电源管理IC是DDR SDRAM存储器的理想选择

与其它存储器技术相比,DDRSDRAM具有出众性能、很低的功耗以及更具竞争力的成本。可与以前的SDRAM技术相比,DDRx存储器需要一个更复杂的电源管理新架构。本文探讨了DDR电源管理架构的理想选择。

与其它存储器技术相比,DDRSDRAM具有出众性能、很低的功耗以及更具竞争力的成本,目前已普遍应用在桌面电脑和便携计算应用中。

最初,DDR的数据传输速率只有266MBps,而普通SDRAM的速率只有133MBps。随后,DDR数据传输速率增加400MBps。第二代DDR,即2004年初登场的DDR2,将数据速率从400MBps提高到667MBps,而同时还进一步降低了功耗。

目前,第一代DDR仍在存储器市场中占主流地位,但DDR2正在快速地抢得市场份额,并可望在2005年底两者的市场份额将出现转折点。但不论DDR内存多么受欢迎,与以前的SDRAM技术相比,DDRx存储器需要一个更复杂的电源管理新架构。

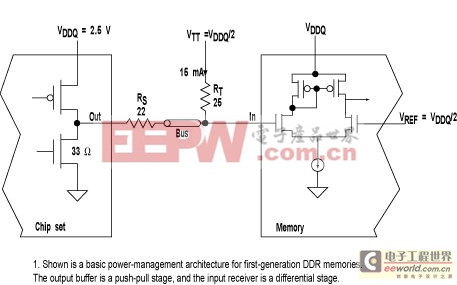

DDR电源管理架构图1给出了第一代DDR存储器的基本电源管理架构。在DDR存储器中,输出缓冲器是推挽级,而输入吸收器是差动级,这就需要一个参考电压的偏置中点VREF,从而需要一个能提供和吸收电流的输入电压终端。

最新的特性(提供和吸收电流)使DDRVTT终端与PC主板上的其它终端有所不同。在连接CPU和存储器通道集线器(MCH)的前端系统总线中,它们的差别特别值得注意。由于该终端接到正电压上,因而只要求具有吸收电流的能力,所以DDRVTT终端不能够重复利用或适应以前的VTT终端,而是需要新的电源设计。

第一代DDR存储器的逻辑门由2。5V电源供电。在芯片组任何输出缓冲器与存储器模块相应的输入吸收器之间,一般可以找到需要正确端接电阻RT和RS的一条走线或者走线分支(参见图1)。当考虑所有阻抗(包括输出缓冲器的阻抗)时,每个端接线都可吸收或提供±16。2mA的电流。对于发送器和吸收器之间走线比较长的系统,必须在走线两端端接电阻,以使电流增加一倍。

DDR逻辑所要求的2。5VVDDQ的误差为+200mV。为保持噪声容限,VTT必须以±3%的精度跟随VDDQ变化,且必须等于VDDQ/2,大约为1。25V,精度±3%。最终VREF必须与VTT相差+40mV。这些跟随要求以及VTT必须能够提供和吸收电流的要求,给DDR存储器的供电带来了独特挑战。

最坏情况下的电流消耗

VTT终端:假设128MB存储器系统有128位总线、8个数据选通、8个屏蔽位、8个VCC位、40条地址线(两组20条地址线),则共有192个信号/电源线。每条线消耗电流16。2mA,则最大电流消耗为192×16。2mA=3。11A。

VDDQ电压峰值:VTT吸收电流时VDDQ供应电流,因此VDDQ的电流是单向的,因此其最大电流就等于VTT的最大电流3。11A。。

平均功耗:一个128MB存储器模块一般由8个128Mb的器件组成,平均消耗990mW功率,除去VTT终端消耗的功率,IDDQ从VDDQ抽取的平均电流为IDDQ=PDDQ/VDDQ=990mW/2。5V=0。396A。

同样,终端电阻消耗的平均功率PTT为660mW,从VTT抽取的电流ITT为ITT=PTT/VTT=660mW/1。25V=0。528A。

评论