基于FPGA平台的工业电机最大效率实现

RIO架构目前已被用于多款系统中,如EUROelectronics等公司的系统。借助该架构,从产品原型设计到最终机械设备完成,EUROelectronics只用了3个月的时间。

缩短机械设计时间

无刷DC和永磁同步AC电机(PMSM)二者通常组成无刷DC电机(BLDC),其集成式控制非常复杂,是一个挑战。许多机械制造商都缺乏构建嵌入式控制器方面的软硬件设计经验,难以让嵌入式控制器在各种类型的模拟和数字传感器上实时执行闭环控制。

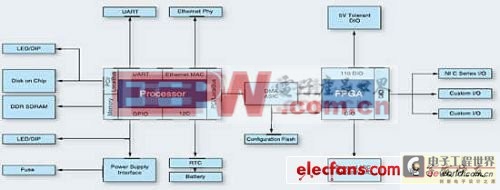

为了缩短嵌入式机械制造商的最终设计时间,本文介绍的方案在CompactRIO产品中集成了某种形式的RIO架构。这种基于FPGA的配置包括基于Virtex-5 LX85到Spartan-3的系统,以及基于Virtex-II 1M门的背板,配合基于PowerPC 603e的处理器,能够满足多种频率和性能需求,如图1所示。

图1 在CompactRIO产品中集成了某种形式的RIO架构

在RIO框架中集成配置软件实用程序和动态I/O重构功能可节约设置时间,而且终端应用编程人员和数字设计工程师还能重复使用有关资源。配置软件能自动检测系统中安装的定制硬件。I/O外设的集成式诊断测试可确保I/O器件正常工作。

如果不安装I/O电路,驱动程序软件及相关API不能适当执行或返回具体器件的故障,就会出现问题。为解决上述问题,软件开发人员通常会创建模拟子例程,临时替代应用中的I/O电路代码。这种方法难以立即开始应用开发,而且几乎不能调试代码。RIO中间件驱动程序架构包括相关功能,可将模拟代码直接集成到函数驱动程序中,从而简化代码的重复使用与故障调试。

图2 嵌入式中间件软件设计分级图

图2所示为嵌入式中间件软件设计分级图。这种中间件驱动程序和系统服务在成千上万种已经部署的机械设计应用中都证实了自己的功能。并行和多线程安全型嵌入式中间件驱动程序是RIO的有机组成部分。机械制造商可同时从多个线程调用多线程安全型和可再入函数,同时还能确保正常工作,避免阻塞现象,这对并行代码的编写和性能优化都是非常重要的特性。不具备可再入执行功能的驱动程序会影响性能,更糟的是还会导致崩溃。代码必须等其他线程使用完每个函数后才能访问函数。可再入性可避免代码中任何不必要的依赖性。

BLDC和PMSM的定子缠绕方式有别。BLDC的定子旋转时其缠绕方式可生成梯形反电势电压,而PMSM的电压则为正弦曲线。

BLDC的成本高于AC电感电机,但在用高级算法控制情况下其节能性和性能更高。此外,BLDC还具有较高的可扩展性,能满足极高功率和极高速应用的需求。

评论