基于MPC8260处理器的PPMC系统

鉴于以往嵌入式系统缺点,结合高端嵌入式系统的新要求,VSO(VITA Standard Organization)在IEEE制定的P1386.1标准上,提出了PPMC(Processor PCI Mezzanine Card)概念,目的是确保各个厂家不同的CPU对外拥有相同的PCI接口。它对PPMC插座接口的电气特性、引脚信号、PPMC和其Carrier Board的连接以及PPMC的尺寸作了严格规定,力求在高端嵌入式系统中促进系统模块化。

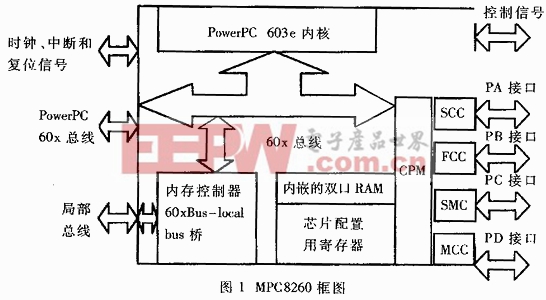

鉴于以往嵌入式系统缺点,结合高端嵌入式系统的新要求,VSO(VITA Standard Organization)在IEEE制定的P1386.1标准上,提出了PPMC(Processor PCI Mezzanine Card)概念,目的是确保各个厂家不同的CPU对外拥有相同的PCI接口。它对PPMC插座接口的电气特性、引脚信号、PPMC和其Carrier Board的连接以及PPMC的尺寸作了严格规定,力求在高端嵌入式系统中促进系统模块化。 本文介绍了一种以MPC8260处理器为基础的PPMC实现,构建了一个微型计算机系统。该系统完全符合VSO对PPMC的要求,在嵌入式PCI系统中可以即插即用,并可应用于CpmpactPCI系统中。该PPMC系统处理能力优异(内核最高处理能力可达350MIPS),带有多种通讯协议处理接口,符合多种RTOS(pSOS、VxWorks等)对其运行平台的要求,且在硬件上满足RTOS的两种主要调试手段(串口调试和以太网调试),应用开发相当容易。此外,该系统具备高度的现场可扩展性,通过简单的软件配置,可以方便地提供多种通讯协议的前端处理接口。 1 MPC8260处理器简介 PowerPC芯片是由Motorola、Apple、IBM三家公司联合研制的一种RISC处理器,具备超强处理能力,广泛出现在处理器的高端应用场合。Motorola公司考虑到电信和网络市场的特点,在PowerPC芯片的基础上,推出了专为嵌入式系统设计的MPC8260芯片。该芯片内嵌一个PowerPC 603e内核,有着与PowerPC完全相同的指令集合,并且集成了若干通讯协议处理单元,是目前最先进的专为电信和网络市场设计的微处理器。MPC8260芯片的功能框图以及外部引脚示意如图1所示。

本文介绍了一种以MPC8260处理器为基础的PPMC实现,构建了一个微型计算机系统。该系统完全符合VSO对PPMC的要求,在嵌入式PCI系统中可以即插即用,并可应用于CpmpactPCI系统中。该PPMC系统处理能力优异(内核最高处理能力可达350MIPS),带有多种通讯协议处理接口,符合多种RTOS(pSOS、VxWorks等)对其运行平台的要求,且在硬件上满足RTOS的两种主要调试手段(串口调试和以太网调试),应用开发相当容易。此外,该系统具备高度的现场可扩展性,通过简单的软件配置,可以方便地提供多种通讯协议的前端处理接口。 1 MPC8260处理器简介 PowerPC芯片是由Motorola、Apple、IBM三家公司联合研制的一种RISC处理器,具备超强处理能力,广泛出现在处理器的高端应用场合。Motorola公司考虑到电信和网络市场的特点,在PowerPC芯片的基础上,推出了专为嵌入式系统设计的MPC8260芯片。该芯片内嵌一个PowerPC 603e内核,有着与PowerPC完全相同的指令集合,并且集成了若干通讯协议处理单元,是目前最先进的专为电信和网络市场设计的微处理器。MPC8260芯片的功能框图以及外部引脚示意如图1所示。 由图1可知,MPC8260主要包括三部分。第一部分是高性能的PowerPC 603e内核,体系结构与其它PowerPC芯片相同,运行频率为100~266MHz。 第二部分是总线接口。在兼容MPC860局部总线的基础上,MPC8260另外提供了高性能的PowerPC 60x总线。该总线是一种标准总线,32位地址线,64位数据线,支持多PowerPC芯片互连。可以通过简单的寄存器配置来决定采用哪种总线。本系统选用60x总线,总线工作频率为66MHz。 第三部分是通信处理模块CPM(Communication Processor Module)。该模块是MPC8260相对其它处理器的最大优势所在,除了带有一个增强的32位RISC专用通信控制器外,模块中还内嵌有3个FCC(Fast Communication Controller)、2个MCC(Multiple Channel Controller)、4个SCC(Serial Channel Controller)、2个SMC(Serial Managements Controller)。所有这些控制器都可以用来处理特定的通讯协议。 MPC8260芯片中包括四组通用I/O端口:PA、PB、PC、PD。这四组通用I/O端口与CPM有着密切关系。PA、PB、PC包含32个管脚,PD包含28个管脚。各组端口中的每一个管脚都可以通过软件配置外接不同的信号。例如,管脚PC[2]可以配置为外接以太网MII(Media-Independent Interface)接口的CD信号,也可配置为外接ATM(Asynchronous transfer mode异步传输模式)UTOPIA接口的TXD信号,还可配置为一般的IO信号。

由图1可知,MPC8260主要包括三部分。第一部分是高性能的PowerPC 603e内核,体系结构与其它PowerPC芯片相同,运行频率为100~266MHz。 第二部分是总线接口。在兼容MPC860局部总线的基础上,MPC8260另外提供了高性能的PowerPC 60x总线。该总线是一种标准总线,32位地址线,64位数据线,支持多PowerPC芯片互连。可以通过简单的寄存器配置来决定采用哪种总线。本系统选用60x总线,总线工作频率为66MHz。 第三部分是通信处理模块CPM(Communication Processor Module)。该模块是MPC8260相对其它处理器的最大优势所在,除了带有一个增强的32位RISC专用通信控制器外,模块中还内嵌有3个FCC(Fast Communication Controller)、2个MCC(Multiple Channel Controller)、4个SCC(Serial Channel Controller)、2个SMC(Serial Managements Controller)。所有这些控制器都可以用来处理特定的通讯协议。 MPC8260芯片中包括四组通用I/O端口:PA、PB、PC、PD。这四组通用I/O端口与CPM有着密切关系。PA、PB、PC包含32个管脚,PD包含28个管脚。各组端口中的每一个管脚都可以通过软件配置外接不同的信号。例如,管脚PC[2]可以配置为外接以太网MII(Media-Independent Interface)接口的CD信号,也可配置为外接ATM(Asynchronous transfer mode异步传输模式)UTOPIA接口的TXD信号,还可配置为一般的IO信号。 PA、PB、PC、PD四组通用I/O端口的灵活配置,结合内部SCC、FCC、SMC的可配置性,使得CPM的功能得以倍增。CPM模块利用这四组通用I/O端口完成的通讯协议接口主要如下: (1)2个ATM UTOPIA接口,可用来实现2个155Mbps ATM SAR。 (2)8个 TDM(时分复用线)接口,其中2个TDM接口可以无缝连接到T3/E3,最高可以提供256个全双工64kbps HDLC通道。 (3)3个MII接口,可用来实现3个10/100Mbps自适应以太网接口。 (4)4个RS-232串口。 由此可知,MPC82760内嵌了多种通讯处理模块,可以方便地为用户提供一个全新的系统解决方案来建立高端嵌入式系统。

PA、PB、PC、PD四组通用I/O端口的灵活配置,结合内部SCC、FCC、SMC的可配置性,使得CPM的功能得以倍增。CPM模块利用这四组通用I/O端口完成的通讯协议接口主要如下: (1)2个ATM UTOPIA接口,可用来实现2个155Mbps ATM SAR。 (2)8个 TDM(时分复用线)接口,其中2个TDM接口可以无缝连接到T3/E3,最高可以提供256个全双工64kbps HDLC通道。 (3)3个MII接口,可用来实现3个10/100Mbps自适应以太网接口。 (4)4个RS-232串口。 由此可知,MPC82760内嵌了多种通讯处理模块,可以方便地为用户提供一个全新的系统解决方案来建立高端嵌入式系统。 2 基于MPC8260的PPMC系统 图2为基于MPC8260的PPMC系统模块框图。 注:篇幅所限,VSO在IEEE标准上专门为PPMC定义的标准插座没有画出来,而图2中,除了连接到两个RJ45插座的信号外,其它黑色粗体箭头代表的信号都必须连到该插座上去。请参阅VSO相关手册。 各子模块的解释如下: (1)10/100Mbps以太网子模块接口和RS-232串口子模块。两者的实现都利用了MPC8260的通用I/O管脚。以太网子模块还包括外接的以太网PHY和以太网变压器。PHY选用LevelOne公司的970系列芯片。变压器选用Pulse H1081。以太网MII接口管脚分布如表1所示。表1 以太网MII接口管脚分布 MII信号MPC 8260管脚含 义TxD[0:3]RxD[0:3]CRSCOLTX_ENTX_ERRX_ERRX_DVTxCLKRxCLKPort B B[4:7]Port B B[8:11]Port B B[12]Port B B[13]Port B B[14]Port B B[15]Port B B[16]Port B B[17]Port C C[16]Port C C[19]发送数据线接收数据线开始发送发送冲突可以发送发送失败接收到环帧接收到数据发送时钟接收时钟RS-232串口子模块包含一个电平转换器MAX3221。此外,相对一般的9线RS-232接口而言,本系统中无论是数据接收还是发送,MPC8260总是处于准备好的状态。因而RS-232使用5线接口就可以,串口管脚分布如表2所示。表2 串口管脚分布 信 号管 脚含 义TxDRxDCDRTSCTSPort D D[26]Port D D[27]Port D D[28]Port C C[12]Port C C[13]发送数据线接收数据线检测到载波请求发送可以发送(2)时钟和复位子模块为系统提供时钟信号和复位信号。时钟子模块核心部件为高稳定性66MHz石英晶振。该晶振提供系统基准时钟。考虑到晶振直接带负载能力有限,时钟子模块中还包含1个零延时缓冲器。复位子模块核心为MAX706芯片,结合后面提到的EPLD,可为系统各器件提供上电复位、硬复位、软复位等各种复位信号。 (3)Power Span子模块为PPMC系统提供对外PCI接口,PCI总线工作在33MHz。 (4)EPLD子模块。因为需要实现的控制逻辑较多,采用Altera公司的可编程逻辑芯片EPM9510ARC208-10,可以为SDRAM产生时序信号、读取接口配置信号、汇总各个中断信号、汇总复位信号和时钟信号。 (5)SDRAM子模块。选用4片现代公司的HY57V653220CT SDRAM芯片。

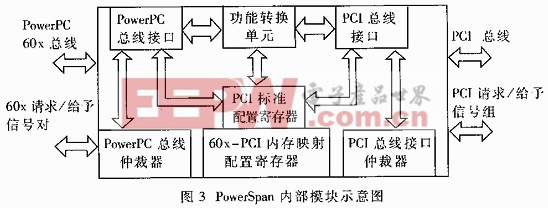

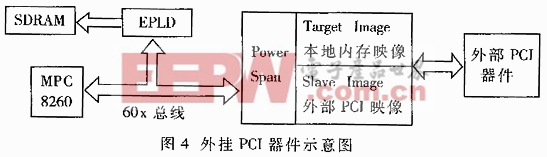

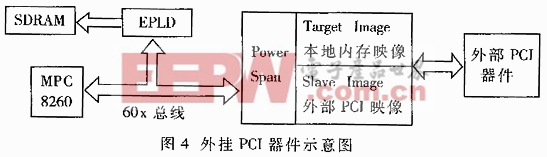

2 基于MPC8260的PPMC系统 图2为基于MPC8260的PPMC系统模块框图。 注:篇幅所限,VSO在IEEE标准上专门为PPMC定义的标准插座没有画出来,而图2中,除了连接到两个RJ45插座的信号外,其它黑色粗体箭头代表的信号都必须连到该插座上去。请参阅VSO相关手册。 各子模块的解释如下: (1)10/100Mbps以太网子模块接口和RS-232串口子模块。两者的实现都利用了MPC8260的通用I/O管脚。以太网子模块还包括外接的以太网PHY和以太网变压器。PHY选用LevelOne公司的970系列芯片。变压器选用Pulse H1081。以太网MII接口管脚分布如表1所示。表1 以太网MII接口管脚分布 MII信号MPC 8260管脚含 义TxD[0:3]RxD[0:3]CRSCOLTX_ENTX_ERRX_ERRX_DVTxCLKRxCLKPort B B[4:7]Port B B[8:11]Port B B[12]Port B B[13]Port B B[14]Port B B[15]Port B B[16]Port B B[17]Port C C[16]Port C C[19]发送数据线接收数据线开始发送发送冲突可以发送发送失败接收到环帧接收到数据发送时钟接收时钟RS-232串口子模块包含一个电平转换器MAX3221。此外,相对一般的9线RS-232接口而言,本系统中无论是数据接收还是发送,MPC8260总是处于准备好的状态。因而RS-232使用5线接口就可以,串口管脚分布如表2所示。表2 串口管脚分布 信 号管 脚含 义TxDRxDCDRTSCTSPort D D[26]Port D D[27]Port D D[28]Port C C[12]Port C C[13]发送数据线接收数据线检测到载波请求发送可以发送(2)时钟和复位子模块为系统提供时钟信号和复位信号。时钟子模块核心部件为高稳定性66MHz石英晶振。该晶振提供系统基准时钟。考虑到晶振直接带负载能力有限,时钟子模块中还包含1个零延时缓冲器。复位子模块核心为MAX706芯片,结合后面提到的EPLD,可为系统各器件提供上电复位、硬复位、软复位等各种复位信号。 (3)Power Span子模块为PPMC系统提供对外PCI接口,PCI总线工作在33MHz。 (4)EPLD子模块。因为需要实现的控制逻辑较多,采用Altera公司的可编程逻辑芯片EPM9510ARC208-10,可以为SDRAM产生时序信号、读取接口配置信号、汇总各个中断信号、汇总复位信号和时钟信号。 (5)SDRAM子模块。选用4片现代公司的HY57V653220CT SDRAM芯片。 3 硬件实现的要点 就硬件实现而言,有几点需要注意: (1)为以太网和串口分配管脚。如果仅仅是配置一个MII接口和一个RS-232接口,有多种实现方案。但必须考虑到系统功能的可扩展性,尽可能多地预留TDM接口和ATM UTOPIA接口。 (2)PCI桥接和总线仲裁 VSO规定,PPMC系统必须带有PCI接口。但MPC8260芯片本身不带PCI接品,因而需要外挂PCI桥接芯片PowerSpan。 PowerSpan是Tundra公司生产的PCI桥接芯片,总线频率范围为25~66MHz,支持PCI2.2规范。PowerSpan内部模块如图3所示。可以与MPC8260、PowerPC 603e/740/750等PowerPC系列芯片无缝接合。电气特性符合VSO PPMC标准。 实际应用时,PowerPC 60x总线和PCI总线上都挂二多个器件,每个器件都可能需要获取总线的控制权以便发起总线操作,因此总线控制权的仲裁十分重要。 就PCI总线布言,采用PowerSpan内嵌的PCI总线仲截器件为整个PCI总线的仲裁器,应该将PPMC卡标准插座上各组GNT、REQ信号连到PowerSpan相应管脚处。PowerPC 60x总线的情况有点不同,MPC8260芯片和PowerSpan芯片都自带60z总线仲裁器。从系统的扩展性考虑,采用MPC8260芯片自带 60x总线仲裁器。因而PowerSpan的PB_BR[1]、PB_BG[1]、PB_DBG[1]等信号必须连到MPC8260芯片对应处。 (3)片选信号和内存分配 MPC8260 60x总线包含32位地址线,可以访问高达4G字节的内存。MPC8260内嵌有一个内存分类控制器,该分类控制器提供了多个片选信号。在本系统中,地址空间分类6类子空间,如表3所示。表3 内存分配表 60x内存类型和片选信号地址范围含 义PowerSpan Register SpaceMPC8260 Register SpaceBootrom(CS0) D[0:7]Flash (CS1) D[0:15]SDRAM (CS2) D[0:63]PCI Image n(n=1...8)0X30000000~0X30000FFF0XF0000000~0XF001FFFF0XFE000000~0XE0FFFFFF0XE0000000~0XE0FFFFFF0X00000000~0X03FFFFFFMaximum Block Size=2GBMinimum Block Size=64KB4KB128KB1024KB16MB64MB以64位数据线方式访问PowerSpan内部寄存器空间,以及通过PowerSpan映射的PCI空间。访问二者时,不需要片选信号。PowerSpan自行判断60x地址是否指向自身,决定是否回应。 CS0代表的Bootrom空间有着特殊含义。根据MPC8260的规定,复位时,MPC8260自动读取Bootrom中的指令运行启动程序。Bootrom空间是唯一不需要额外配置、MPC8260就可以读取的子模块。 相关配置寄存器包括:MPC8260中的BRn、Orn(n=0,1,2)寄存器、IMMR寄存器以及PowerSpan相关设置中的Slave Image和Iarget Image。 4 硬件实现的难点 保证外部PCI器件(没有位于PPMC上)通过PowerSpan高速访问PPMC系统所带SDRAM内存,是设计上一大难点。图4是外挂PCI器件时,内存存取示意图。 图4从左向右为Slave Image方向。MPC8260通过设置PowerSpan的相关Slave Image寄存器,将外部PCI空间映射到60x空间后,PowerSpan即成为透明桥。MPC8260以60x总线地址访问外部PCI器件,PowerSpan会自动进行有关转换工作。 图4从右向左为Target Image方向。此时外部PCI器件要访问PPMC上的SDRAM。通过设置PowerSpan Target Image中相关寄存器,将60x总线地址空间的一部分(也就是PPMC上SDRAM对应的60x地址空间中的一段)映射到外部PCI空间上,外部PCI器件就可能以PCI总线地址访问PPMC所带SDRAM,PowerSpan自动进行有关转换工作。

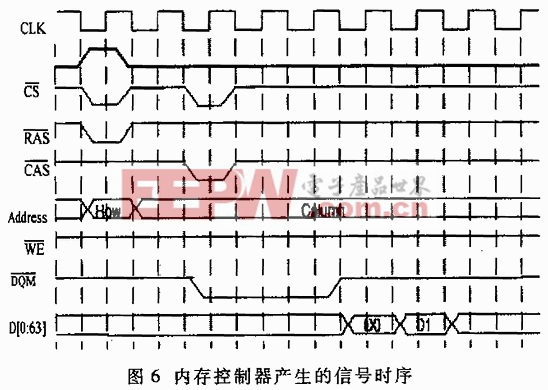

3 硬件实现的要点 就硬件实现而言,有几点需要注意: (1)为以太网和串口分配管脚。如果仅仅是配置一个MII接口和一个RS-232接口,有多种实现方案。但必须考虑到系统功能的可扩展性,尽可能多地预留TDM接口和ATM UTOPIA接口。 (2)PCI桥接和总线仲裁 VSO规定,PPMC系统必须带有PCI接口。但MPC8260芯片本身不带PCI接品,因而需要外挂PCI桥接芯片PowerSpan。 PowerSpan是Tundra公司生产的PCI桥接芯片,总线频率范围为25~66MHz,支持PCI2.2规范。PowerSpan内部模块如图3所示。可以与MPC8260、PowerPC 603e/740/750等PowerPC系列芯片无缝接合。电气特性符合VSO PPMC标准。 实际应用时,PowerPC 60x总线和PCI总线上都挂二多个器件,每个器件都可能需要获取总线的控制权以便发起总线操作,因此总线控制权的仲裁十分重要。 就PCI总线布言,采用PowerSpan内嵌的PCI总线仲截器件为整个PCI总线的仲裁器,应该将PPMC卡标准插座上各组GNT、REQ信号连到PowerSpan相应管脚处。PowerPC 60x总线的情况有点不同,MPC8260芯片和PowerSpan芯片都自带60z总线仲裁器。从系统的扩展性考虑,采用MPC8260芯片自带 60x总线仲裁器。因而PowerSpan的PB_BR[1]、PB_BG[1]、PB_DBG[1]等信号必须连到MPC8260芯片对应处。 (3)片选信号和内存分配 MPC8260 60x总线包含32位地址线,可以访问高达4G字节的内存。MPC8260内嵌有一个内存分类控制器,该分类控制器提供了多个片选信号。在本系统中,地址空间分类6类子空间,如表3所示。表3 内存分配表 60x内存类型和片选信号地址范围含 义PowerSpan Register SpaceMPC8260 Register SpaceBootrom(CS0) D[0:7]Flash (CS1) D[0:15]SDRAM (CS2) D[0:63]PCI Image n(n=1...8)0X30000000~0X30000FFF0XF0000000~0XF001FFFF0XFE000000~0XE0FFFFFF0XE0000000~0XE0FFFFFF0X00000000~0X03FFFFFFMaximum Block Size=2GBMinimum Block Size=64KB4KB128KB1024KB16MB64MB以64位数据线方式访问PowerSpan内部寄存器空间,以及通过PowerSpan映射的PCI空间。访问二者时,不需要片选信号。PowerSpan自行判断60x地址是否指向自身,决定是否回应。 CS0代表的Bootrom空间有着特殊含义。根据MPC8260的规定,复位时,MPC8260自动读取Bootrom中的指令运行启动程序。Bootrom空间是唯一不需要额外配置、MPC8260就可以读取的子模块。 相关配置寄存器包括:MPC8260中的BRn、Orn(n=0,1,2)寄存器、IMMR寄存器以及PowerSpan相关设置中的Slave Image和Iarget Image。 4 硬件实现的难点 保证外部PCI器件(没有位于PPMC上)通过PowerSpan高速访问PPMC系统所带SDRAM内存,是设计上一大难点。图4是外挂PCI器件时,内存存取示意图。 图4从左向右为Slave Image方向。MPC8260通过设置PowerSpan的相关Slave Image寄存器,将外部PCI空间映射到60x空间后,PowerSpan即成为透明桥。MPC8260以60x总线地址访问外部PCI器件,PowerSpan会自动进行有关转换工作。 图4从右向左为Target Image方向。此时外部PCI器件要访问PPMC上的SDRAM。通过设置PowerSpan Target Image中相关寄存器,将60x总线地址空间的一部分(也就是PPMC上SDRAM对应的60x地址空间中的一段)映射到外部PCI空间上,外部PCI器件就可能以PCI总线地址访问PPMC所带SDRAM,PowerSpan自动进行有关转换工作。 由此可知,MPC8260和PowerSpan都可成为60x总线的Master,都会访问SDRAM。从效率考虑,必须允许二者可以猝发存取SDRAM。 与读写ROM不同,读写SDRAM的时序关系很复杂,要考虑到多种因素,如SDRAM的刷新问题。遗憾的是,就60x总线信号的时序而言,无法直接与SDRAM连接。特别是对PowerSpan,没有内嵌任何内存控制器,即使MPC8260提供了一些辅助控制信号,也无法直接连接,因而外部须提供逻辑转换。就本PPMC系统而言,必须在EPLD内实现一个SDRAM控制器,这就是图4中引入EPLD的原因。 该控制器采用Verilog HDL实现,可为SDRAM提供一系列符合时序的控制信号。控制器就其本质而言,是一个状态机。随着外部60x总线输入信号的变化,该状态机在一系列不同状态之间转换,同时输出SDRAM控制信号,以及60x总线的回应信号。例如就读数据而言,隐去刷新等状态,状态机如图5所示。 图6是在触发方式下,2-beat读取数据时,内存控制器产生的控制信号。此时,Page Closed、CAS latency为3个时钟周期,Activate to Read interval为2个时钟周期。RAS为控制器输出的行地址选择信号,CAS为列地址选择信号,DQM为字节选择信号。

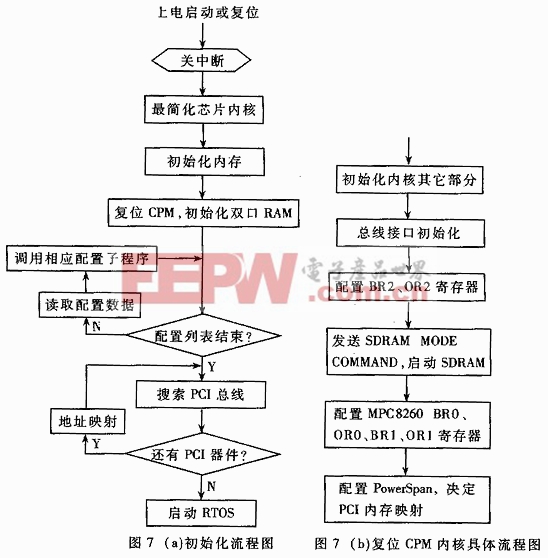

由此可知,MPC8260和PowerSpan都可成为60x总线的Master,都会访问SDRAM。从效率考虑,必须允许二者可以猝发存取SDRAM。 与读写ROM不同,读写SDRAM的时序关系很复杂,要考虑到多种因素,如SDRAM的刷新问题。遗憾的是,就60x总线信号的时序而言,无法直接与SDRAM连接。特别是对PowerSpan,没有内嵌任何内存控制器,即使MPC8260提供了一些辅助控制信号,也无法直接连接,因而外部须提供逻辑转换。就本PPMC系统而言,必须在EPLD内实现一个SDRAM控制器,这就是图4中引入EPLD的原因。 该控制器采用Verilog HDL实现,可为SDRAM提供一系列符合时序的控制信号。控制器就其本质而言,是一个状态机。随着外部60x总线输入信号的变化,该状态机在一系列不同状态之间转换,同时输出SDRAM控制信号,以及60x总线的回应信号。例如就读数据而言,隐去刷新等状态,状态机如图5所示。 图6是在触发方式下,2-beat读取数据时,内存控制器产生的控制信号。此时,Page Closed、CAS latency为3个时钟周期,Activate to Read interval为2个时钟周期。RAS为控制器输出的行地址选择信号,CAS为列地址选择信号,DQM为字节选择信号。 5 初始化软件流程 本PPMC的初始化流程有着与RTOS中标准BSP(Board Support Package)要求相同的次序,程序流程如图7所示。 系统初始启动时,MPC8260自动读取Bootrom中的指令。Bootrom中最初一段程序采用PowerPC汇编语言编写,该部分程序必须对系统进行基本的初始化工作。其中最重要的是初始化那些与SDRAM有关的寄存器,以便可以尽快使用SDRAM,从而在其后可以使用C语言编写的程序进行后继初始化工作。 本文构建了一个符合VSO和IEEE标准的PPMC系统,可以为嵌入式系统(特别是通讯用嵌入式系统)提供一个功能强大、高度模块化、具体高度可扩展性的微型计算机系统。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

5 初始化软件流程 本PPMC的初始化流程有着与RTOS中标准BSP(Board Support Package)要求相同的次序,程序流程如图7所示。 系统初始启动时,MPC8260自动读取Bootrom中的指令。Bootrom中最初一段程序采用PowerPC汇编语言编写,该部分程序必须对系统进行基本的初始化工作。其中最重要的是初始化那些与SDRAM有关的寄存器,以便可以尽快使用SDRAM,从而在其后可以使用C语言编写的程序进行后继初始化工作。 本文构建了一个符合VSO和IEEE标准的PPMC系统,可以为嵌入式系统(特别是通讯用嵌入式系统)提供一个功能强大、高度模块化、具体高度可扩展性的微型计算机系统。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论