工业以及汽车应用中多种串行总线特性及比较

由于在消费类电子产品、计算机外设、汽车和工业应用中增加了嵌入式功能,对低成本、高速和高可靠通信介质的要求也不断增长以满足这些应用,其结果是越来越多的处理器和控制器用不同类型的总线集成在一起,实现与PC软件、开发系统(如仿真器)或网络中的其它设备进行通信。目前流行的通信一般采用串行或并行模式,而串行模式应用更广泛。

微处理器中常用的集成串行总线是通用异步接收器传输总线、串行通信接口、同步外设接口(SPI)、内部集成电路(I2C)和通用串行总线,以及车用串行总线,包括控制器区域网(CAN)和本地互连网(LIN)。这些总线在速度、物理接口要求和通信方法学上都有所不同。本文将对嵌入式系统设计的串行总线、驱动器和物理接口这些要求提供一个总体介绍,为选择最优总线提供指导并给出一个比较图表(表1)。为了说明方便起见,本文的阐述是基于微处理器的设计。

|

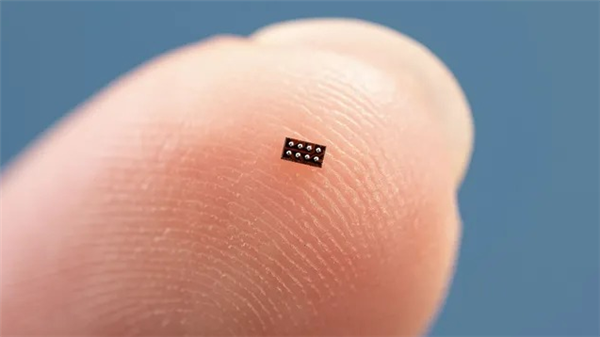

串行相比于并行的主要优点是要求的线数较少。例如,用在汽车工业中的LIN串行总线只需要一根线来与从属器件进行通信,Dallas公司的1-Wire总线只使用一根线来输送信号和电源。较少的线意味着所需要的控制器引脚较少。集成在一个微控制器中的并行总线一般需要8条或更多的线,线数的多少取决于设计中地址和数据的宽度,所以集成一个并行总线的芯片至少需要8个引脚来与外部器件接口,这增加了芯片的总体尺寸。相反地,使用串行总线可以将同样的芯片集成在一个较小的封装中。

另外,在PCB板设计中并行总线需要更多的线来与其它外设接口,使PCB板面积更大、更复杂,从而增加了硬件成本。此外,工程师还可以很容易地将一个新器件加到一个串行网络中去,而且不会影响网络中的其它器件。例如,可以很容易地去掉总线上旧器件并用新的来替代。

串行总线的故障自诊断和调试也非常简单,可以很容易地跟踪网络中一个有故障的器件并用新器件替换而不会干扰网络。但另一方面,并行总线比串行速度快。例如,Rambus公司的“Redwood”总线速度可高达6.4GHz,而最高的串行速度不会超过几个兆赫。

在工业和汽车应用中常用的串行协议

1. UART

UART是一种通用串行数据总线,用于异步通信。该总线双向通信,可以实现全双工传输和接收。在嵌入式设计中,UART用来与PC进行通信,包括与监控调试器和其它器件,如EEPROM通信。

a. UART通信

UART首先将接收到的并行数据转换成串行数据来传输。消息帧从一个低位起始位开始,后面是7个或8个数据位,一个可用的奇偶位和一个或几个高位停止位。接收器发现开始位时它就知道数据准备发送,并尝试与发送器时钟频率同步。如果选择了奇偶,UART就在数据位后面加上奇偶位。奇偶位可用来帮助错误校验。

在接收过程中,UART从消息帧中去掉起始位和结束位,对进来的字节进行奇偶校验,并将数据字节从串行转换成并行。UART也产生额外的信号来指示发送和接收的状态。例如,如果产生一个奇偶错误,UART就置位奇偶标志。

b. 数据方向和通信速度

数据传输可以首先从最低有效位(LSB)开始。然而,有些UART允许灵活选择先发送最低有效位或最高有效位(MSB)。

微控制器中的UART传送数据的速度范围为每秒几百位到1.5Mb。例如,嵌入在ElanSC520微控制器中的高速UART通信的速度可以高达1.1152Mbps。UART波特率还受发送和接收线对距离(线长度)的影响。

目前,市场上有只支持异步通信和同时支持异步与同步通信的两种硬件可用于UART。前者就是UART名字本身的含义,在摩托罗拉微控制器中被称为串行通信接口(SCI);Microchip微控制器中的通用同步异步收发器(USART)和在富士通微控制器中的UART是后者的两个典型例子。

c. 计算机中的UART

UART是计算机中串行通信端口的关键部分。在计算机中,UART相连于产生兼容RS232规范信号的电路。RS232标准定义逻辑“1”信号相对于地为3到25伏,而逻辑“0”相对于地为-3到-25伏。所以,当一个微控制器中的UART相连于PC时,它需要一个RS232驱动器来转换电平。

2. 同步外设接口

同步外设接口(SPI)是由摩托罗拉公司开发的全双工同步串行总线,该总线大量用在与EEPROM、ADC、FRAM和显示驱动器之类的慢速外设器件通信。

a. SPI通信

该总线通信基于主-从配置。它有以下4个信号:

- MOSI:主出/从入

- MISO:主入/从出

- SCK:串行时钟

- SS:从属选择

芯片上“从属选择”(slave-select)的引脚数决定了可连到总线上的器件数量。

在SPI传输中,数据是同步进行发送和接收的。数据传输的时钟基于来自主处理器的时钟脉冲,摩托罗拉没有定义任何通用SPI的时钟规范。然而,最常用的时钟设置基于时钟极性(CPOL)和时钟相位(CPHA)两个参数,CPOL定义SPI串行时钟的活动状态,而CPHA定义相对于SO-数据位的时钟相位。CPOL和CPHA的设置决定了数据取样的时钟沿。

评论