以太网控制器ENC28J60及其接口技术

引言

ENC28J60是Microchip Technology(美国微芯科技公司)近期推出的28引脚独立以太网控制器。

在此之前,嵌入式系统开发可选的独立以太网控制器都是为个人计算机系统设计的,如RTL8019、AX88796L、DM9008、CS8900A、LAN91C111等。这些器件不仅结构复杂,体积庞大,且比较昂贵。目前市场上大部分以太网控制器的封装均超过80引脚,而符合IEEE 802.3协议的ENC28J60只有28引脚,既能提供相应的功能,又可以大大简化相关设计,减小空间。

1 结构和功能

采用业界标准串行外设接口(SPI)的以太网控制器ENC28J60具有以下主要特征:

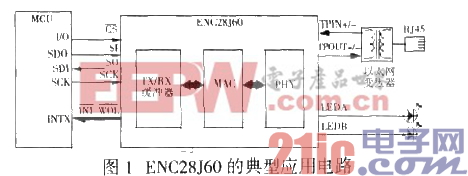

◆ 符合IEEE 802.3协议。内置10 Mbps以太网物理层器件(PHY)及媒体访问控制器(MAC),可按业界标准的以太网协议可靠地收发信息包数据。

◆ 具有可编程过滤功能。特殊的过滤器,包括Microchip的可编程模式匹配过滤器,可自动评价、接收或拒收Magic PACket,单播(UNIcast)、多播(Multicast)或广播(Broadcast)信息包,以减轻主控单片机的处理负荷。

◆ 10 Mbps SPI接口。业界标准的串行通信端口,使得低至18引脚的8位单片机也具有网络连接功能。

◆ 可编程8 KB双端口SRAM缓冲器。以高效的方式进行信息包的存储、检索和修改,以减轻主控单片机的内存负荷。该缓冲存储器提供了灵活可靠的数据管理机制。

2 硬件设计

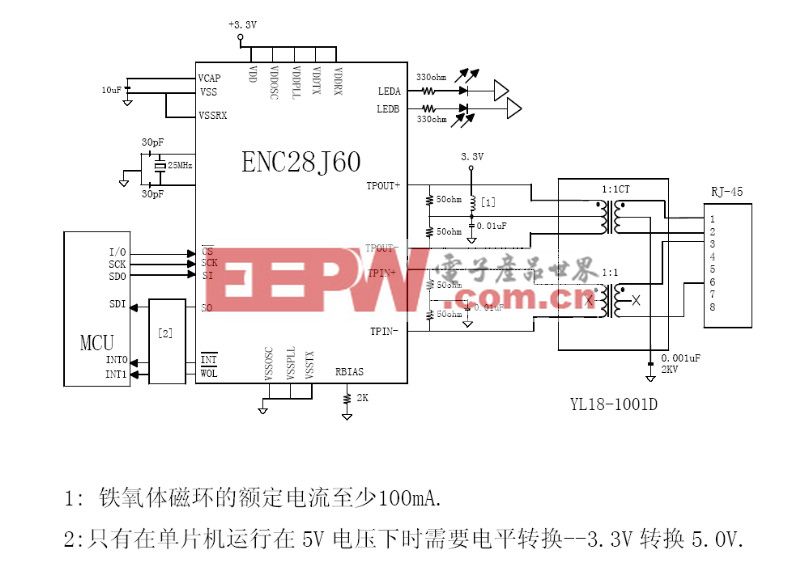

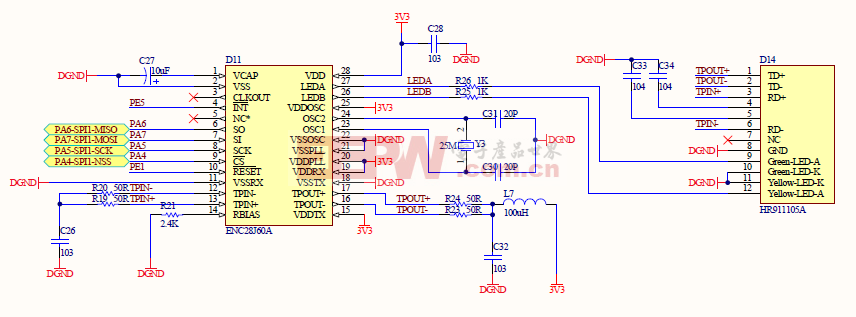

ENC28J60的硬件设计需要注意复位电路,时钟振荡器,振荡器启动定时器,时钟输出引脚,变压器、终端和其他外部器件,输入/输出电平等几个方面。(图1可供参考)

2.1 复位电路

ENC28J60有上电复位(Power-on Reset)功能,RESET引脚上的低电平使ENC28J60进入复位模式;RESET引脚内部有弱上拉电阻。ENC28J60的硬件连接如图1所示。

2.2 时钟振荡器

ENC28J60需要一个25 MHz的晶振,接在OSC1和OSC2脚上;也可由外部时钟信号来驱动。此时3.3 V的外部时钟接在OSC1脚上,OSC2断开或者通过一个电阻接地来降低系统噪声。

2.3 振荡器启动定时器

ENC28J60内部有一个振荡器启动时钟OST(Oscillator Startup Timer),上电7 500个时钟周期(300 μs),OST期满后内部的PHY方能正常工作。这时不能发送或者接收报文。上位机可通过检测ENC28J60内部ESTAT寄存器中的CLKRDY位的状态来决定是否可设置发送或接收报文。

需要注意的是,当ENC28J60上电复位或者从PowerDown模式下唤醒时,必须检测ESTAT寄存器中的CLKRDY是否置位。只有CLKRDY置位后才能发送、接收报文,访问相关寄存器。

评论