通过架构改进提高微控制器处理效率

微控制器要想处理实时I/O和外设的高数据速率和频率,便必须拥有更高的处理效率。但这个效率不能通过提高时钟频率来获得,而是要通过微控制器架构的内部改进来实现。

卸载CPU任务还有很多方法

集成式协处理器在嵌入式微控制器中已获得相当广泛的应用,其中比较常见的协处理器是加密和TCP/IP卸载引擎。协处理器可高效卸载整个任务,或帮助执行复杂算法中的密集计算部分。例如,一个加密引擎可以把CPU上的AES计算任务从每次运算数千个周期缩减为数百个周期,而一个TCP/IP卸载引擎可以极小的CPU运行支出来终止一个以太网连。

DMA控制器通过执行数据访问(如在后台执行外设寄存器到内部或外部SRAM的数据访问),从CPU卸载数据移动管理任务。DMA(Direct Memory Access,直接内存存取) 是所有现代电脑的重要特色,他允许不同速度的硬件装置来沟通,而不需要依于 CPU 的大量 中断 负载。否则,CPU 需要从 来源 把每一片段的资料复制到 暂存器,然后把他们再次写回到新的地方。在这个时间中,CPU 对于其他的工作来说就无法使用。 DMA 传输将数据从一个地址空间复制到另外一个地址空间。当 CPU 初始化这个传输动作,传输动作本身是由 DMA 控制器 来实行和完成。典型的例子就是移动一个外部内存的区块到芯片内部更快的内存区。像是这样的操作并没有让处理器工作拖延,反而可以被重新排程去处理其他的工作。DMA 传输对于高效能 嵌入式系统 算法和网络是很重要的。在实现DMA传输时,是由DMA控制器直接掌管总线,因此,存在着一个总线控制权转移问题。即DMA传输前,CPU要把总线控制权交给DMA控制器,而在结束DMA传输后,DMA控制器应立即把总线控制权再交回给CPU。另外,DMA控制器还能够承担通信外设管理的大部分工作(见表1)。

表1 DMA控制器能够承担通信外设管理的大部分工作

利用DMA控制器所节省的周期数可以十分可观:许多嵌入式开发人员都已发现自己无法以有限的微控制器资源来满足应用的需求,直到认识了DMA,才突然明白原来还有大量额外的周期可用,数目有时甚至多达整个系统的30%到50%左右。

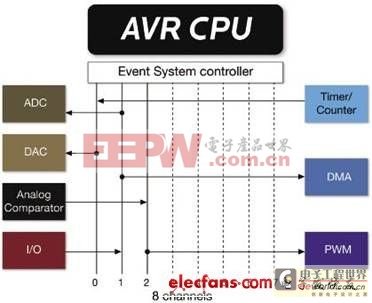

熟知事件系统(event system)的开发人员就更少了。事件系统与DMA制器协同工作,可进一步减少CPU周期的负担,并降低总体功耗。事件系统是一条总线,能够将从微控制器上的一个外设发出的内部信号连接到另一个外设。当有事件在外设上发生时,它就可以在一个双周期的延时内触发其它外设采取行动。

更确切地说,事件系统利用一个连接了CPU、数据总线和DMA控制器的专用网络在整个微控制器上进行信号路由(见图1)。在正常情况下,外设必须中断CPU来激活某个行动,包括读取外设本身。而事件系统通过直接在外设之间发送相关事件,便可有效地使CPU摆脱这些中断所带来的负担。CPU是一台计算机的运算核心和控制核心。CPU、内部存储器和输入/输出设备是电子计算机三大核心部件。电脑中所有操作都由CPU负责读取指令,对指令译码并执行指令的核心部件。其功能主要是解释计算机指令以及处理计算机软件中的数据。所谓的计算机的可编程性主要是指对CPU的编程。 CPU由运算器、控制器和寄存器及实现它们之间联系的数据、控制及状态的总线构成。差不多所有的CPU的运作原理可分为四个阶段:提取(Fetch)、解码(Decode)、执行(Execute)和写回(Writeback)。

图1 一个事件系统

灵活的卸载

DMA和事件系统配合工作,就可让开发人员卸载整个任务,这与协处理器的作用很类似,但两者间的关键区别是协处理器不是可编程的。协处理器采用硬件来执行一个已详细定义的任务,有时甚至是可配置的;而DMA控制器配合事件系统的可编程性使其适用于从最简单的到极复杂的各类任务。在采用DMA和事件系统的情况下,DMA负责管理整个微处理器架构上的数据传输;至于事件系统则控制这些低延时、高精度传输发生的时间。

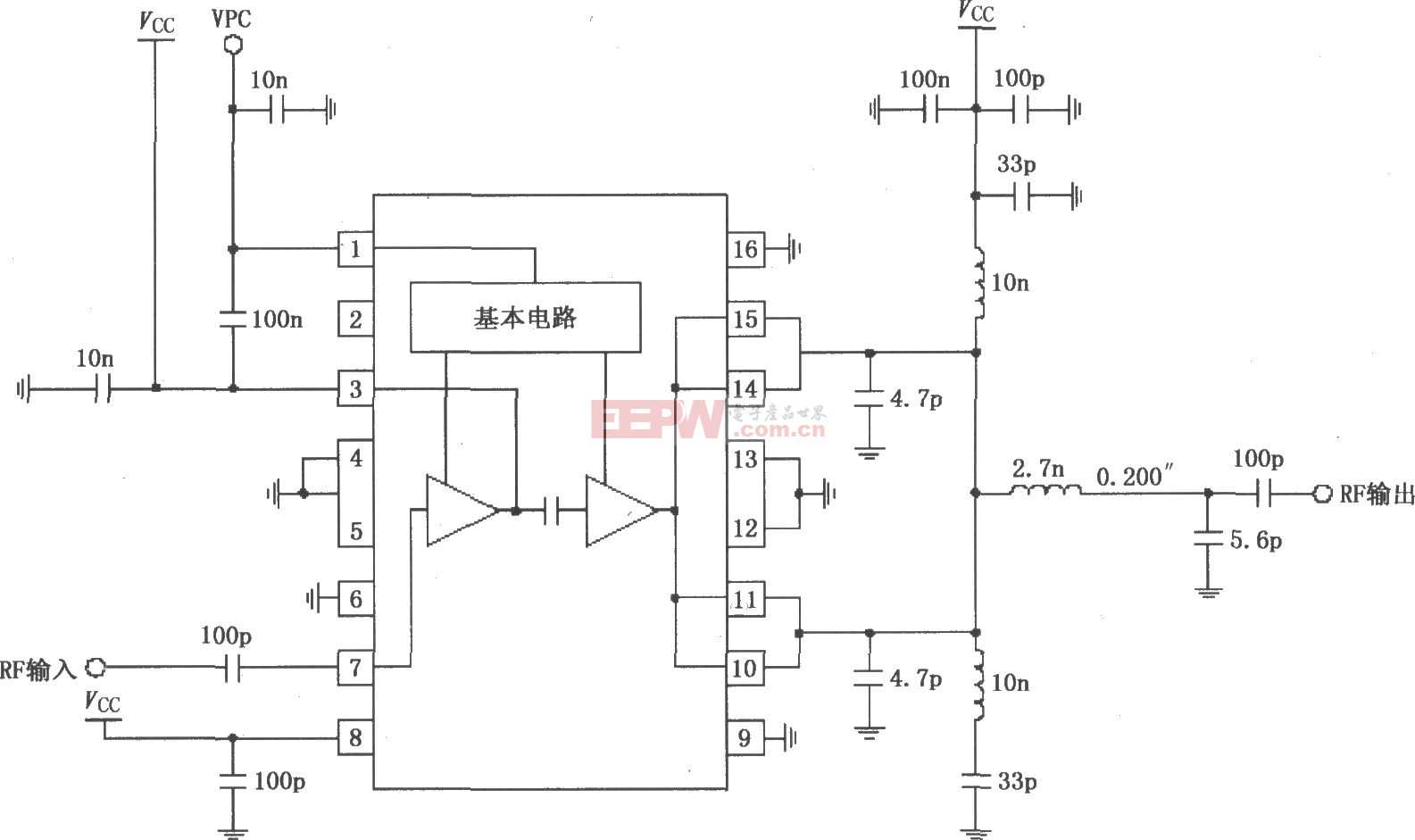

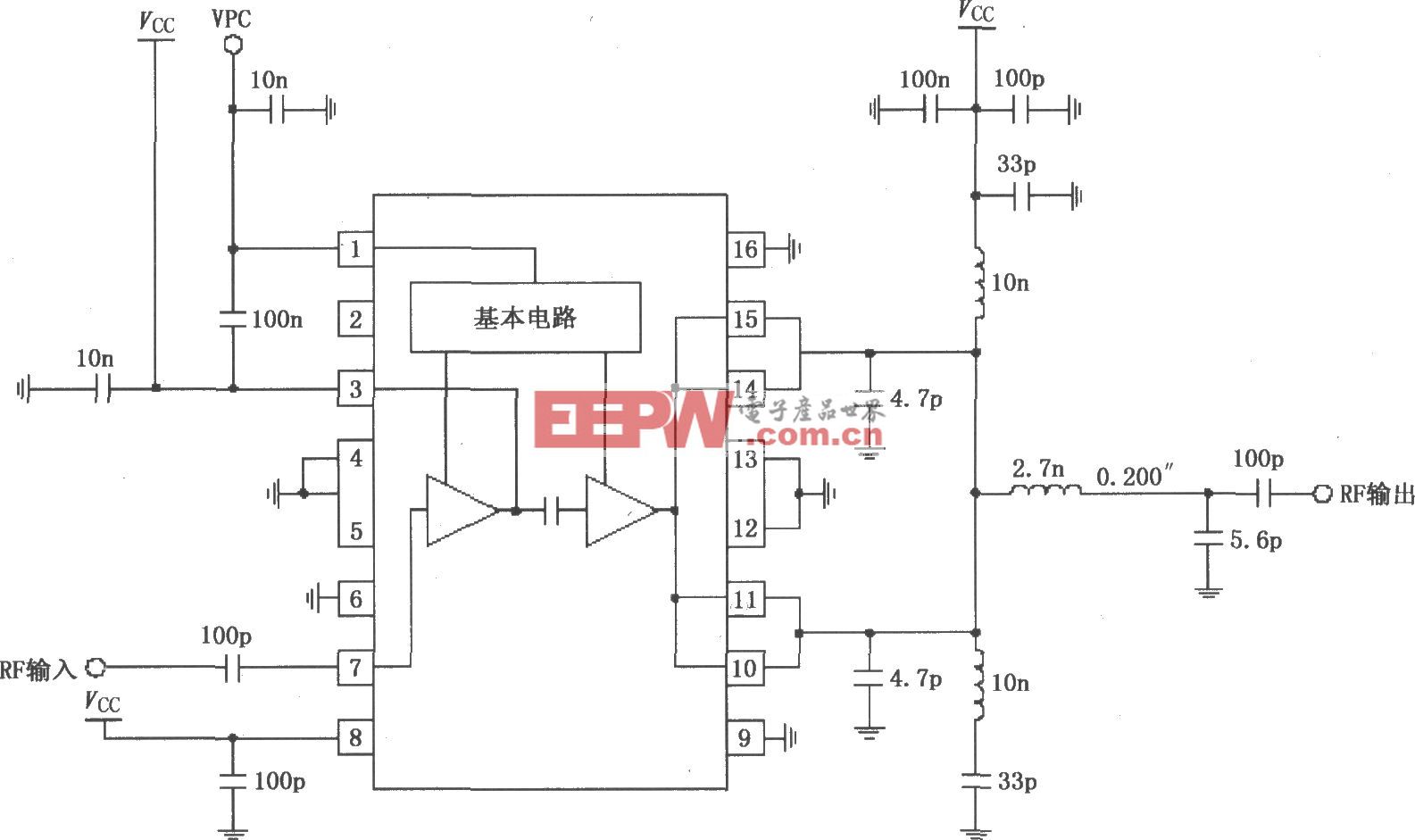

图2所示为事件系统与DMA共同工作的原理模块示意图。ADC连接一个传感器,并会采集信号样本。内部计数器被设置为与采样频率相匹配,用以提供规律且精确的时间间隔。事件系统可以直接激活ADC的采样,而无需中断CPU,使采样频率比利用微控制器的时钟更为精确。

图2 DMA控制器配合事件系统

事件管理可扩展为包含多个事件、连接多个外设的更复杂的配置。例如一个输入信号(事件1)可触发ADC采样(事件2),并把数值存储到DMA中(事件3),直到DMA缓冲器溢满(事件4)。

DMA控制器和事件系统还支持多通道,使开发人员能够配置一个与主CPU并行工作的互连结构,因此,可采用一种固定性方式来对多个并行实时任务进行协调。

评论