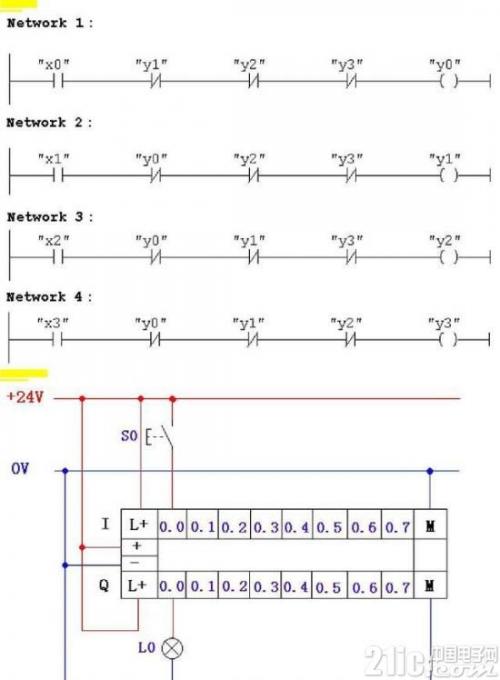

简述控制驱动法的实现

为减小导通损耗及反向恢复损耗,同步整流需要精确的时间控制电路,虽然已有几种方法来产生控制信号,我们现在采用一种从反馈系统来有源控制的栅驱动信号的定时系统。其关键优点在于该电路将根据元件状态的变化来特别调节同步整流MOSFET中的不可控的电容。时间的延迟及温度变化对MOSFET阈值的影响都可以根据反馈环来校正。

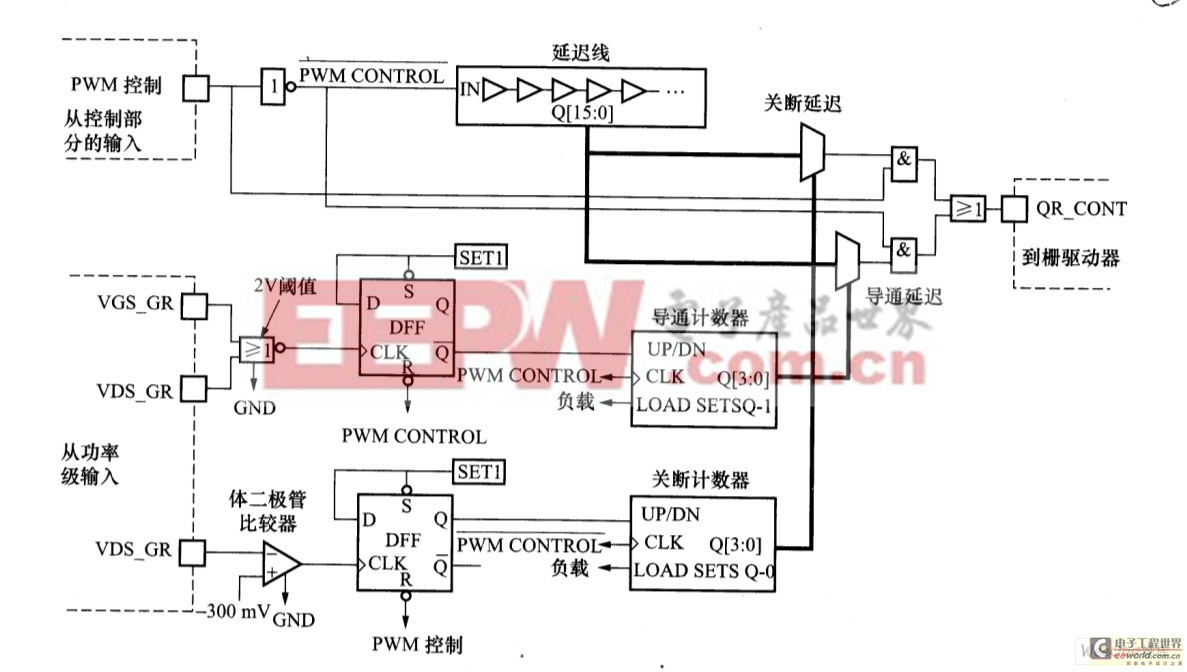

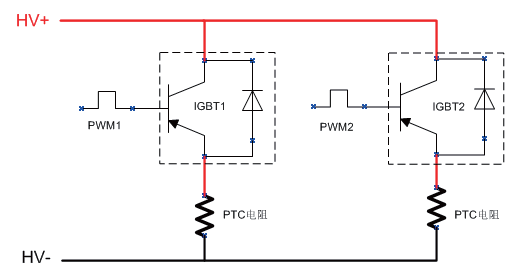

为控制栅躯动的时间,在图1中使用了可调延迟的电路,该延时电路包含三个主要元件,一个延迟线,一个乘法器及一个逻辑与门电路。到延迟线的输入信号是相对每个延迟元件都延迟几个纳秒的信号。为了产生控制导通的延迟,乘法器选择了使输出信号延迟的元件,最后与门确定延迟加到驱动导通的上升沿。从IN到OUT的延迟控制由数字控制总线来执行,数字总线加到乘法器的地址输入上。相反地,如果控制总线设置全部为0,则从IN到OUT的延迟就为0,即没有延迟。几种不同的延迟时间可以设定,给出几种开启延迟时间,关闭延迟时间,或对称的开启及关断延迟。注意看图1中是一个电压检测电路及数字控制器,为执行不同的延时设置,会用不同的电压检测电路及数字控制器。

图1 可调延迟电路

A、控制驱动VR的执行方案

控制驱动电路的设计从回流的MOSFET VR开始。随着其源漏电压降到零,它将立即被关断。一种实现它的简单方法就是用比较器检测VR的源漏电压过零时间,用这种方法的问题在于通过比较器,逻辑电路及栅驱动的延迟会产生出来,这要给予考虑。即使非常快的电路,延迟总量也会有50ns或更多。此期间体二极管会导通,并增加大的导通损耗,从检测降落的源漏电压到MOSFET导通时,一个逻辑回应的固有时间延迟可以用从最后一个开关周期得到的信息处理,去预置下一次的MOSFET的导通。在此预期方法中,MOSFET的栅压开始在其源漏电压降落之前就增加。此期间让栅压提前动作,在源漏电压降下时其即导通,而体二极管决不会导通。

图2展示出控制电路可实现VR的导通及关断。它使用了两个乘法器,两个记数器,一个延迟线及控制MOSFET导通及延迟的胶合逻辑,因此消除了体二极管的导通。电路的描述从MOSFET的开启延迟开始。PWM控制信号驱动初级侧MOSFET Q1,同时加到延迟线。当电源第一次启动,则LOAD输入到记数器为高电平,它设置了开启延迟的计数器为全部是1(高电平),而设置了关断延迟计数器全部为零(低电平),随着计数器开始记数,从控制电路的输出到栅驱动的结果之间为最大的导通延迟及最小的关断延迟。

图2 VR的控制电路

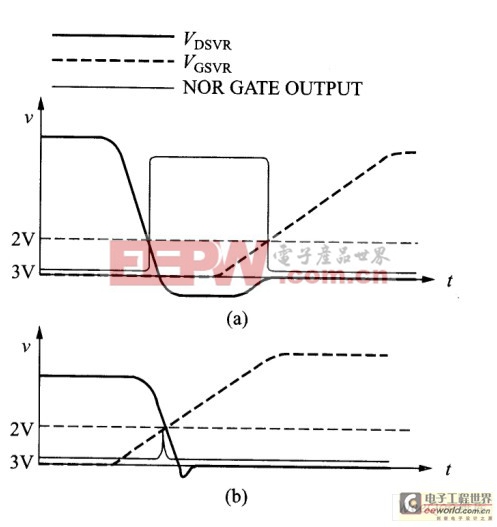

随着延迟设置了这些数值,VR体二极管将会导通,反馈环路也将开始调节延迟,使之实现最小的体二极管导通,图3(a)和(b)展示出VR在导通期间的栅源和漏源电压,图3(a)展示在VR导通时延迟太长的电路,而图3(b)展示出最佳延迟时间。

图3 VR的开启波形

调节关断延迟,用一个或门在一个大约2V输入阈值,来检测VR的栅源电压和漏源电压两者是否都为低电平时的状态,从或门出来的高电平指示控制器,告之延迟时间太长,控制器就会在下一个开关周期减少延迟。

或门输出被锁存、倒相并送至开启延迟计数器的UP/DOWN输入端,该信号告诉计数器向上记数或向下记数。如果或门输出为高电平,则记数器向下记数,减少延迟时间。而或门为低电平输出时,计数器向上记数,则增加延迟时间。计数器并有效地保持该延迟信息给下一个工作周期。反馈环会调节开启延迟使之缩短,直到或门没有更长的输出脉冲,当计数器工作在恒定负载和线路电压时,对下一个周期的开启延迟将稍微有些加长,或门将给出高输出脉冲,延迟将会缩短,在这种方式中,电路会在两个延迟时间之间抖动,一个长一些,另一个就会接近最佳状态。

关断控制器工作在与开启控制器非常相似的管理方式。不同之处在于电压检测电路及计数器的记数方向。当体二极管导通时,用一高速比较器检测。为了更加精确,一个比较器用于检测体二极管导通,去替代或门,在开启的期间,电流正从整流MOSFET向回流MOSFET换向,电流的DI/DT非常高,VR的源漏电压上通常可看到其震铃。如果用一个比较器检测体二极管在VR导通期间的体二极管状态,由于源漏电压的振铃,可能会出现误触发。在VR关断期间,通过VR MOSFET器件的电流是恒定的。该电流或者通过其通道或者通过其体二极管。在关断时,仅有非常小的振铃,比较器用来改善精度,比较器的阈值必须比先前的MOSFET通道导通时的误触发值更负向一点。

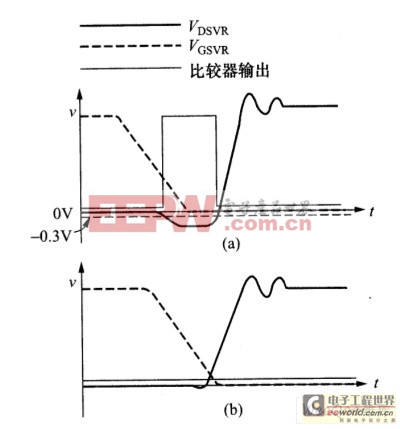

在通道导通期间,源漏电压大约等于I LOAD*.RDS(ON),并规定了噪声。比较器阈值设置在大约-300mV。比较器比较VR的源漏电压与此设置阈值,从比较器出来的高电平指示给控制器,系体二极管在导通,延迟时间需要增加,这与开启局面精确对应。因为关断延迟记数设置在起始时全部为0。图4(a)和(b)示出VR关断波形及比较器的输出。

图4 VR的关断波形

(a)非最佳延迟( b)最佳延迟

图4(a)示出当延迟设置太短时电路的工作状态。图4(b)示出最佳延迟状态。由于在VR导通中,关断延迟在某一值处处于抖动状态,这就是太长以及最佳值的两个状态。

问题出现:开启延迟及关断延迟可否设置的短些,这是否会造成交叉导通,问题在于仔细地研究比较器的特性,及延迟线的每个元件的延迟,比较器仅能响应差分输入电压,此电压仅在转换间隔结点上有足够的时间总量才会存在。假定比较器可以检测出体二极管导通用5ns时间。在下一个周期内,延迟即可调节,用延迟线上一位数码去减少体二极管的导通。当然,比较器也不会去响应下一个周期体二极管的导通,因为它在延迟线的每个元件上大约减少5ns的延迟时间。关键防止交叉导通的措施是设置的每个元件的延迟要比比较器可检测的最小脉宽要少。

B、 控制驱动QF的执行

正向整流的QF的控制和回流元件VR很不一样。一个主要的区别是:其目标是在变压器复位后即将QF开启,它独立于PWM控制信号的上升沿和下降沿,它不同于回流的MOSFET。此处,目标只不过是调节PWM控制器信号的上升沿及下降沿的时间,以减少VR体二极管的导通时间,并使之最小化。

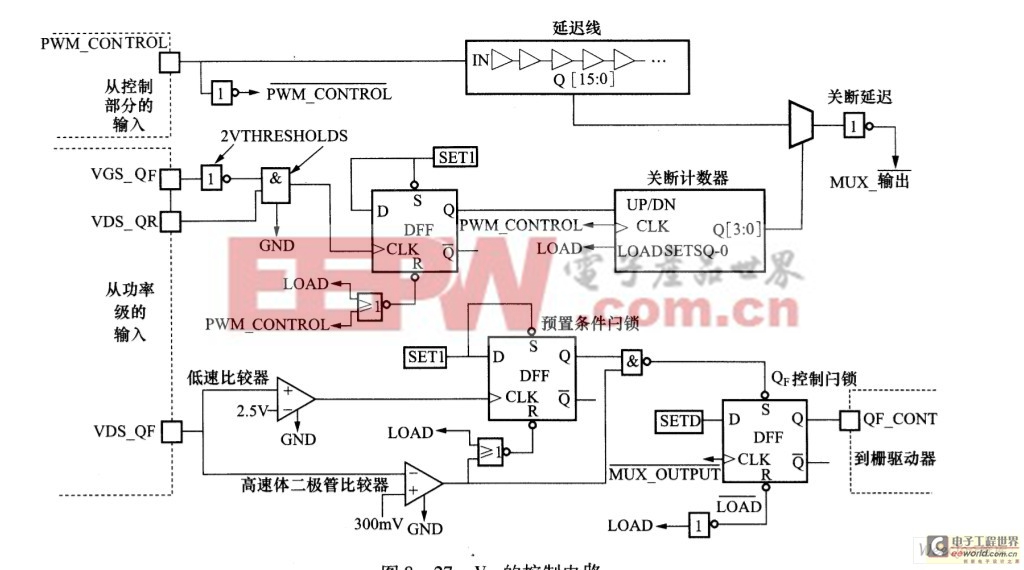

了解该目标是在变压器复位后要将QF导通,一个好的起始点就是图5所示出的使QF导通所需的电路。

图5 VR的控制电路

首先,一个高速体二极管比较器用于检测QF开始导通时的体二极管,它在变压器复位时间间隔结束时发信号,偏巧如图6所示,这个比较器还将检测出的初级侧MOSFET Q1关断后令其体二极管正好导通。

使用该比较器仅单独为开启QF,并确保在Q1进入关断的时间。这样变压器将绝不容许复位。为防止这一点,用一个低速比较器检测QF的源漏电压升至2.5V。当QF源漏电压升过2.5V时,设置了一个预置锁存调节,它将使高速体二极管比较器能输出工作。在QF源漏电压降过-300mV的体二极管比较器阈值,QF就立刻导通,并设置QF的控制锁存。在高速比较器输出变成高电平。预置锁存即刻复位,开启电路在下次导通事件中就处在恰当状态。从体二极管比较器检测出体二极管的导通固有延迟期间,到QF导通的通道,体二极管传导变压器的磁化电流。虽然在此间隔内,在QF体二极管有导通损耗,但与之相比,这已是QF遇到的最小的损耗。如果QF在此糟糕的时间间隔还保持关断的话。为完全消除这个损耗,用一个相同的预先控制的方案,用来开启VR,虽然这在理论上是可以的,但实际上会相当困难,因为此处没有PWM控制信号的脉冲沿存在,此时系变压器完全复位的状态。

评论