时域反射仪的硬件设计与实现----关键电路设计(四)

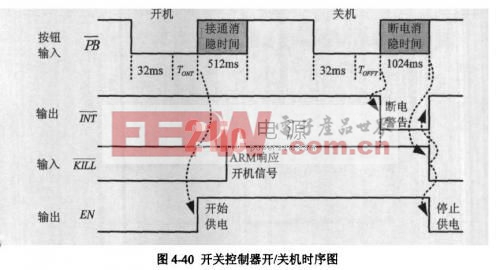

里被忽略。该消隐时间表示完成DC心C转换器和处理器上电操作所需的最大时间,如果

引脚未在该slZms时间窗口里被拉至高电平,则使能输出将被释放,前提是slZms为系统的上电操作提供了足够的时间。

防反跳断电:如果要启功断电操作,则

引脚保持于低电平的最小时间也必须为32ms(几即),同样可以利用在OFFT引脚上增加电容器的方式来增加额外的关断防反跳时间(几脚),电容几阿与几脚的关系和开机设置采用的关系式一致。一旦尸召被拉低,则

引脚将被转换至低电平,用来提醒处理器执行其断电和内务处理任务,留给处理器的断电时间为1024ms,如果处理器提前完成上述任务的处理,则可提前

拉低,以释放使能输出,否则1024ms时间到以后,使能输出将被强制释放。图4礴0给出了简单的开关控制器在执行上电和断电任务时的时序图。

在关机控制上也可以采用软件关机,即当软件检测到定时关机时间到或者是电池电量不够时,可在完成相关的内务处理以后,将

置成低电平,则输出使能被主动释放,随即关闭了DC心C转换器。当供电被切短以后,控制器非常低的静态电流(6uA)对电池电量的消耗是微不足道的,有效的延长了电池的使用时间。

评论