时域反射仪的硬件设计与实现----关键电路设计(四)

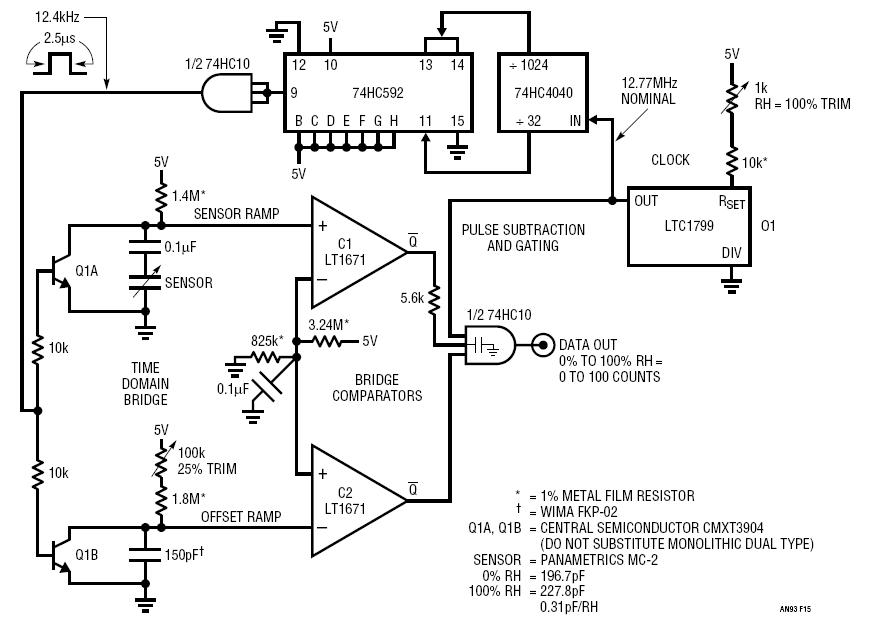

引脚相距较远时,则寄生电容有可能耦合到高阻抗

输入端上。此外,寄生串联电感还有可能在

引脚上引发不可预测的振铃干扰,因此在

引脚和按钮开关之间布设一个5K电阻器将使寄生电感问题有所缓解,在

引脚上接一个0.luF的电容器到地,可以减轻寄生容性耦合的影响。

开关控制电路的工作分为防反跳接通和防反跳断电两部分。

防反跳接通:当首次给控制器加电时,器件将对输出引脚进行初始化,此时与EN引脚相连的DC心C转换器将被保持在关闭状态,如果确定要是EN为高电平输出,来打开DC/DC转换器,则PB引脚保持低电平的最小时间必须为32ms(TON),并可通过在ONT引脚上布设一个任选电容器来提供额外的接通防反跳时间(CONT),下面的式子给出了电容CONT,与TONT的关系:

一旦使能输出EN被确定,则任何连接到该引脚的DC心C转换器均被接通。

来自处理器的

输入在随后的512ms消隐时间

评论