资深工程师关于数字电源转换的方案介绍

模拟工程师以前在设计需要具有多路输出、动态负载共享、热插拔或广泛故障处理能力的电源时,往往需要与复杂性抗争。利用模拟电路来实现系统控制功能并非总是经济有效或灵活的。采用模拟技术设计电源需要使用“过大的”元件来解决元件变化和元件漂移的问题。即使是在克服了这些设计难点之后,这些电源在生产线末端还需要进行人工调整。

那么,模拟工程师应该选择什么来设计电源呢?工程学对这个问题的回答是利用功率转换反馈环路的智能数字控制来实现上述功能。单片机已使模拟设计人员能够实现监控、控制、通信甚至确定性功能(如电源中的上电时序、软启动和拓扑结构控制等)。不过,由于缺乏经济有效的高性能技术,以数字方式控制整个功率转换环路还不太现实。

开关电源中的DSC设计

现在,一种新型数字信号控制器(DSC)的问世使具有智能电源外设等功能的数字转换成为可能,因为这种器件采用基于计数器的脉冲宽度调制(PWM)模块、基于模拟比较器的反馈和协调模数转换器(ADC)采样,可以在一个单时钟周期内进行快速乘法。这些特性的组合有助于DSC处理控制环路软件所需的较高执行速度。

在开始进行电源设计之前,需要做出以下决择。

1. 选择一种适合应用需要的拓扑结构:升压型还是降压型(Boost还是Buck),隔离式(正向、半桥还是全桥)。

2. 选择一种开关技术:硬开关还是软开关。软开关技术(如谐振模式或准谐振模式),以增加电路和控制的复杂程度为代价,换取较少的开关损耗。

3. 选择一种控制方法:电压模式还是电流模式。

电压模式控制和电流模式控制是基于传统模拟开关电源(SMPS)控制技术的两种控制方法。在电压模式条件下,利用期望的输出电压和实际的输出电压之间的差值(误差)来控制电源电压施加在电感器上的时间,进而间接地控制电感器中的电流。在电流模式控制条件下,利用期望的输出电压和实际的输出电压之间的差值 (误差)为模拟比较器创建一个门限值来设置峰值电感电流,从而控制平均电感电流。电压模式可以在噪声环境中或宽工作范围条件下提供更高的稳定性;电流模式控制可以实现逐周期的电流限制和更快的瞬态响应,它还可防止可能导致电感器饱和并引起灾难性MOSFET故障的“逐步增加的电感电流”。

4. 选择PWM工作频率。高频PWM有助于使用更小的电感器和电容器,但是需要额外付出开关损耗为代价。

5. 确定需要的控制带宽。这在很大程度上取决于应用所期待的负载瞬态响应。

6.根据估计的控制带宽需求来分配处理器资源。虽然有多种控制算法,但是常用的技术仍是比例、积分和微分(PID)方法。使用常用PID算法,控制环路将需要以所需控制系统带宽的八倍速度运行,以保证足够的相位容限。在估计控制环路的延迟时,控制环路内的所有延迟都必须考虑到(参见“计算控制环路的延迟”部分)。

接着,选择一个可以满足您所有或大多数设计需求的DSC。

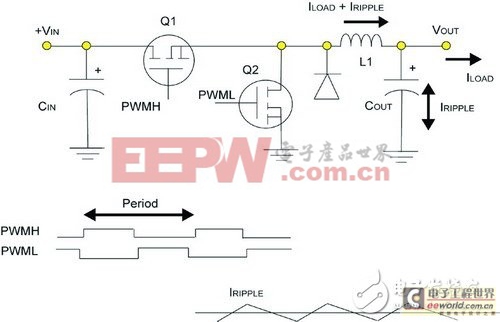

选择采用Microchip的SMPS dsPIC DSC——dsPIC30F2020来设计一个同步降压式转换器。这种DSC有一个硬开关,可提供互补PWM模式的电压控制模式。这种降压式转换器(见图 1)采用同步开关,用一个MOSFET取代了电路中的整流器,因为它比标准整流器有低得多的正向电压降。通过降低电压降,这种降压式转换器的整个效率可以提高5%~10%。同步开关与Q2需要一个次级PWM信号来补充初级PWM信号。当Q1关断时,Q2接通,反之亦然。此外,在PWM信号的上升沿和下降沿期间,需要利用“死区”控制来防止Q1和Q2同时导通。

图1 同步降压式转换器

降压式转换器的输入与输出电压的关系可以表示为:

VOUT = VIN ( D,其中 D = PWM占空比 = TON /(TON + TOFF)

一个降压式转换器理想的输出电压是输入电压与晶体管占空比的乘积。通过检测(见图1),如果晶体管Q1是常通的,输出电压将等于输入电压。如果Q1是常断的,那么输出电压将为零。实际上,当负载电流增加时,晶体管和电感器两端存在的电压降将会增加。图2给出了如何使用DSC设计数字SMPS控制系统。

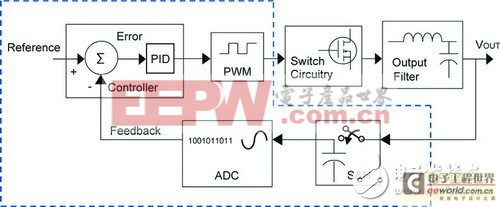

图2 用于同步降压式转换器的典型SMPS控制系统

采样保持(S/H)电路通常每2~10ms进行一次采样,ADC需要大约500ns将模拟反馈信号转换成为数字值。PID控制器是一种运行于DSC的程序,有大约1~2ms的计算延迟。该控制器输出可以转换为一个PWM信号,由它来驱动开关电路。当进入新的占空比时,如果PWM发生器不能立即更新其输出,就可能出现明显的延迟。晶体管驱动器和相关的晶体管也会引入大约50ns到1微秒的延迟,其长短因使用的器件和电路设计而异。

计算控制环路的延迟

总控制环路延迟是ADC采样与转换时间(500ns)、PID计算时间(1μs)、PWM输出延迟(0)、晶体管切换时间(50ns)和PID执行速度时期(2μs)之和。这个例子中的总环路延迟是3.65μs,这意味着最大有效控制环路的采样率为274 kHz。虽然尼奎斯特定理需要2倍的采样率来重建一个信号,数字控制环路仍必须以6倍至10倍采样率进行采样。这样做的原因是只使用2倍的采样率,相位滞后将180度。利用2倍采样率,我们已经用完了180度的相位滞后“预算”,而没有考虑系统中任何其他的延迟。一个采用8倍采样率的系统单在采样过程引入 45度的相位滞后,这是一个好得多的采样率。为了有足够的相位容限,许多数字控制系统对模拟信号进行了10倍或更高的过采样。假定最高有效采样率为274 kHz,有效控制带宽是其八分之一,也就是大约34 kHz。

SMPS设计中PWM的重要性

不同的电源规范推动着对不同电源拓扑结构的需求,

pid控制器相关文章:pid控制器原理

评论