STWD100xP系统硬件抗电磁干扰技术的应用

1 嵌入式系统EMC的产生

本文引用地址:https://www.eepw.com.cn/article/227763.htm嵌入式系统产生电磁干扰的大小和抗电磁干扰的能力同系统本身功能有很大关系,不同嵌入式系统产生的电磁干扰不同抗电磁干扰能力也不同。

1.1 高次谐波干扰

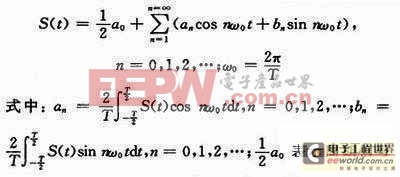

根据Fourier series任何一个周期信号S(t)并非单一波形,都由直流分量、基波和各次谐波组成,谐波频率十分丰富,周期信号S(t)可以用式(1)表示:

直流成分,当n=1时表示信号基波,n=2,3,4,…表示信号2,3,4,…各次谐波,其中基波是该信号主要组成成份,很多时候信号的特性呈现为基波特性。例如在电源系统中交流信号为S(t)=380sin 2π50t表示市电信号存在n=1的基波,信号在基波附近谐波频率不断增加、幅度迅速衰减,从理论上说正弦和余弦信号频谱只存在一点冲击信号。正弦信号本身所产生的谐波较小而其他电磁干扰参杂在正弦信号中造成系统谐波很大。系统对信号的基波要加以利用,对信号的谐波要加以抑制、滤除。正弦信号本身对外来干扰信号的抑制能力较差容易出现EMC,严重干扰系统工作,影响系统稳定性。

1.2 嵌入式系统主频过高,引起干扰

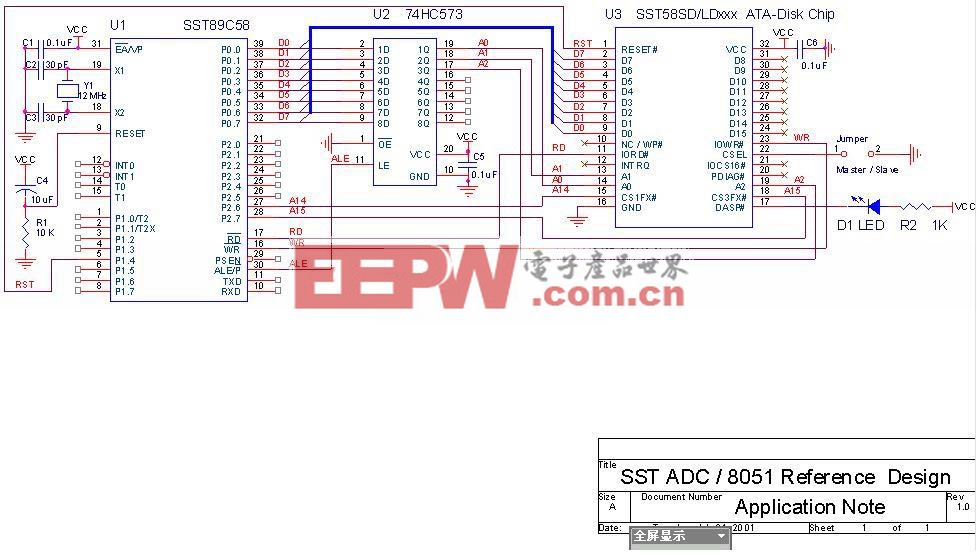

随着电子技术的发展,CPU处理速度越来越快,数据吞吐量越来越大,主频越来越高。8位51单片机系统主频为12MHz,16位凌阳单片机系统主频为50MHz,Altera公司Cyclone系列FPGA芯片系统主频可达200MHz,以Inter PAX255,PAX270,PAX310为核心的嵌入式系统主频可达820MHz,CPU主频过高信号变化速率过快,信号幅度大的地方容易引起干扰。根据Fourier Series和Euler Formula,方波信号频谱为Sine信号,Sine信号为连续信号其本身谐波很大,容易造成系统工作不稳定。2 嵌入式系统硬件抗EMC技术

嵌入式系统工作不稳定、不可靠因素有很多,干扰可以来自系统本身也可以来自本系统外其他系统,关于系统干扰靠软件处理能起一定作用,但仅靠软件没有硬件的局面难以支撑,系统抗干扰问题始终难以解决。在可编程系统中为了增加系统稳定性和可靠性,减小系统CPU开支,常用以下方法:

2.1 抑制电源谐波干扰

在可编程电子系统中,能够解决好电源干扰问题就解决整个系统干扰的一大半,很多干扰都是从电源中出来,电源干扰过大会造成系统不稳定。单纯正弦信号不会有干扰,关键正弦信号处于干扰很大的环境中,这时正弦信号就会附加干扰。例如:电源线过长在电源线上就会产生寄生干扰,可以在电源线上加上小磁珠或磁环滤波,要求不高的情况下可以加100Ω电阻对干扰信号进行衰减,使干扰信号对系统不起作用。对开关电源来说,主要是振荡器振荡频率过高引起谐波,不仅影响电源而且会影响整个系统,开关电源效率较高很多地方都采用,但在要求比较高的系统中仍然采用线性电源。

2.2 CPU选择能够满足系统要求的最低主频

CPU主频过高系统时钟加快,系统时钟产生的方波频率升高,由方波带来的谐波随之增加。从Fourier Series和Euler Formula得单一方波比正弦波的谐波幅度大得多,谐波频率复杂得多,由此系统主频越高产生的谐波越复杂,影响系统工作的稳定性。但随着电子技术的发展,CPU主频越来越高,电子系统越来越复杂,功能不断增加,集成度不断提高,但对于CPU来说无论哪方面使用,系统主频够用即可。

2.3 减小信号在传输过程中的衰减、畸变和反射

现代集成电路制造主要采用CMOS技术,输入阻抗大、输出阻抗小,抗干扰能力强,适合小信号放大。CMOS集成电路输入电流大约为1 mA,信号在电路板上延时Td与电路板引线阻抗有关,阻抗越大信号衰减越大、信号延时越长、系统发热越大,系统稳定性越差。在高速系统设计过程中要考虑PCB信号传输延时Td,使信号人为延时Tr大于信号传输延时。

2.4 注意PCB布线和元器件高频特性

PCB布线最大原则是元器件之间引线尽量短、信号线交叉尽量少,尽量不用或少用过孔。模拟地、数字地、高频地分开走线,然后汇聚成一点,大功率器件、小功率器件和干扰信号特别大的器件在布局时要分开。对干扰信号特别敏感的高频元器件可以用金属罩屏蔽起来,避免电磁干扰。

2.5 退耦电容的使用

一般在系统集成电路

评论