利用8051内核使SoC设计不再复杂的模拟仿真

在前面描述中可以看到,在该芯片设计中由于采用标准的8051核,其指令系统和体系结构基本没有改变,但其中一些特殊寄存器与外围模块之间建立了映射关系,中断源也得到了扩充。因此,验证和仿真器的设计关键在于能否正确反映这些寄存器的状态或通过寄存器控制这些外围模块的工作。

在系统芯片设计流程中,仿真器的设计与芯片设计同步甚至要提前,因此没有现成的CPU芯片作仿真器核心;而简单地将CPU与FSK、DTMF、CAS等功能芯片组合起来替代该CPU芯片,不能实现完全仿真和模拟,特别是无法获得外围模拟模块的状态。

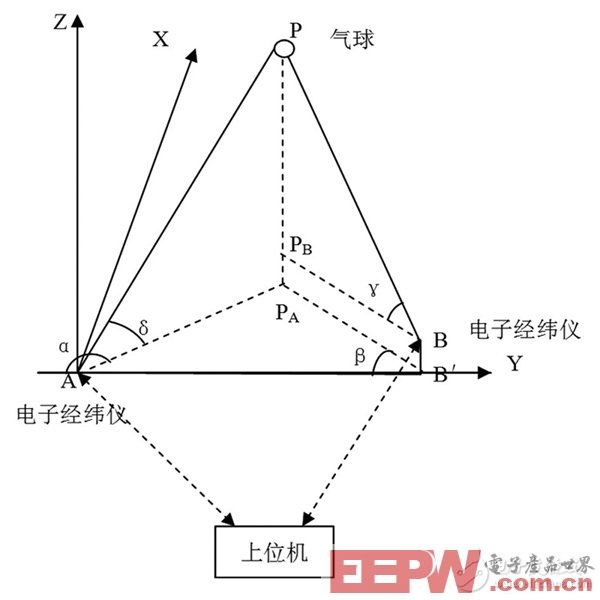

在这里,我们采用FPGA和FSK、DTMF、CAS等功能芯片组合成模拟CPU来替代所设计的系统芯片,系统结构可参照图3。图3中,8051核及数字接口部分由FPGA实现;CID部分中,FSK、DTMF、CAS、振铃检测等模块则由相应硬件模块实现。

图3 短消息系统芯片仿真方案图

FSK、DTMF、CAS、振铃检测等模块通过接口与FPGA中8051相应寄存器对应,这样在这些外围模块动作的同时,在8051寄存器中都能正确映射;反之FPGA中相应寄存器的改变,会引起这些外围模块的动作。

图3是建立在通用8051仿真器上的短消息系统芯片仿真方案。模拟CPU模块集成了FPGA和CID部分芯片和电路,该模块采用与8051定义一致的引脚与仿真板相连。对于仿真板来说,该模块的命令和操作与标准8051是一致的,因此通用的仿真和集成环境不需要改变。仿真接口由通用8051仿真接口和模拟CPU模块中的CID外接信号共同组成,其引脚封装定义与系统芯片一致。这样通过通用仿真集成环境可以观察和控制CID部分电路,从而实现了对整个短信息系统芯片的完全验证和仿真。

采用该方法,具有以下优点:

◇ 实现了对该SoC芯片系统功能的验证;

◇ 完全兼容现有集成开发和仿真环境;

◇ 简化了数模混合设计的验证问题;

◇ 经过改进,可以利用通用仿真器仿真和调试硬件、软件;

◇ 由于FPGA可以随着芯片的改进而重新编程,因此增大了设计和验证的灵活性;

◇ 缩短了开发时间,加快芯片上市时间。

4 结论

利用该方案构成的系统芯片验证和仿真方案已经在我们的设计中得到了应用。事实上,利用该方案的思想不仅可以实现基于8051核系统芯片的验证和仿真,其它系统芯片的验证和仿真也是可以借鉴的。

评论