利用 Platform Flash PROM 实现多重启动功能

一些应用利用 Xilinx FPGA 在每次启动时可改变配置的能力,根据所需来改变 FPGA 的功能。Xilinx Platform Flash XCFxxP PROM 的设计修订 (Design Revisioning) 功能,允许用户在单个PROM 中将多种配置存储为不同的修订版本,从而简化了 FPGA 配置更改。在 FPGA 内部加入少量的逻辑,用户就能在 PROM 中存储的多达四个不同的修订版本之间进行动态切换。多重启动或从多个设计修订进行动态重新配置的能力,与 Spartan-3E FPGA 和第三方并行 flash PROM 一起使用时所提供的 MultiBoot 选项相似。

本应用指南将进一步说明 Platform Flash PROM 如何提供附加选项来增强配置失败时的安全性,以及如何减少引脚数量和板面积。此外,Platform Flash PROM 还为用户提供其他优势:iMPACT 编程支持、单一供应商解决方案、低成本板设计和更快速的配置加载。

本应用指南还详细地介绍了一个包含 VHDL 源代码的参考设计。

简介

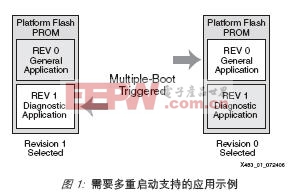

与 FPGA 少量的内部逻辑结合,Platform Flash PROM 可方便地支持需要动态选择多种 FPGA配置或修订版本(即多重启动)的应用。利用 Xilinx Platform Flash 的 设计修订功能和 FPGA少量的内部逻辑,即可实现多重启动。该示例为需要多重启动功能的应用,此时 FPGA 需要同时支持一般功能和诊断功能(图1)。在这种情况下,FPGA 使用诊断应用启动以进行板级测试。如果测试成功,FPGA 就通过第二个包含正常工作所需的一般功能配置镜像的比特流触发重配置。一般的 FPGA 应用设计用于进行重配置,以便随时按需重新加载诊断应用。

图1 所示的示例中,默认配置作为修订版本 1 而存储到 PROM 中。此默认配置在系统复位时加载。当多重启动被触发时,FPGA 将使用存储在 PROM 中的配置镜像(修订版本 0)来自动重配置。

注: Revision Select[1:0] 输入有一个 50KΩ 的内部上拉电阻接到 VCCO,在引脚未被驱动时,向器件提供逻辑 1。

作为修订版本 1 存储的默认配置可包含一个“最佳”或“失效安全型”配置镜像,可用于与外界进行通信,检查是否存在更新的配置镜像。如果存在更新的配置镜像,并且能够通过验证,那么最佳配置会触发重配置来加载新的镜像。

注: 用户能够选择使用存储在多达 4 个修订版本位置的任意一个配置镜像,来重配置 FPGA。

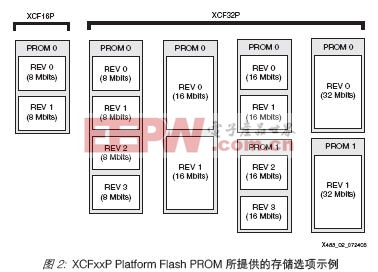

设计修订设计修订允许用户在单个 PROM 或多个级联的 PROM 中存储多达 4 个不同的配置镜像(图2)。与动态重配置结合,Platform Flash PROM 的设计修订能力就能创建多重启动应用。

利用设计修订,每个配置镜像都被存储到一个特定的修订版本位置(0 到 3),并且都能得到串行和并行输出模式下的 8/16/32 Mbit XCFxxP Platform Flash PROM 的支持。利用 iMPACT 软件能够创建 PROM 编程文件和修订版本信息文件 (.cfi)。稍后需要使用此 .cfi 文件实现设计修订编程功能(详情请参见 Xilinx ISE 8 软件手册)。

在使用一系列配置镜像对 Platform Flash PROM 进行编程后,可以通过外部 REV_SEL[1:0] 引脚或内部可编程设计修订控制位,来选择一个存储在特定版本位置的配置镜像。

EN_EXT_SEL 引脚决定是使用外部引脚还是内部控制位来选择设计修订版本。当

EN_EXT_SEL 为低电平时,通过外部修订版本选择引脚 REV_SEL[1:0] 来选择使用哪个修订版本。当 EN_EXT_SEL 为高电平时,则通过内部可编程的修订版本选择控制位来选择相应的修订版本。

注: 对于本应用指南的与参考设计, EN_EXT_SEL 须置为低电平。

上电时,由配置 PROM 的内部逻辑对设计修订版本选择输入(引脚或控制位)进行采样。上电结束后,当 CE 置为低电平(启用 PROM 输入),则在 CF 脉冲的上升沿,将再次对设计修订版本选择输入进行采样。在此参考设计中, CE 接地,用户将利用 FPGA 上的一个 I/O 来控制 CF,请参见第 5 页“参考设计”。选中的设计修订版本的数据会出现在 FPGA 配置接口上。此接口可以是 8 位 SelecMAP (并行)或串行的。详情请参见 DS123,Platform Flash 在系统可编程配置 PROM。

典型应用

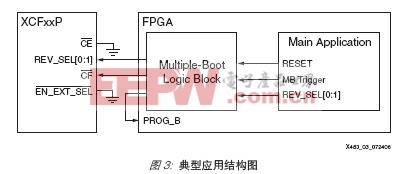

要利用 Platform Flash PROM 实现多重启动功能,需要对标准 PROM 接口进行一些修改,并且在 FPGA (图3)中嵌入少量控制逻辑。除下面这几个不同之处外,大部分与配置 PROM 的标准连接保持不变:

CE 必须与低电平相连,以确保 PROM 一直处于启用状态。在通常情况下, CE 与 DONE相连,以便在配置完成后禁用 PROM。

CF 由 FPGA 内部的多重启动控制逻辑的一个输出驱动,而不再像通常那样连接到

PROG_B。

FPGA 的 PROG_B 引脚由多重启动控制逻辑的一个输出驱动。

注: 该连接需要使用 FPGA 的一个用户 I/O。

REV_SEL 由多重启动控制逻辑的输出驱动。

控制逻辑监控 RESET,而 RESET 可复位控制逻辑状态机和多重启动触发器(图3 中的 MB 触发器)。每个状态间的时序非常关键;如果要确保成功进行重配置,就需要仔细观察一些建立和保持时间。这里给出了一个经过充分验证的控制逻辑设计,可以满足这些时序约束条件(请参见第 5 页“参考设计”)。

硬件接口

要启用多重启动功能,FPGA 的一个输出控制 PROM 上修订版本选择引脚的采样。该信号与PROM 上 的 CF 输入相连。当 PROM 检测到 CF 上的一个上升沿时,就开始对修订版本选择引脚进行采样。修订版本选择引脚 REV_SEL[1:0],由 FPGA 的其他输出驱动,他们可控制由哪个修订版本来为 FPGA 提供配置数据。修订版本选择引脚至少要在采样被触发前 300 ns 时被设置好,(请参考 Platform Flash 在系统可编程配置 PROM)。CF 变为高电平之后,FPGA 内部的多重启动逻辑模块将一个与 PROG_B 相连的输出驱动至低电平,并保持 300 ns,以触发重配置。配置完成后,FPGA 将按照选中的那个修订版本来工作。

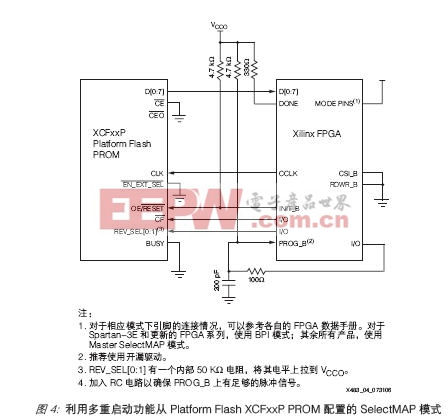

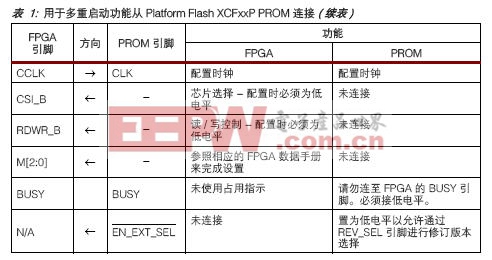

第 4 页图4 和表1 说明 FPGA 用于与 SelectMAP 模式下的 Platform Flash PROM 接口的配置信号。

参考设计

本应用指南中所描述的参考设计,使用 Platform Flash PROM 中存储的修订版本实现了加载多重启动配置数据所需的控制逻辑。在 FPGA 内部实现的控制逻辑包含一个状态机,用来选择设计修订版本和对 FPGA 进行动态重配置。多重启动控制逻辑设计成一个单独的模块,以方便地集成到设计中。使用该模块时,用户须建立适当的连接,并在主应用中插入逻辑,以便在触发动态重配置过程之前,设置和保持 REV_SEL 引脚。

本应用指南中所描述的参考设计,可从以下站点下载:

http://www.xilinx.com/cn/xlnx/xweb/xil_publications_display.jsp?category=Application+No

tes/Device+Configuration+and+Programming/FPGA+Configuration

show=xapp483.pdf

控制逻辑状态机

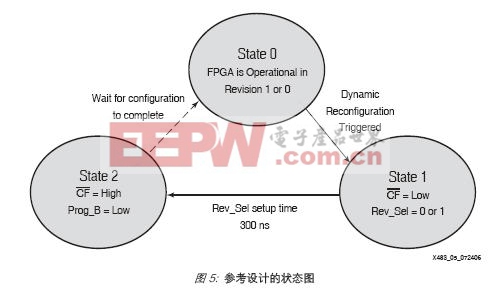

控制逻辑状态机包含三个状态:

状态 0

一上电,FPGA 就从初始状态(未画出)进入状态 0,以便对设计中使用的变量或信号进行置位/ 复位。收到来自主 FPGA 设计的动态重配置的触发信号后,状态机从状态 0 进入状态 1。

状态 1

在控制逻辑将一个低电平信号驱动到 PROM 上的 CF 引脚上,并将主应用设置好的修订版本传至 PROM 的 REV_SEL[0:1] 引脚。

在达到指定的 REV_SEL 建立时间后 (300 ns),状态机进入状态 2。

注: 对于使用 XCF16P PROM 或只需两个修订版本位置的设计,多重启动控制逻辑模块的 Rev_sel[1] 输入必须接地,并且 PROM 的 REV_SEL[1] 也必须与地相连,以确保对 FPGA 进行适当的配置。

状态 2

一旦进入状态 2,状态机就将一个高电平信号和一个低电平信号分别驱动至 PROM 的 CF 输入和 FPGA 上的 PROG_B 引脚上。300 ns 后,重配置开始,FPGA 开始对配置存储器重新进行初始化。一旦 INIT_B (在与 PROM 上 OE/RESET 相连的 FPGA 上)变为高电平,FPGA 即已准备好接收数据。PROM 将存储在被选中的修订版本中的配置数据发送到 FPGA 中。重配置完成后,FPGA 配置逻辑就通过将 DONE 引脚置为高电平来发出信号。随后,状态机回到状态0。

注: 本应用指南假设每个修订版本都包含有多重启动控制逻辑的例示。实际上,状态 2 下 PROG_B 变为低电平后(300 ns 后),配置存储器包括状态机都会被擦除。因此,状态机实际上不会从状态 2 回到状态 0,而是在状态 2 中就停止工作。重配置和初始化 FPGA 之后,新配置中的多重启动控制逻辑例示将再次进入状态 0。

参考设计中所使用的状态机的状态图如图5 所示。

优势这里所描述的多重启动解决方案的主要优势有:

进行重配置时不需要其他器件。该解决方案仅需要一个 Platform Flash XCFxxP PROM 和一个 FPGA,而大多数重配置设计都需要另一个逻辑器件,如 CPLD。

动态重配置 FPGA 的能力。只要不要求同时实现存储在每个修订版本位置上的功能,用户就能够在同一个 FPGA 上实现 4 种完全不同的设计,从而有效地对 FPGA 资源进行分时操作。

此外,多重启动还能让用户利用 Platform Flash PROM 的优势:

集成式 iMPACT 编程支持。在系统可编程能力 (In-System Programmability) 可以在开发和验证期间轻松修改设计。

更快速的配置。Platform Flash PROM 在快速配置方面进行了优化,可使用 x8 接口和 30ns 的配置时钟周期。

所需的接口线路数量减少,降低了板成本。由于只需使用数据线,因此与并行的 NOR

flash 存储器相比,板上布线的信号数量被降至最低。主串行模式下的配置能够节省更多的引脚,仅需 4 个引脚就能配置 FPGA。

单一供应商支持。客户可以利用 Xilinx Platform Flash 和 Xilinx FPGA 获得单一供应商解决方案。

了解 Platform Flash PROM 优势方面的更多信息,请访问:

http://www.xilinx.com/cn/products/silicon_solutions/proms/pfp/index.htm

结论

Xilinx Platform Flash XCFxxP PROM 使用户在其设计中能够实现多重启动功能。实现多重启动功能最基本的条件就是 Platform Flash PROM 的设计修订能力,它允许将多个 FPGA 配置存放到单个 PROM (Xilinx FPGA 系列所有产品均支持)。Platform Flash PROM 的设计修订能力与动态重配置功能结合,就产生了功能强大的多重启动。

利用 Platform Flash PROM 易于实现多重启动解决方案,可降低板成本,获得iMPACT 编程支持,并且允许对 FPGA 进行快速配置。

如欲了解更多赛灵思技术文档,请访问http://china.xilinx.com/china/documentation/

评论