VHDL设计的消抖与滤波

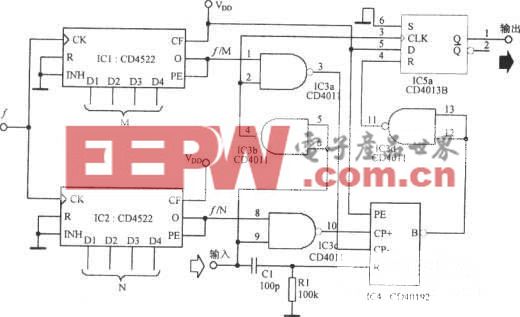

在同一块电路板上,由于信号线的走线过长而产生的高频毛刺我们可以通过在接近输入端串联一个100欧左右的电阻来滤除。但是对于板外信号,或者板内其他干扰造成较大的抖动时只好采用积分电路来滤波,即串一个电阻还要并一个电容接地。

同样在VHDL中我们可以采用类似的办法,对于小于触发器建立时间的毛刺可以用时钟打一下实现滤波。但对于开关或按键抖动等较大的干扰,我们可以采用延时比较法或积分法,或者二者并用。

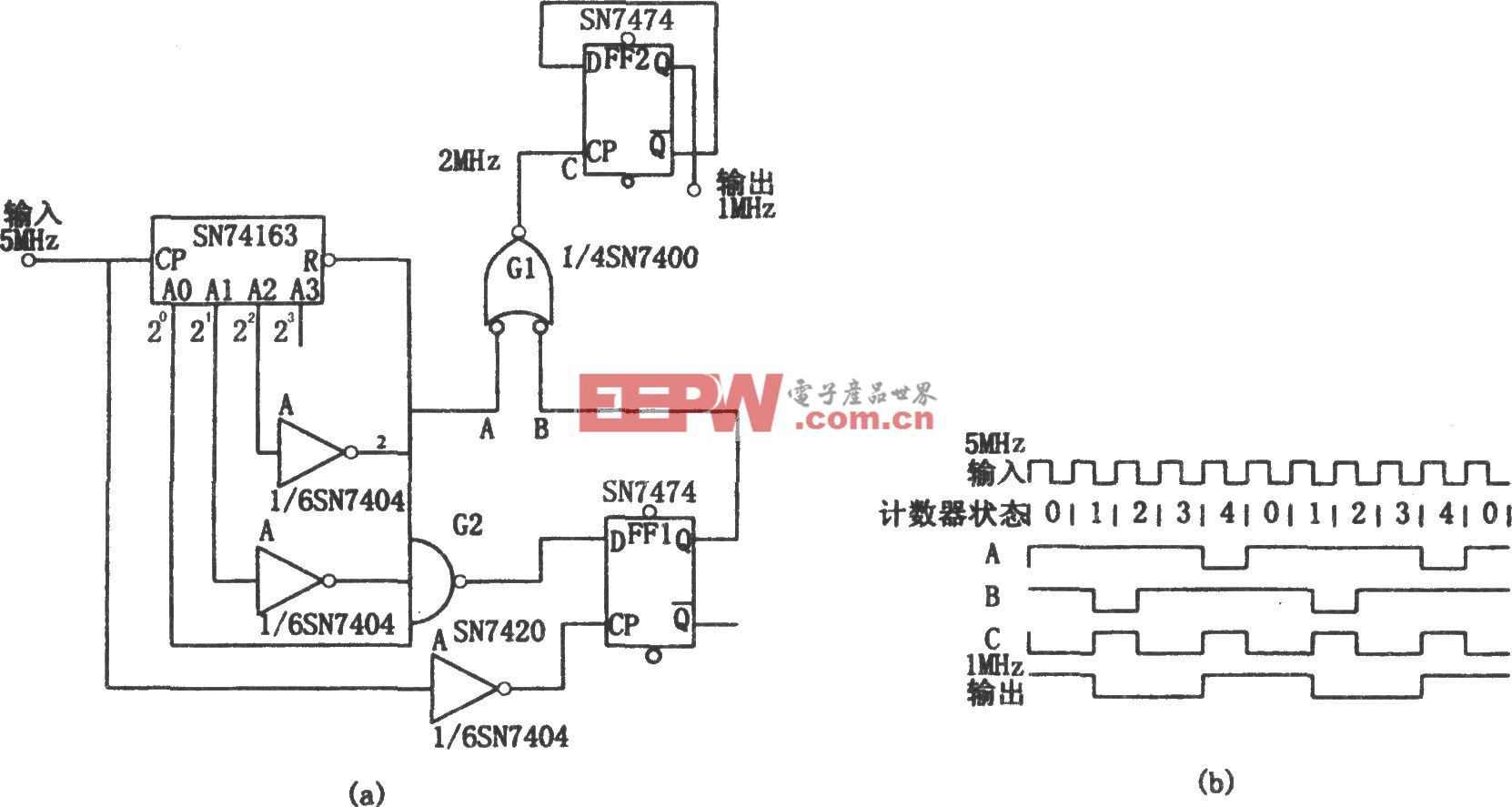

比较法:这个方法很好理解,就是若干个时钟周期读取的数据相同时我们认为收到了一个稳定的数据,否则认为是过渡态。即采用若干位的移位寄存器,当寄存器是全'1'或全'0'时才开始读数。这种方法的缺点是,当干扰脉冲较宽时我们必须等比地扩大移位寄存器的比特,消耗较大资源。

积分法:用一个增减计数器,当输入信号为'1'时计数器递增计数直到计数器全'1'停止计数、否则计数器递减计数直到全'0'停止计数。那么计数器的 MSB即为输入信号的去抖信号。你也可以用时钟再加上一个速度较慢的使能来对输入信号计数。显然计数器的位数要求与要去抖的抖动脉冲宽度的对数关系。当然也可以二者结合,前端用几个比特的移位寄存器实现比较,比较结果作为计数使能来控制接下来的增减计数器的计数。

评论