基于FPGA的多路I2C总线设计与实现

摘 要: 介绍了一种基于FPGA的多路I2C总线设计与实现。主要包括系统处理器、局部总线、FPGA逻辑模块、负载设备几部分,实现了从处理器局部总线到I2C协议的转换及其多路扩展,使系统具有多个I2C总线通道,且每一路I2C总线上能挂载多个不同的主设备或从设备。该系统中各路I2C总线相互独立工作,没有干扰和影响。

关键词: I2C;可编程逻辑门阵列;状态机

I2C(Inter-Integrated Circuit)总线是由Philips公司开发的用于IC器件之间连接的二线制总线,其为双向、两线、串行、多主控接口标准,具有总线仲裁机制,非常适合器件之间近距离、非经常性的数据通信。由于其具有接口线少、控制方式简化、器件封装形式小、通信速率较高等优点,I2C总线的应用非常广泛[1]。

在工业监控系统中需要有多路I2C总线控制器来完成温度、电压、湿度等各个方面的监控功能。但是,目前很多系统没有或者只有很少通道的I2C总线接口,使其应用受到了限制。

基于上述技术现状,本文通过现场可编程门阵列FPGA(Field Programmable Gate Array)实现一种多路I2C总线的系统控制设计。

系统硬件设计

FPGA作为ASIC专用集成电路领域中的一种半定制电路,可以解决定制电路的不足,又克服了原有可编程器件门电路数有限的缺点,具有设计周期短、开发费用低、保密性强、体积小、重量轻、可靠性高等特点[2]。

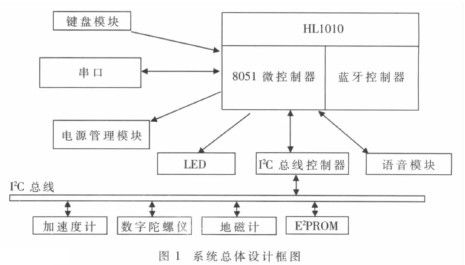

本系统主要由系统处理器、局部总线、FPGA逻辑模块、负载设备几部分组成。其中系统处理器采用Freescale公司的MPC8245[3]。

具有多路I2C总线的系统硬件设计框图如图1所示。

处理器利用局部总线,通过地址线、数据线、读写信号线和片选信号线与FPGA逻辑模块进行通信,在FPGA内部完成I2C总线控制器的功能,实现从处理器局部总线到I2C协议的转换和多路扩展,其中每个I2C总线控制器挂载多个不同的设备,可以是主设备或从设备。

FPGA逻辑模块设计

多路I2C总线的系统控制中,FPGA逻辑模块的设计是核心。该模块主要由三部分组成:顶层控制模块、处理器接口模块、多路I2C总线控制器模块。模块化的设计便于移植和软件重用。其中FPGA芯片采用XILINX公司的SPARTAN3A系列的芯片,开发平台为ISE10.1。

顶层控制模块

顶层控制模块主要实现处理器接口模块与多路I2C总线控制器模块之间的连接与通信,实现整个输入输出接口到各个功能模块之间的映射。三者之间的逻辑关系如图2所示。

处理器接口模块

MPC8245处理器接口模块主要完成MPC8245处理器与FPGA的接口功能,并实现与FPGA内部的多路I2C总线控制器数据传输的握手协议和数据交换。在MPC8245处理器接口模块中,每个I2C控制器对应有4个8位的寄存器,即数据寄存器、地址寄存器、控制寄存器和状态寄存器。

(1)数据寄存器根据读/写信号区分,分为发送数据缓冲寄存器和接收数据缓冲寄存器,共享一个地址,数据长度为8位。

(2)地址寄存器用来保存当前地址。当该路I2C控制器作为从节点通信时,地址寄存器中保存的是自己的地址,这个地址在总线上是唯一的。从节点接收到包头后,将其中的地址与自己的地址比较,如果一致,则响应主节点,开始传输。

(3)控制寄存器用来控制I2C总线控制器的数据传输,按照设置产生各个协议命令、响应动作及工作模式。

(4)状态寄存器显示当前总线的状态。通过状态寄存器中不同的状态指示,实现与MPC8245处理器的握手协议。

MPC8245处理器利用地址线、数据线、片选信号和读写信号来与MPC8245处理器接口模块N路I2C总线控制器相关的N×4个寄存器交换数据、读取状态、作为从设备时响应的地址和控制各路I2C总线的控制器。

I2C总线控制器模块

I2C总线控制器模块主要实现并行的I2C通信控制,每一路I2C总线控制器通过FPGA的I/O管脚连接到外部实现各自独立的I2C总线,具有主工作模式和从工作模式两种工作状态。

I2C总线控制器主要有两个状态机:主控制状态机和时钟生成状态机。

主控制状态机是整个I2C总线控制器的核心。时钟生成状态机只在I2C总线控制器作为主设备时的模式下工作,是I2C总线通信时的时钟。当I2C总线控制器作为从设备通信时,主控制状态机时钟由FPGA所实现的I2C总线上所挂载的I2C主设备提供,整个I2C总线通信时的时钟为外部主设备提供的时钟。

I2C总线控制器状态机设计

(1)主控制状态机

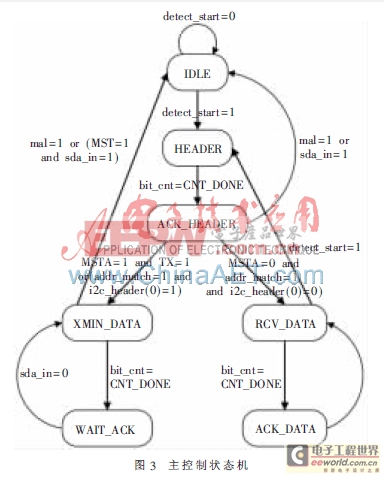

主控制状态机状态转移图如图3所示。

IDLE状态:当I2C上电或者复位后,主控制状态机就处于此状态。

HEADER状态:在此状态,系统根据控制寄存器位MSTA值,发送或者接收包头,满足条件后,转移到ACK_HEADER状态;I2C总线控制器中的HEADER移位寄存器与地址寄存器中存放的I2C总线控制器作为从设备时响应的地址进行比较,如果匹配,则表明该路I2C总线控制器为被主设备寻址的从设备,模式立刻切换到从设备模式,同时状态寄存器中的MAAS位被置位,数据线SDA将会按照TXAK中的设置应答当前主设备。

ACK_HEADER状态:当该路I2C总线控制器作为主设备时,如果没有收到从设备发送的ACK,则发送结束信号,返回到IDLE状态;如果收到ACK,则确定仲裁没有丢失,根据控制寄存器位TX值转到XMIT_DATA或者RCV_DATA状态;当该路I2C总线控制器作为从设备时,如果地址匹配,则发送ACK,根据主设备发送的第一个字节中的最后一位的值转到XMIT_DATA或者RCV_DATA状态。

XMIT_DATA状态:在此状态时,移位寄存器将数据移到SDA线上。发送一个字节完成后,转移到WAIT_ACK状态。

WAIT_ACK状态:在此状态时,如果收到ACK,则返回到XMIT_DATA状态;如果仲裁丢失,则转到IDLE状态;如果没有收到ACK,则发送结束信号,转移到IDLE状态。

RCV_DATA状态:在此状态时,如果检测到重新启动信号,则返回HEADER状态;否则,移位寄存器从SDA线上移入数据,以供MPC8245处理器的驱动程序读取,移入一个字节后,转到ACK_DATA状态,控制寄存器中的TXAK位被输出到数据线SDA。

ACK_DATA状态:I2C控制器发送ACK,返回到RCV_DATA状态。

(2)时钟状态机

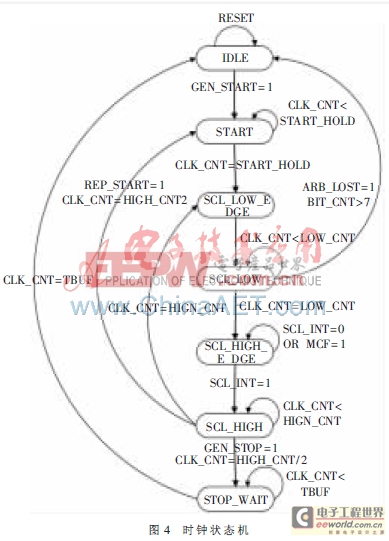

整个状态机状态转换如图4所示。

SCL_IDLE状态:当上电复位后,状态机就处于该状态。当I2C控制器为主节点并且总线空闲时,收到开始标志后,转移到START状态。

START状态:当在此状态时,根据I2C协议,需要保持一定的时间,当持续时间满足要求时,转移到SCL_LOW_EDGE状态,否则保持在START状态。

SCL_LOW_EDGE状态:当在此状态时,在下一个系统时钟时,转移到SCL_LOW状态。

SCL_LOW状态:在此状态时,根据控制信号,设置SDA的输出,根据I2C协议,需要保持一定的时间,当保持时间满足要求时,转移到SCL_HIGH_EDGE状态,否则保持在该状态;如果仲裁丢失且已经传输了7个字节,则转移到SCL_IDLE状态。

SCL_HIGH_EDGE状态:在此状态时,完成一定的操作,持续一个时钟周期后,转移到SCL_HIGH状态。如果SCL输入为0或者状态寄存器中的位MCF=1,则一直停留在该状态。

SCL_HIGH状态:在此状态时,如果有重复起始信号,则SCL高电平持续一半时间,转移到START状态;如果有结束信号,则SCL高电平持续一半时间,转移到STOP_WAIT状态;根据I2C协议,需要保持一定的时间,当持续时间满足要求时,转移到SCL_LOW_EDGE状态,否则保持在当前状态。

STOP_WAIT状态:在此状态时,根据I2C协议,需要保持一定的时间,当持续时间满足要求时,转移到SCL_IDLE状态。

系统工作流程

多路I2C总线的系统在系统上电后,处理器通过FPGA与FPGA相连接的I2C设备通信。

(1)当处理器作为主设备与FPGA所实现的I2C总线上所挂的从设备进行通信时,处理器主体通过对FPGA内部的该路I2C总线控制器对应的寄存器进行操作,根据I2C总线通信协议,产生起始信号和时钟信号,并查询状态位,对该路I2C总线上的从设备进行发送或者接收数据的操作,在数据交换完成后,产生停止信号,完成整个通信。

(2)当处理器主体作为从设备与FPGA所实现的I2C总线上所挂的主设备进行通信时,FPGA所实现的I2C总线上所挂的主设备产生起始信号和时钟信号,处理器主体通过对FPGA内的该路I2C总线控制器对应的数据寄存器进行操作,发送或者接收数据。当通信完成后,FPGA所实现的I2C总线上所挂的主设备产生停止信号,完成整个通信。

通过可编程逻辑器件实现的多路I2C总线上每一路可以挂多个设备,可以是从设备,也可以是主设备,具体能挂的设备数量受总线电容的限制。

本设计利用可编程逻辑器件,完成对处理器主体I2C总线的扩展,使该处理器能够有多个I2C总线通道,每一路I2C总线上可以挂载多个不同的设备,可以是主设备,也可以是从设备,满足不同应用场合的要求。在可编程逻辑器件内,每个I2C总线控制器仅使用4个寄存器,大大降低了控制的复杂度,无需占用较多的CPU资源,系统稳定,执行效率高。

评论