51单片机总线时序

一、总线概述

计算机系统是以微处理器为核心的,各器件要与微处理器相连,且必须协调工作,所以在微处理机中引入了总线的概念,各器件共同享用总线,任何时候只能有一个器件发送数据(可以有多个器件同时接收数据) 。

计算机的总线分为控制总线、地址总线和数据总线等三种。而数据总线用于传送数据,控制总线用于传送控制信号, 地址总线则用于选择存储单元或外设。

二、单片机的三总线结构

51系列单片机具有完善的总线接口时序,可以扩展控制对象,其直接寻址能力达到64k( 2的16次方) 。在总线模式下,不同的对象共享总线,独立编址、分时复用总线,CPU 通过地址选择访问的对象,完成与各对象之间的信息传递。

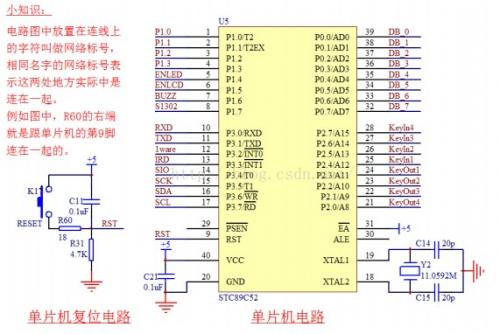

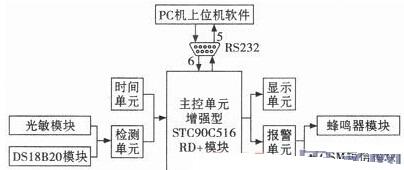

单片机三总线扩展示意如图1 所示。

1、数据总线

51 单片机的数据总线为P0 口,P0 口为双向数据通道,CPU 从P0 口送出和读回数据。

2、地址总线

51 系列单片机的地址总线为16 位。

为了节约芯片引脚,采用P0 口复用方式,除了作为数据总线外,在ALE 信号时序匹配下,通过外置的数据锁存器,在总线访问前半周期从P0口送出低8位地址,后半周期从P0 口送出8 位数据。

高8位地址则通过P2 口送出。

3、控制总线

51 系列单片机的控制总线包括读控制信号P3.7 和写控制信号P3.6 等,二者分别作为总线模式下数据读和数据写的使能信号。

三、单片机总线时序分析

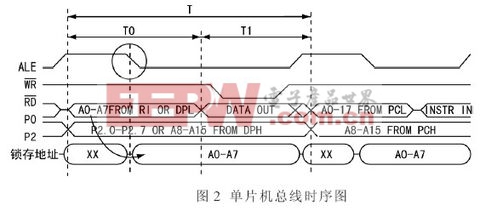

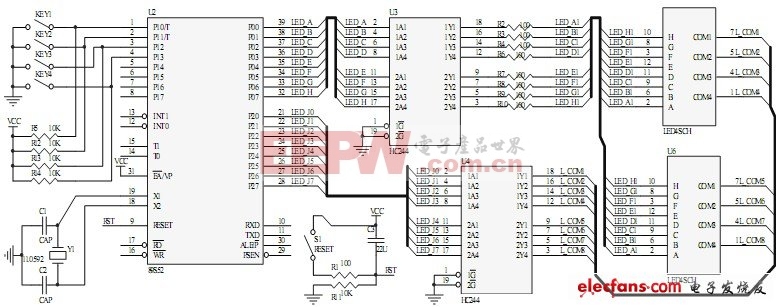

51 单片机总线时序如图2 所示。

从图2 中可以看出,完成一次总线( 读写) 操作周期为T,P0 口分时复用,在T0 期间,P0 口送出低8 位地址,在ALE 的下降沿完成数据锁存,送出低8位地址信号。在T1 期间,P0 口作为数据总线使用,送出或读入数据,数据的读写操作在读、写控制信号的低电平期间完成。

需要注意的是,在控制信号( 读、写信号) 有效期间,P2 口送出高8位地址,配合数据锁存器输出的低8 位地址,实现16 位地址总线,即64kB 范围的内的寻址。

由于CPU不可能同时执行读和写操作,所以读、写信号不可能同时有效。

评论