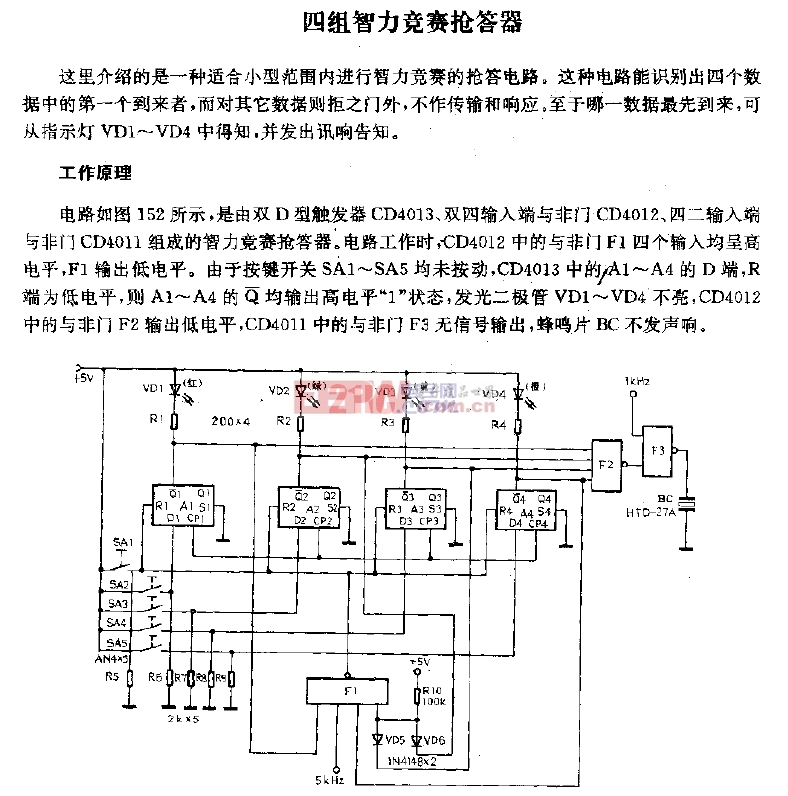

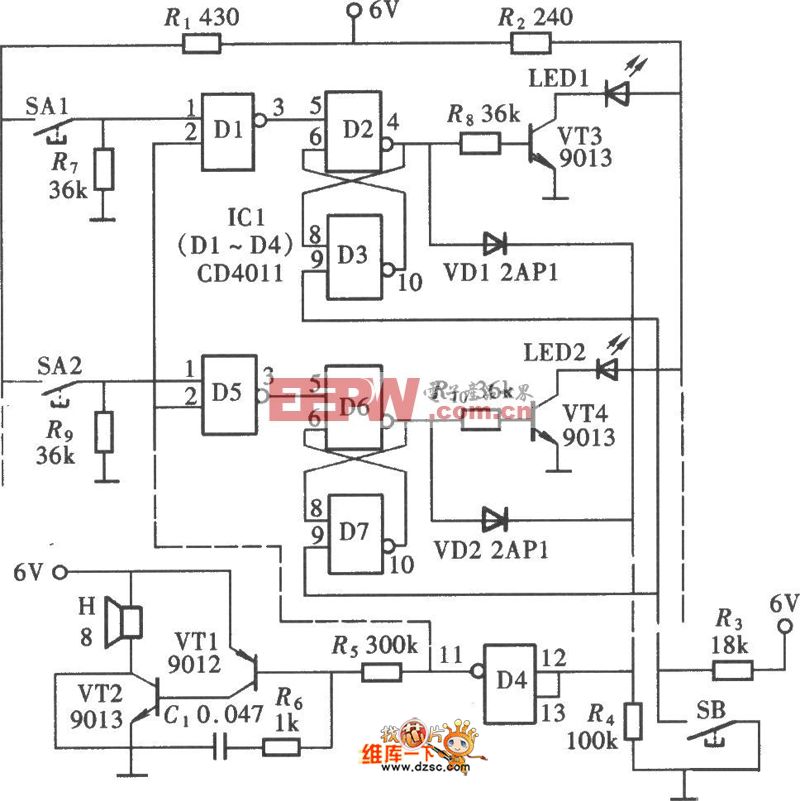

四组智力竞赛抢答器电路设计

按下复位space键,与电源接通得到高电平,同时加到4个D触发器的CD端,使得4个触发器的 端输出高电平,四个发光二极管熄灭,4输入与非门U7B输出低电平,U8A被封锁,蜂鸣器不响。

由于U1A、U1B、U2A、U2B的 端均为高电平,U1A、U2B的 分别加到4输入与非门U3A的2脚和4脚, U1B、U2A的 端经D1、D2(D1、D2、R10、VDD组成与门电路)加到U3A的5脚, 将U3A打开,由函数信号发生器XFG1产生的5KHZ的信号经反向后加到U1A、U1B、U2A、U2B的时钟端,此时U1A、U1B、U2A、U2B具备时钟条件。若先按下A键,与电源接通得到高电平,加到U1A的D端,此时 端输出低电平,“LED1”发光,同时U1A 端输出的低电平分两路:一路加到U7B的9脚,使U7B输出高电平,加到U8A上,将U8A打开,函数信号发生器XFG2产生1KHZ的信号经U8A、U5A两次反向,加到蜂鸣器上,使蜂鸣器发出声音。另一路加到4输入与非门U3A的2脚,使U3A输出高电平,同时加到U1A、U1B、U2A、U2B的时钟端,此时U1A、U1B、U2A、U2B不具备时钟条件,若再按下其他任何键时,抢答均无效,抢答器被锁定。如要进行下一轮抢答,必须先按下复位spa ce键即可。

三、设计依据

4013BD为双D上升沿触发器集成电路,其真值表如下:

/SD | /RD | CP | D | Q | /Q |

0 | 1 | X | X | 1 | 0 |

1 | 0 | X | X | 0 | 1 |

1 | 1 | ↑ | 0 | 0 | 1 |

1 | 1 | ↑ | 1 | 1 | 0 |

1 | 1 | 0 | X | Q | /Q |

逻辑表达式:Qn+1 =D CP为↑

4011BD为双输入四与非门,逻辑表达式:Y= /(AB),其真值表如下:

| A | B | Y |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

4012BD四输入双与非门集成电路,逻辑表达式:Y= /(ABCD),其真值表如下:

A | B | C | D | Y1 |

0 | 0 | 0 | 0 | 1 |

0 | 0 | 0 | 1 | 1 |

0 | 0 | 1 | 0 | 1 |

0 | 0 | 1 | 1 | 1 |

0 | 1 | 0 | 0 | 1 |

0 | 1 | 0 | 1 | 1 |

0 | 1 | 1 | 0 | 1 |

0 | 1 | 1 | 1 | 1 |

1 | 0 | 0 | 0 | 1 |

1 | 0 | 0 | 1 | 1 |

1 | 0 | 1 | 0 | 1 |

1 | 0 | 1 | 1 | 1 |

1 | 1 | 0 | 0 | 1 |

1 | 1 | 0 | 1 | 1 |

1 | 1 | 1 | 0 | 1 |

1 | 1 | 1 | 1 | 0 |

评论