传感器网络操作系统平台TinyOS下CC2420驱动组件的设计

网络节点是构成无线传感器网络的基本单位,无线传感器网络节点有两种常用体系结构:Atmel AVR处理器+TinyOS[1]和MSP430+TinyOS[2].本文采用 ATmega128L+TinyOS的体系结构。因此,CC2420驱动组件设计应符合TinyOS的硬件抽象体系结构(Hardware AbSTractiON Architecture,HAA)[3].TinyOS中将硬件抽象体系结构分为3层:硬件表示层(Hardware Presentation Layer,HPL)、硬件适配层(Hardware Adapation Layer,HAL)和硬件接口层(Hardware Interface Layer,HIL)。各层功能作用及具体设计原理在本文中作了细致的研究。CC2420是一款基于IEEE 802.15.4协议的低功耗无线收发模块。本文根据硬件抽象体系结构的原则,对CC2420无线收发模块在TinyOS平台下的驱动组件设计作了深入的研究,这使得基于CC2420硬件的无线传感器网络(Wireless Sensor Network,WSN)应用程序的开发,可以与TinyOS操作系统的组件模型、主动消息、基于事件驱动等机制有效地结合起来,使应用程序具有代码量小、能耗少、并发性高等特点。

1 nesC语言及TinyOS操作系统

早期的面向传感器网络的操作系统TinyOS是用汇编和C语言开发的。但经研究发现,C语言并不能高效地完成传感器网络的应用开发。所以研究人员对C语言进行了一定的扩展,提出了一种新型的编程语言--支持组件化编程的nesC(C language for network embedded Systems)语言[4].用nesC语言编写的TinyOS[56],将轻量级线程、主动消息通信模型、事件驱动机制和组件化编程等技术相结合,是一种专门为无线传感器网络开发的微型操作系统,使面向传感器网络的操作系统及应用程序开发的复杂度大大降低,使程序的整体性能得到优化,提高了程序的健壮性和安全性。

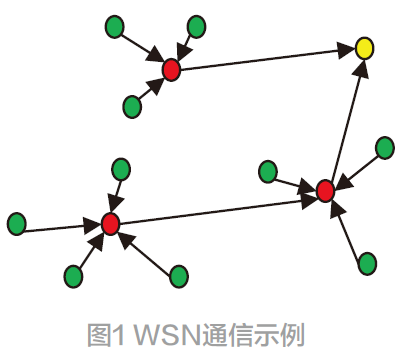

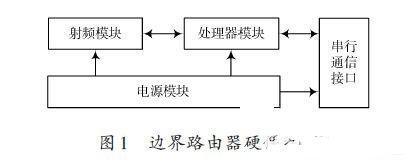

图1 TinyOS组件模型体系结构

TinyOS采用组件模型,这种模块化的思想使得应用程序的编写更加方便、高效。程序开发人员可以方便快捷地将独立的组件组合到各种配件文件中,并在应用程序的顶层(toplevel)配件文件中完成程序的整体装配。TinyOS的组件模型体系结构如图1所示。

上层组件对下层组件发命令,下层组件向上层组件发信号通知事件,最底层的组件直接和硬件打交道。TinyOS中有3种类型的组件:硬件抽象组件、合成组件、高层软件组件。硬件抽象组件将物理硬件映射到TinyOS组件模型;合成组件模拟高级硬件行为;高层软件组件负责数据传输、控制、路由等。本文针对的是实际硬件上的抽象层。

2 节点硬件模块

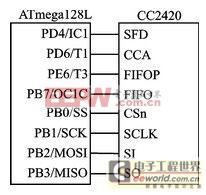

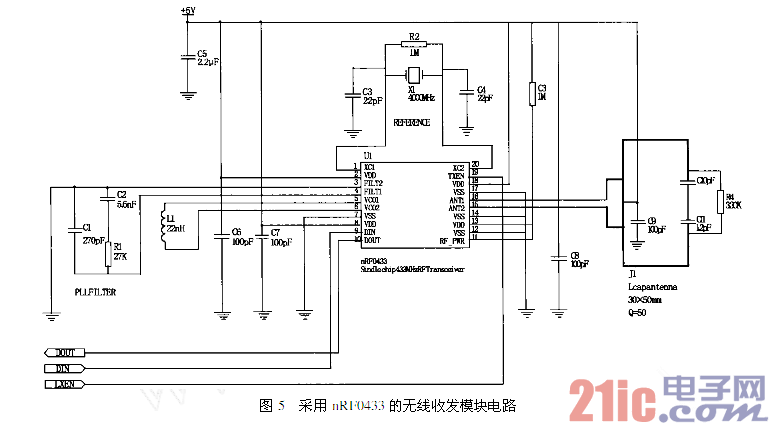

节点采用ATmega128L微处理器和CC2420无线收发模块,硬件连接如图2所示。

图2 ATmega128L与CC2420的硬件连接

CC2420[7]无线收发芯片符合IEEE 802.15.4标准,工作在ISM 2.4 GHz频段。其内部集成了压控振荡器、天线、16 MHz晶振等外围电路。CC2420通过SPI接口与ATmega128L完成设置和收发数据两方面的任务。如图2所示,SPI接口由CSn、SI、SO和SCLK四个引脚构成。ATmega128L为接口主设备,访问CC2420内部寄存器和存储区;CC2420为SPI接口从设备,接收时钟信号和片选信号,并在处理器的控制下执行输入/输出操作。

CC2420通过SFD、FIFO、FIFOP和CCA四个引脚与ATmega128L表示收发数据状态。CC2420收到物理帧的SFD字段后,会在SFD引脚输出高电平,直到接收完该帧。如果启用了地址识别,在地址识别后,SFD引脚立即转为输出低电平。FIFO和FIFOP引脚标识FIFO缓存区的状态。如果接收FIFO缓存区有数据,FIFO引脚输出高电平;如果接收FIFO缓冲区为空,FIFO引脚输出低电平。FIFOP引脚在接收FIFO缓存区的数据超过某个临界值时或者在CC2420接收到一个完整的帧以后输出高电平,触发ATmega128L的中断。CCA引脚有效表示信道空闲评估有效,通常为CSMACA算法的实现提供依据。

3 CC2420驱动组件

TinyOS中的硬件抽象体系结构分为3层:硬件表示层、硬件适配层和硬件接口层。本设计根据实际需求,完成了其中两层结构的实现。

3.1 HPL组件

如前面所述,ATmega128L通过SPI接口访问CC2420内部寄存器和存储区,CC2420使用SFD、FIFO、FIFOP和CCA四个引脚表示收发数据状态。硬件表示层的作用就是根据这种硬件连接将CC2420所提供的硬件基本功能以接口函数的形式封装起来,供上层HAL组件调用,实现对底层硬件的隔离。

HPL体系结构如图3所示。HPL组件包括3个模块文件HPLCC2420FIFOM、HPLCC2420M、HPLCC2420Interrupt,分别实现CC2420的不同功能接口,最后由HPLCC2420C以组件的形式将所有的接口函数封装起来,提供给HAL组件调用。

评论