改进微控制器架构最大化提升其性能

当更多的中断出现时,优先权较低之中断的延时随固定性的下降而增加。一个50 周期的任务可能多次被中断,并最终需要数百乃至数千个周期来完成。这一点十分重要,因为并非所有的中断都具有高优先权,一切都是相对性的。

固定性直接影响到响应性、可靠性和精度。当开发人员确切知道延时是50或500个周期,便可以在处理时可将之考虑在内。不过,如果延时介于50到500个周期之间,即便是最优秀的开发人员,所能做的也不过是假设一个典型延时(如200个周期)数值,然后把所有的偏离视为误差。此外,最坏的延时情况有可能出现在濒临实时期限的极值,威胁到系统的可靠性。

通过DMA控制器和事件系统来减少同时发生的中断(即便是低频中断),可以大大提高系统的固定性并减小延时,而更高的固定性还有助于精度等其它重要因素的提升。

获得更高的精度

下面以一个电源管理任务在驱动电机等大负载时实现交流电源效率的最大化为例,来说明固定性如何影响精度。因为大部分可用能量都在电压处于峰值并与电流同相时供应,所以这时系统的电流消耗量应该最大。反之,电压越接近零(即过零点),可用电能就越少,而效率也越低。利用功率因数校正(PFC),通过接入和断开大电容,调节负载保持交流电流和电压同相,便可以提高功效。

比较器一般用于过零检测,当电压下降至设定阈值以下或上升至阈值以上时,比较器便会接通。相对于使用比较器触发中断并驱使CPU开关电容的情况,事件系统可以把比较器事件直接发送到定时器/计数器输出,无需CPU干预即可控制开关。

低优先权任务(如PFC)的中断延时可能需要数千个周期,而具体延时取决于有多少个优先权更高的中断同时发生。延时较大意味着电容会晚于最佳时刻开关,这会显着降低总体效率。相比之下,事件路由的延时最多两个周期。

当把上面的数字跟微控制器的时钟频率一同考虑时,便会发现如果微控制器的时钟频率为 32MHz,一个双周期延时所引入的误差其实微不足道(2/32M);而数千个周期的延时则可能大大影响高频任务(它们本身也需要每隔数千周期才会被处理)的精度。值得注意的是,若中断是由优先权较高的任务发出的,该延时可能降至50个周期左右。不过,这样一来会导致根据精度要求而不是根据系统功能的重要性来分配优先权,而且这只是把缺乏固定性引起的误差转移给了其它任务而已。

更高的精度在产生信号时也起着关键的作用,这里所指的并非单纯的信号采样。以创建100kHz波形为例,利用中断,波形的精度将受相对于信号速率的可变延时的影响,并根据任务切换和已堆积的其它中断数量而变得稍慢或稍快。注意,当波形平均而言准确时,在许多情况下,影响只来自是两个连续样本之间的相对差异。

高频信号处理

在大量嵌入式应用中,信号产生成为了一个越来越普遍的任务。信号用于产生声音、管理电压转换调节器、控制工业应用中的致动器,以及实现无数其它功能。信号的频率越高,采用中断时CPU上的负荷就越大,其他任务延时增加的可能性也越高。

对于发生频率较高的事件而言,CPU负荷是一大考虑因素。例如,高速传感器必须在下一个样本准备好之前进行采样,以防丢失数据。以一个流量计多轴定位系统或一个拥有每秒采集200万个样本采样速度的快速精确测量能力的仪表系统为例,单是采集样本,每秒便消耗了数十到数亿个周期。而若采用一个事件系统和DMA控制器,所有这些周期都可从CPU卸载,而且这些样本还会被实际处理,而不是简单地缓存。即使只是一个仅需要50个周期来完成、需要任务切换支出的简单任务,也能够从CPU卸载一亿个周期。鉴于这个原因,许多系统都使用独立的微控制器来管理各个高频传感器或电机。

对于频率较高的任务,事件系统和DMA控制器还能够实现以下事项:

• 精确的时间戳((TIme-stamping):为采样加上时间戳让开发人员能够使信号更好地与外部事件同步。在双周期延时的情况下,时间戳远比标注中断更精确,并可省去后者达数千个周期的延时。

• 过度采样:提高传感器分辨率的其中一个方法是过度采样。譬如,把计数器除以16,可以使采样样本数目增加到16倍,从而提高传感器的总体精度。由于CPU 没有直接参与样本的采集和存储,故有可能出现过度采样,而无太多惩罚。

• 动态频率:某些应用只在某些时间或特定工作条件下才需要较高的感测精度。例如,水表在水流速度快速变化时,采样频率会较高;而在流量被切断或流速稳定时,又回复正常频率。采样频率不但易于调节,而且还不会影响即时响应能力。

• 降低堆栈大小:减少并行中断数目的另一个好处是能够维持较小的堆栈。由于每一个中断都必须通过在堆栈中增加数十个寄存器来执行环境信息保存,因此消除了好几个环境保存层,显著减低所需堆栈的大小,这将让应用能够使用更少的RAM存储器。

• 抗扩展能力:鉴于不同微控制器支持的外设数目不同,同一应用的中断数目可能随产品价格而各有不同。即便使用同一个微控制器系列,支持更多功能的较高端系统会有更多的中断,降低了总体固定性。因此,把设计移植到集成度更高的微控制器,可能会影响信号延时乃至采样和输出的精度。

• 实现简易软件改变:由于事件处理减少了CPU干预,所以系统可在不会影响实时响应的情况下实现软件改变。即便需要更多的CPU时间来处理额外的功能,事件处理和响应时间也将完全相同。否则,就很难在产品使用寿命期间为即时应用实现软件的改变。

自主控制

一个嵌入式微控制器可能要执行无数个任务来降低功耗、提高精度以及改善用户体验,而许多这类任务只不过是监控或是检测单个数值。例如电池监控器进行监测,直至电压降至某个数值以下。然后,系统就触发关断操作,在仍有足够电量时保存应用数据。

提升用户体验常常是许多消费类产品的主要卖点。例如,事件系统能够加快系统对唤醒按键或外设输入的响应速度,在两个周期内就可以做出反应。如果与采用中断的响应性比较,由于中断需要系统返回到工作模式,因此就降低了能效。基于这个原因,开发人员常常延长定时器的时间间隔,以致降低了响应性。

若利用中断,对于CPU处理能力而言,执行这类任务的成本太高,而且会增加延时,降低固定性。而采用事件系统和DMA控制器,开发人员就能够避免CPU执行这些功能。这不仅可减少系统必须管理的中断数量,而且还能简化任务的实现和管理。

例如,在一个在特殊工作条件下向用户发出警示信息的应用中,预先设置的声音文件可以存储在缓存中,再利用DMA通过适当的外设馈入到扬声器,而利用定时器,事件系统就可以确保44,056KHz的准确数据率。此外还有一个额外的好处,因为频率准确且稳定,声音保真度也得以提高。从性能角度来看,只要配置了DMA和事件系统,CPU就完全不用干预播放任务了。

说这些任务变得更“自由”可能显得有点夸张。不过,以这种方式执行这些任务,的确使其能够适用于更宽范围的应用。协处理器、DMA控制器和事件系统的结合能够释放控制器,让它只进行信号处理,而不必把大部分资源消耗在信号的周期密集型采集工作上。因此,CPU得以保存大部分处理能力进行信号处理。这样一来,就可以利用单个控制器管理多个高频任务。这也简化了系统设计,使用户能够以更低的成本在单个微控制器上执行更多任务,更容易实现多个信号之间的互连性,并提高能效。

对许多应用来说,能否支持多个任务可成为一项重要的产品差异化指标。例如,采用了DMA控制器和事件系统的电机控制应用,就能够使微控制器释放出足够的资源,使开发人员能够以在不增加系统材料成本的条件下实现PFC等先进功能。

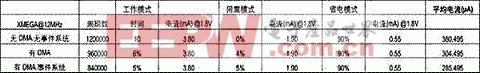

除了通过卸载中断来提高微控制器的性能和能力之外,事件系统还能够把功耗最低降至 1/7(具体数字取决于应用)。表2所示为一个需要每秒120万周期的应用的功率相关数据。在12MHz时,微控制器只有10%的时间在工作模式下,其余时间都处于待机模式。执行DMA控制器和事件系统可以卸载大量CPU每秒必须执行的周期数,使微控制器进入闲置或睡眠模式。鉴于工作模式下的耗电量远大于闲置睡眠模式下的,就算工作模式只出现少许百分比变化,所能节省的功率也可以是相当可观的。

表2 一个需要每秒120万周期的应用的功率相关数据

总结

架构方面的改进提高了CPU的总体能力,使得嵌入式微控制器系统性能不断提升。协处理器能够从CPU卸载已详细定义的计算密集型任务,DMA控制器可把整个系统的数据移动任务从CPU中解放出来,而事件系统可解决有关多个由频率触发中断的瓶颈问题。通过减少系统必须处理的并行中断的数目,开发人员能够提高系统固定性,从而降低延时,提高信号的分辨率和精度,改善稳定性和可预测性,并增强系统可靠性。这样一来,设计人员不但使用单个微处理器就能够执行以往需要多个微控制器才能完成的工作,而且还可降低系统的成本和功耗。

评论