基于LPC2134的多道脉冲幅度分析器设计

0 引言

核能谱辐射测量技术是一种综合性很强的技术,是核探测技术、电子技术、计算机技术等多学科相互交叉渗透的产物。具有现场、多元素快速分析等特点。核能谱辐射测量技术已经不仅用于核研究,也在地质学、医学、环境学、生物学、化学、考古学等学科扮演着越来越重要的角色。由于闪烁记数器、半导体探测器等核辐射探测器输出的脉冲信号幅度和入射粒子的能量成正比关系,因此,测量这些脉冲的幅度,就可以知道辐射的能量。然而,脉冲幅度的测量在核能谱辐射探测中则是一个重要问题。

多道脉冲幅度分析器不仅能自动获取能谱数据,而且一次测量就能得到整个能谱,因此可大大减少数据采集时间,与此同时,其测量精度也显着提高。自从20世纪50年代以来,多道脉冲幅度分析器发展迅速,现在已成为获取核能谱数据的通用仪器。

传统的核地球物理数据采集系统在硬件上大多采用分离元器件以及8位单片机来设计,故其功耗大、设计复杂、存储数据的内存容量小、数据传输速率低并且难于调试;而在软件设计上也多采用冗长繁琐的汇编语言来实现,设计效率低、可移植性差、性能难以保证。随着电子技术的发展,一些新型低功耗集成电路、ASIC集成电路、微处理器技术、计算机技术的不断引入,使核地球物理数据采集系统的功能日益完善和强大,也为核地球物理数据采集系统向轻便化、智能化、微机一体化以及网络化等方向发展提供了必要条件。

多道分析任务是将被测量的脉冲幅度范围平均分成2n个幅度间隔,然后测量幅度在每一个幅度间隔内的输入脉冲个数,最后得到输入信号的脉冲幅度分布曲线。其测量采用的是计算机技术中的A/D模数变换及数据存储技术。

在计算机的存储器中开辟一个数据缓冲区,数据缓冲区内有2n个计数器,每一个脉冲幅度间隔在数据缓冲区内部有一个对应的计数器。多道脉冲幅度分析时,可在微处理器的控制下,将被分析的脉冲信号首先送往模数变换器,经A/D变换形成一个代表脉冲幅度的数字量(道址)。然后用微处理器将该数字量变换成所对应的计数器地址。并使该地址对应的计数器内容加一(反映该道计数加一)。这样,经过一段时间的测量,存储器内计数器缓冲中各计数器计数的多少就可反映输入脉冲的幅度分布。

1 多道脉冲幅度分析器结构

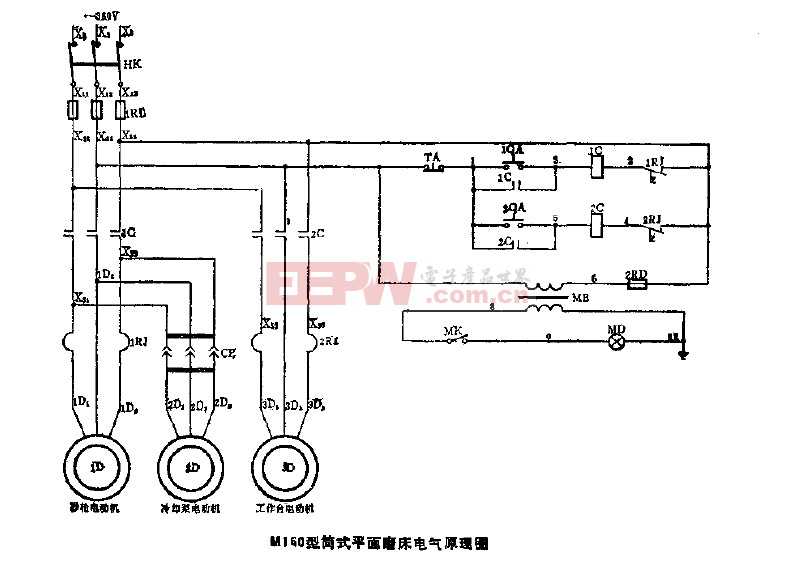

一台完整的核地球物理仪器通常可分为两部分:核辐射探测器和嵌入式系统。而多道脉冲幅度分析器是嵌入式系统的核心部分。多道脉冲幅度分析器一方面采集来自放大器的信号并进行模数转换,同时存储转换结果;另一方面将存储的转换结果进行数据分析,并直接显示谱线,或通过计算机接口送给计算机进行数据处理和谱线显示。

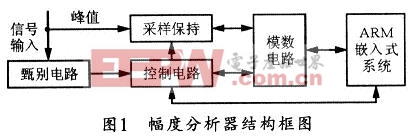

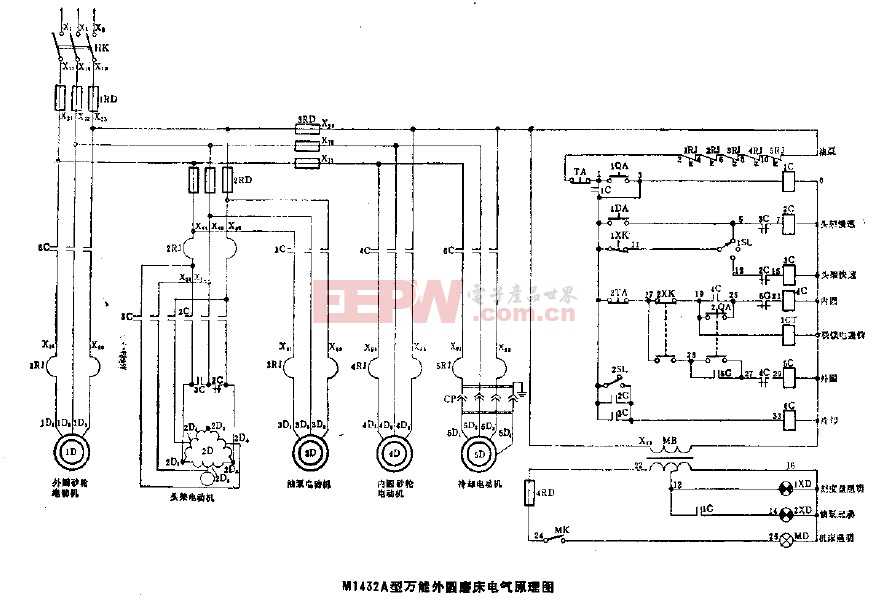

本文介绍的多道脉冲幅度分析器的设计结构框图如图1所示。脉冲信号在通过甄别电路和控制电路时,甄别电路给出脉冲的过峰信息,并启动A/D转换。A/D转换电路则可对脉冲信号峰值幅度进行模数转换,并将转换结果存储在片上Flash中,然后由微控制器进行相应的数据处理。

2 多道脉冲幅度分析器硬件设计

2.1 脉冲线性主放大器

多道脉冲幅度分析器由甄别电路、控制电路、采样保持电路、模数转换电路、ARM嵌入式系统组成,其控制核心为嵌入式系统。它的基本功能是按输入脉冲的幅度分类计数。多道脉冲幅度分析器将能够分析的脉冲幅度范围分成多个幅度间隔,幅度间隔的个数就是脉冲幅度分析器的道数,幅度间隔的宽度就是脉冲幅度分析器的道宽。道数越多,幅度分布分析的越精细,各个道的计数相应减少,需要测量的时间就要加长,硬件电路也随之复杂。因此,不应盲目追求道数。通常要求,在幅度峰的半宽度范围内应有5~10道。对于采用NaI探测器的多道能谱仪,由于它的能量分辨率比较差,往往128道至256道就能满足测量要求。而对于半导体探测器,则需要1024~8196道。本文使用半导体探测器并采用12位AD转换器,共有4096道,但采用并道的方式来显示1024道。

主放大器应放在前置放大电路和甄别电路之间,但需要增益调节来补偿核辐射探测器输出脉冲幅度的变化。由于探测器输出的脉冲信号幅度比较小(为几十毫伏至几百毫伏),脉冲宽度比较窄,因此。为了能进行信号幅度分析,实现能谱测量,通常需要用脉冲线性放大器将脉冲信号进行幅度的线性放大与脉冲成形。针对脉冲特点,要求放大器具有以下技术指标特性:

首先是放大倍数应按放大器的输入脉冲幅度和所要求的输出幅度来确定。因为前放输出的电脉冲信号幅度一般可以调至几百毫伏左右,而放大器输出脉冲幅度在1~5V范围内,所以其放大倍数应在10倍左右,考虑到前置放大器输出的信号幅度有差异,其放大倍数应可调试。

其次是放大器的频带宽度。由于前放输出的脉冲宽度会受有关电路影响,一般为几个μs,因此,要求放大器的频带宽度为1~2MHz。

第三是放大器的噪声。考虑到来自前放的信号幅度比较小,要求选用的放大器的输入噪声应尽可能的小。一般地,选用低噪声的运算放大器组件可以有效减少电路内部固有的噪声。

另外,诸如放大器的输入阻抗、抗计数过载、放大器的稳定性、功耗等,在电路设计和调试时也应予以考虑。由于α脉冲信号通过整形后大概有1~2个微秒的脉冲宽,γ脉冲信号通过整形后大概有3~5个微秒的脉冲宽,所以,在选用运算放大器时,要考虑到运放的转换速度。本系统的运算放大器选用CA3140,该器件具有输入阻抗高、噪声低、功耗小、温漂小等特点。

2.2 峰值检测电路

峰值检测电路由甄别电路和控制电路两部分构成,甄别电路的作用是检测信号时序,控制电路则根据甄别电路的时序对模拟开关、ADC转换进行控制。控制电路必须跟甄别电路的时序严格结合在一起,才能完成峰值检测任务。

由于核辐射探测器输出的脉冲信号幅度和入射粒子的能量成正比,因此,测量这些脉冲的幅度,就可以知道辐射的能量。可见,脉冲幅度测量技术在核能谱测量中是一个重要的问题。甄别电路需要解决三个与信号相关的信息:一是超过阈值信号的信息;二是过峰时间信息,即启动ADC转换的时间信息;三是ADC完成转换的时间信息。甄别电路中也存在三个关键问题,研究中要予以注意:

首先,由于放大器输出的α和γ射线脉冲宽度比较窄(约1μs到5μs),而本系统选用的ADC转换速度为10μs,所以,要对脉冲信号峰值进行峰值展宽。采样保持电路要求采样速度快,以使保持时间能达到ADC采样时间指标。

其次,由于脉冲信号的随机性,为了防止信号来的过密而引起漏计,本系统采用10μs转换速度的ADC,所以,从理论上分析,如果两个信号相隔10μs内,则会引起漏计。而由于CPU处理速度等问题的存在,实际上,这个时间间隔可能长3~10倍,即在30~100μs之间(根据CPU处理速度及代码量而定),甚至更多,也就是说,实际信号出现这种情况的几率很少,所以,可以忽略这个问题。

另外,还要解决信号过密而引起的幅度信号错误纪录,而高能区的信号也可能被误计为低能区的信号,容易引起低能计数偏大而高能计数偏小的问题。

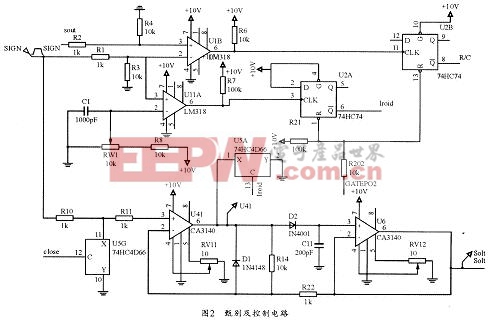

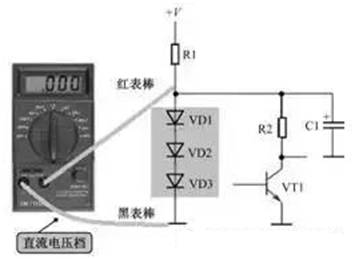

图2所示是甄别电路和控制电路的原理图。甄别电路的主要功能是完成过峰检测和去除信号噪声,可通过设定闭值将信号中能量小于阀值的噪声去。峰值通过后,提供信息给控制电路;控制电路的主要功能是完成对A/D读入/转换状态的控制。控制电路可由74HC74触发器构成。

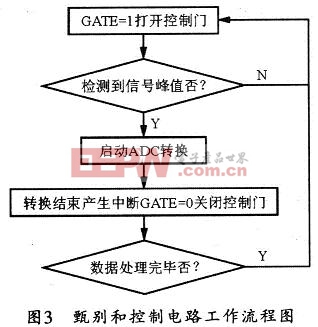

甄别和控制电路具体工作过程是,先由嵌入式微处理器控制中心给控制电路发出信号,以使控制电路处于工作状态,当脉冲信号到达多道脉冲幅度分析器后,由甄别电路进行甄别,并在过峰值后,将峰值通过的时间信息提供给控制电路;此后由控制电路启动模数转换,数模转换完毕,再由嵌入式微处理器控制中心产生中断,同时使控制电路停止工作,同时进行相应的数据处理;中断完毕,再由单片机发信号使控制电路重新处于工作状态。

采样开始时,先由ARM通过控制74HC74来启动A/D,然后,使U2A的RD和U2B的RD及SD端输出高电平,控制电路处于接收信号状态。当信号上升沿的能量低于设定的闭值电压时,U2A的CLK端为低电压,此时,U2A的RD和SD端均为高电平,输出端5脚保持原来的低电平不变。当信号上升沿的能量高于设定的闭压值时,U2A的CLK端为高电压,输出端5脚输出高电平,启动U2B。当脉冲没有达到峰值时,比较器U1B的同相输入端电压低于反相输入端电压,6端输出低电压,当过峰后,6端输出高电平,R/C输出低电平以启动A/D转换。转换完毕后,由ARM重新控制A/D进行下一个脉冲信号的采集。甄别电路和控制电路的工作流程如图3所示。

2.3 模数转换电路

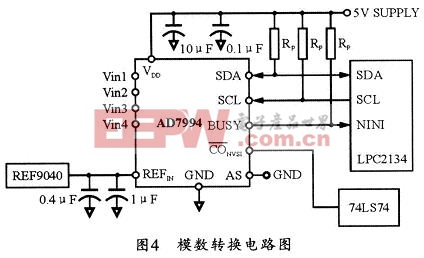

模数转换电路的作用是将模拟量转换成数字量,并将转换结果反馈给微控制器。多道脉冲幅度分析器主要用于快速、高精度地对输入的核脉冲信号进行采样,并将脉冲的幅度值转换成微控制器所能够处理的数字量。模数转换电路作为多道脉冲幅度分析器的关键部件,其性能的好坏直接影响整个系统的能量分辨率和转换精度等参数。综合对多道脉冲幅度分析器的ADC芯片的主要性能(如转换速度,功耗,转换精度)等考虑,本系统选用AD公司的AD7994,并在实际工作中采用“并道”的方法,每4道并作l道,则道宽非线性即可降低至原来的1/4。这种方法可降低由于ADC本身造成的非线性误差。其具体电路设计见图4所示。

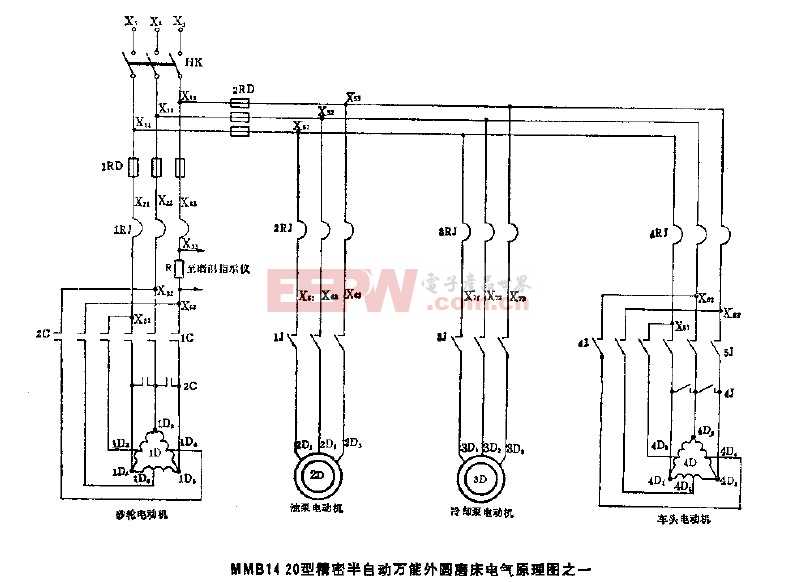

2.4 ARM微控制器外围电路设计

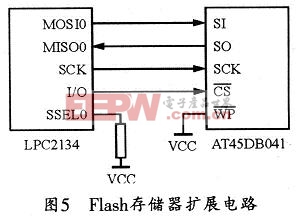

LPC2134是具有全双工通信能力的串行外设接口芯片(SPI)。一个SPI总线可以连接多个从器件和多个主器件,但是在同一时刻,则只允许有一个主机操作总线。本系统利用SPI接口来扩展Flash存储器。Flash存储器选用ATMEL公司的AT45DB041。ARM与串行Flash芯片AT45DB041的连接电路如图5所示。

本系统中,ARM工作在主机方式。由于ARM工作在主机方式时,若SSEL引脚为低电平,则将禁止SPIO模块工作。所以,为了系统可靠的工作,虽然这里该引脚未用,仍需将它通过上拉电阻接在电源上。串行Flash芯片AT45DB041的CS片选端由ARM控制。WP为写保护端,若使能,则存储器的前256页将不能擦除重写。由于本系统不需要此功能,因此,此脚直接接高电平。由于微处理器的存储容量有限且运算功能不强,故在对数据进行较复杂的处理时,往往需要借助计算机系统。因为串行通讯具有所用传输线少,适合于远距离传输等特点,所以本系统采用串口来连接计算机和微控制器。串口通信的硬件电路如图6所示。串口信号TXD和RXD直接和LPC2134的串行口相连接。

评论