数字信号完整性和信号恢复

数据通信和与无线能信有关的数字信号处理对带宽的需求日益增长。日超激烈的产品竞争,促使电路设计工程师考虑使用廉价的方案以尽可能高的速率传输数字信号。与往日侧重远距离传输信号时对信号完整性和信号恢复的考虑不同,板间、芯片组之间广泛使用的高速数据连接侧重于廉价连接时的信号完整性和信号恢复。

信号完整性问题

当试图在一定的距离上连接高速信号时,例如在机房之间传输38Mbps数据或在相邻机架之间传输2.5Gbps信号时,模拟效应对数字信号的影响均可简单归结为信号完整性问题。细分则可分为定时抖动、逻辑电平误触发和数据序列位间串扰。由于信号摆幅和逻辑电平判决门限的下降(因信号传输造成信号幅度衰减,需人为调低逻辑电平判决门限。),耦合到信号中的噪声会造成严重的抖动、误触发和串扰、与之相关的效应被定义为电磁干扰。

参考图1,实现信号完整性恢复的信号处理方式有均衡补偿接收量化、时钟一数据恢复和利用弹性存储器与参考时钟再生数据序列3钟。这3种处理方式分别针对不同模拟效应的影响,可根据实际的信号特点组合使用。

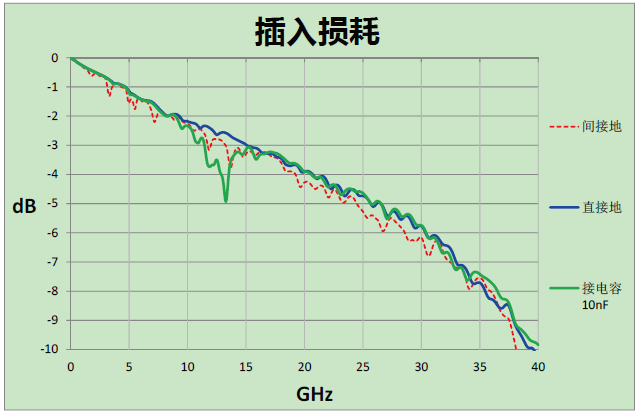

均衡补偿接收量化电路补偿传输线路的衰减,以及在高低频提供不同的增益均衡传输导致的信号失真。这部分电路实现基本的信号幅度判决和信号幅度恢复,主要改善信号经传输后的判决性抖动、误触发和串扰,对是否可有效地传输高速数字信号起关键作用。

再生数据序列时的抖动参数将由参考时钟抖动传递确定,先入先出FIFO弹性存储器暂存由于低频抖动引起的滑差位,一般是在多次级连传输后,由数据流提取的时钟相对于系统时钟出现较大低频抖动时再生数据序列。

MAX3800自适应传输线均衡收发器

MAX3800内部包括一整套完整的CML信号自适应均衡补偿接收量化电路和一套CML线缆驱动电路。使用一对MAX3800可以在30m同轴电缆或2mBPS微带线上有效传输3.2Gbps的数字信号。图2是MAX3800判决和恢复CML信号的实例。MAX3800内部电路包括一个针对集肤效应提供频率响应补偿的放大器和根据信号功率频率分布调节频率补偿的控制电路。配合一个限幅放大量化单元,可自适应接收不同线缆长度和类型、不同速度的CML数字信号。

评论