AD630实现低成本锁入放大器

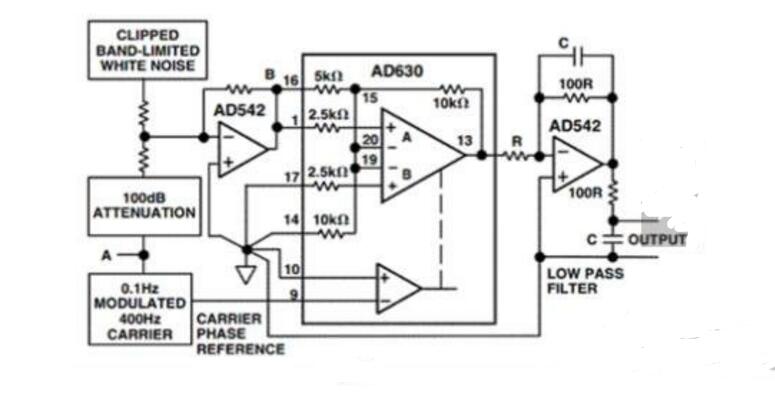

本例中的电路采用Analog Devices公司的AD630平衡调制解调IC实现了一种简单的低成本锁入放大器。该器件使用激光微调薄膜电阻,这带来了很高的准确性和稳定性,并因此产生了一种灵活的换向体系结构。它可用于同步检测等先进的信号处理应用。如果知道信号的频率与相位,那么即使存在振幅大得多的噪声源,该放大器也能检测出微弱的AC信号。

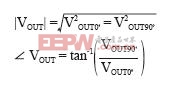

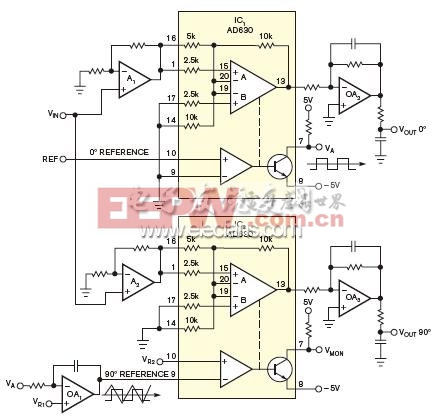

作为模拟放大器,AD630显示了输入电压信号在某个狭窄频带内的分量,该频带围绕基准信号的频率。 AD630输出端的低通滤波器使你能获得关于微弱信号振幅的信息,它原本被无关的噪声掩盖了。当输入电压与基准电压同相时,低通滤波器的输出VOUT具有最大振幅。相反,如果输入电压与基准电压正交,则输出电压在理想情况下将为0V。这样,如果可获得同相基准信号和正交基准信号,则两个平衡解调器显示同相输出电压为0?,正交输出电压为90?。你可以计算模移和相移,方法如下:

两个AD630的增益为±2,并通过两个相同的放大器 A1和A2接收放大的信号VIN。在IC1的7号引脚,出现一个与基准信号同相的双极±5V平方信号。OA1把放大器电压积分,这产生了一个三角波,IC2的比较器把它与VR2电压做比较。

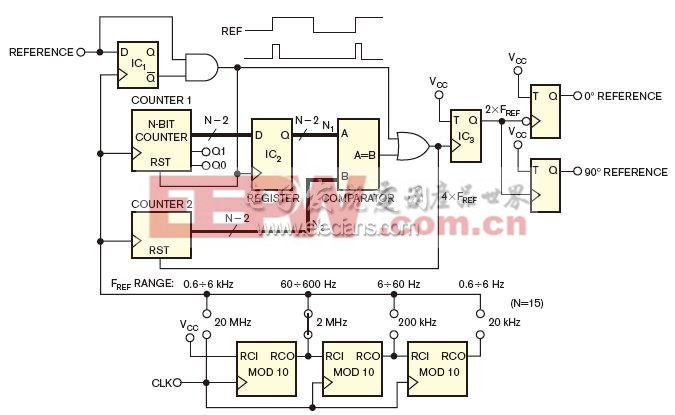

你可以使用不同方法来产生同相和正交基准信号。图2描绘了一条全数字电路,你可在小型CPLD中实施该电路,来产生图1中的0和90?基准信号。1号计数器以数字时钟脉冲的数量N的形式来测量基准信号时间,其中的基准时间可能不同于50%。在基准信号的每个正前沿,该计数器在N1=1处收到一条预设命令。D型双稳态多谐振荡器IC1产生这类脉冲。

图1,OA1把双极VA信号积分,并创建三角波。VR1和VR2获得关于VA的90。相移基准电压。

图2,你可在小型CPLD中实现这条全数字电路。

当基准时间超过N/4整数值的大约四倍时,就会缺少最后的EQ信号。为了克服这个问题,RST脉冲和EQ脉冲的“或”组合会在每个基准时间周期内产生四条几乎等距的命令。N/4整数除法是逻辑右移N1的两位,在最后的脉冲位置上产生最大误差3。T型双稳态多谐振荡器IC3产生一个信号,频率为基准信号的两倍。这样,准确度等于3/N1。

为使准确度至少能与AD630相比,1号计数器的N1输出将为最高值。但是,如果你希望N1达到较高值,那么对于给定的数字时钟频率,位数的增加会使最大基准频率下降。

低通滤波器相关文章:低通滤波器原理

尘埃粒子计数器相关文章:尘埃粒子计数器原理 锁相放大器相关文章:锁相放大器原理

评论