用表面贴装器件进行原理性测试

很多工程师和技术人员常常选用双列直插器件进行电路的原理性能测试,现有的做法是在带有过孔的玻璃纤维板上插入集成电路,使用绝缘导线点对点连接起来进行性能测试。然而,最近十年随着表面贴装技术(SMT)的快速发展,很多新型IC只提供表面贴装形式。在使用表面贴装器件进行测试时,安装比较困难,需要不同的材料和工具,但是,如果掌握了适当的技能将会变得容易许多。

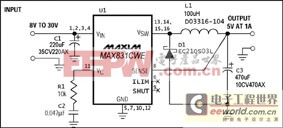

最基本的思路是在敷铜板上刻出细槽,形成矩形焊盘,并把这些器件横跨在这些细槽上。每一个矩形焊盘都是电路的一个节点。这种方法需要敷铜电路板和手动打磨工具,以及几种基本的工具。利用这种技术我们已经成功地测试了管脚间距为0.05英寸(1.27mm)的IC,而且对于0.025英寸(0.64mm)的IC也完全可以进行测试,所以对于SOIC封装的芯片和很多无源表贴器件,这种方法完全可行。为了进一步说明这种技术,图1给出了一个5W降压DC/DC转换器的设计实例。

图1:降压型DC/DC转换器

首先要给出一个完整的带有器件注释的电路图,其次要得到这些器件和实际的封装尺寸。画出电路中IC的管脚构成是很有必要的。使用一张白纸,两根不同颜色的铅笔,粗略地画出实际的电路布局并认真核查,用浅颜色的铅笔画出器件的轮廓,把器件摆放在节点上并相互靠近。所有器件的轮廓画好后,使用深颜色的铅笔画出连线把电路图中不同的节点分开,如图2所示。这些连线会围绕IC的焊盘和其它器件,器件将横跨在这些线的两端。将连线在铜板上刻成细槽,如果这些线都是直线或直角,刻起来会比较容易。图2中有一条飞线连接IC的第8脚和输出节点,如果在铜板上刻出这条线,则会破坏大面积接地或者需要在IC下面走线,这都不是好的布线方案。如果是多层板,这条线可以布在其它层上。

图2:线路板草图

图3:测试电路

为了把草图刻到铜板上,将铜板放平并把元器件按照草图的布局摆放,用钻子或其它尖状工具在铜板上按照草图的连线连接起来,并刻出细槽,然后,用刀片修理这些细槽,并进行打磨,清洗凉干后确认没有短路。接下来就可以安装器件并进行测试了。图3是最后完成的原型。

评论