直接数字频率合成器(DDS)应用的频率规划

dds基本知识与频率规划的意义

dds被定义为是一种由固定频率参考时钟源产生正弦波的数字技术。需要注意的是,参考时钟源的动态性能会直接影响到dds的输出频谱。dds有如下优点:

⑴ dds的输出频率是数字可调的,它具有小于1hz的频率分辨率。

⑵ 输出正弦波的相位是数字可调的,该特性对于那些需要多个dds互相同步的应用非常有用。

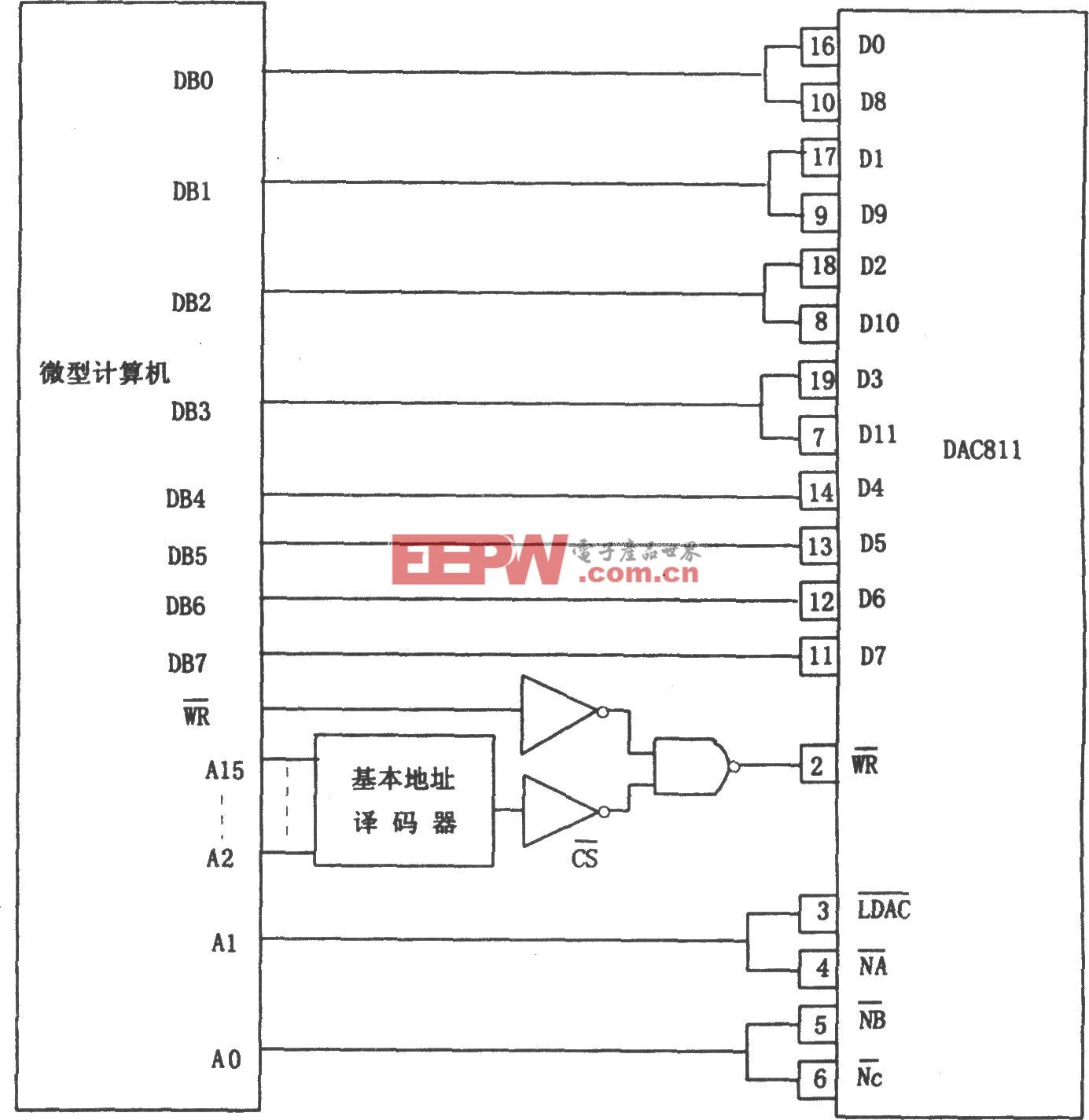

dds在结构上由三部分构成:⑴ 累加器;⑵ 角度幅度转换器,它将数字相位值转换为数字幅度值;⑶ 数模转换器。adi公司所有dds的dac都是电流输出形式。

dds频率规划是指在应用范围内提供最佳动态性能的一种尝试,对于许多应用来说,这就意味着在感兴趣的带宽内提供最大的无杂散动态范围,或者称作sfdr。为了获得最大的sfdr值,需要进行一些dds频率规划。一个好的频率规划首先是要根据应用所给定的性能标准选择合适的dds器件,然后规划并预算出dds的主要杂散源。

频率规划的主要内容及其操作

频率规划的内容主要有以下几方面:

1. dds主要杂散源的判定、内容判定、主要杂散源的框图。

2. dds参考时钟的重要性。

3. 利用简单的公式或模型预测dds所有杂散的频率位置。

4. 相位截断杂散,相位幅度转换杂散和参考时钟杂散的幅度估计。可以非常近似地得到这些杂散的幅度。

5. dac斜波杂散,用一个简单的模型进行模拟。

6. 数字开关的馈通信号杂散。

以上操作的目的是为了得到最大的sfdr。

频率规划一般需要确定四种杂散源,它们是参考时钟源,相位截短,角度幅度转换和dac非线性。每一种杂散源,它们的频率位置都是可以预测的。

参考时钟对dds输出的影响:

⑴ 参考时钟性能会直接影响到dds的输出性能。

⑵ 参考时钟的杂散频率会以相同的固定频率偏移传递到dds的输出。

⑶ 参考时钟的噪声会以相同的方式传递到dds的输出。

⑷ dds输出的参考时钟杂散或噪声的幅度会随着控制字的减小而减小。可以用下式表达: dbc=20log(ref clk/dds output)

⑸ 如果使用了内置参考时钟倍频器,参考时钟的所有噪声和杂散都会在pll环路带宽内按照下式放大:

dbc=20log(ref clk 的倍频数,数值为4~20)。

在知道了参考时钟的这些影响后,便能够很快地确定dds输出中的杂散会不会是由参考时钟引起的。

相位截短对dds输出的影响:

相位截短的原因是相位累加器在每个参考时钟周期中没有将所有的相位信息送给角度幅度转换器。相位截短对dds输出的影响:

⑴ 相位截短会对dds输出产生相位调制。

⑵ 丢弃的比特位的内容并不会被相位累加器丢弃。 ⑶ dds输出的频率分辨率由控制字的全字长决定,并不受相位截短的影响。

⑷ 相位截短杂散的频率位置是可以预测的。

⑸ 相位截短杂散的幅度与送入角度幅度转换器的相位字长n有关,可以表示为dbc=-6.02n

相位幅度转换对dds输出杂散的影响

这种杂散的幅度在dds输出杂散中居第二位。相位幅度转换对dds输出杂散的影响:

⑴ 有限的幅度分辨率在dac的输入端产生一个幅度误差信号,它调制dds输出。

⑵ 相位幅度转换引起的最大杂散的频率位置可以预测。这类预测方法是最新才找到的。

⑶ 最大杂散与基频的谐波有关。这是预测其频率位置的关键因素。

⑷ 最大杂散的幅度通常会比dac的量化噪声大约低12dbc或更多,具体数值取决于相位转换器的结构。

dac对输出信号杂散频率的影响

dac杂散主要是由dac的非理想开关特性和直流非线性引起的。它们会将这些杂散频率的能量分配到基波的较低次基波谐波中,这是预测杂散频率位置的关键。dac对输出信号杂散频率的影响:

⑴ dac通常是造成dds输出中最大杂散的因素。

⑵ dac非线性误差和非理想开关特性是造成最大杂散的原因。二者都会产生谐波失真。

⑶ 大部分的谐波失真能量都集中在基频的低次谐波上,主要是二次和三次谐波。 ⑷ 随着基频频率的增大,非理想开关特性成为引起谐波失真增大的主要原因。

一般地,得到最大sfdr的关键是找到参考时钟频率和频率控制之间的最佳比例关系。

数字开关馈通杂散

dds内部的数字信号的高摆率能够产生瞬时噪声耦合到dac的输出,但这种噪声耦合是不能消除的。同样来自外部噪声源的耦合也不能消除。它们都会影响dds输出的频谱。但这些噪声通常可以通过改善pcb的布线来解决。

数字开关馈通杂散的主要影响是:

⑴ 片上的数字时钟或外置时钟都会影响到dds的 输出频谱。

⑵ 这些时钟会对参考时钟进行相位调制,对dac输出进行幅度调制,从而引起基频周围的混叠分量。

⑶ 好的pcb布线有一定的改善作用。好的pcb布线包括使用大面积的接地层和电源层,分开模拟和数字电源,旁路电路尽可能靠近电源引脚。

⑷ 输入参考时钟和dac的输出为差分方式,可以降低共模噪声。

表1总结了可预测的影响dds的五个杂散源。

评论