基于FPGA的通用位同步器设计方案(一)

该同步器工作过程如下:外部控制器根据基带码元速率设置相应参数,通过外部控制器接口将控制、地址和数据信号分别送往分频器、环路滤波器和内部控制器。时钟电路分别提供采样时钟和FPGA 时钟,FPGA工作时钟在片内通过分频器产生所需频率的时钟,供FPGA 各模块使用。输入连续时间信号x(t) 经由独立时钟控制的ADC 进行采样,转换为8 位数字信号送至FPGA 内,符号化后变为有符号数字序列,送入内插滤波器模块。内插滤波器根据输入信号的采样值和内部控制器给出的参数μk,在每个插值时刻kTi 计算出最佳判决点的内插值y(kTi)。定时误差检测计算出误差μτ (n),输出至环路滤波器。环路滤波器依据当前的参数设定,滤除噪声并将误差信息送给内部控制器。内部控制器以NCO为核心,根据处理后的误差信息和设定的频率字参数调整插值时刻kTi,使之尽可能接近最佳判决时刻,并输出位同步脉冲BS,同时计算出误差间隔μk 送给内插滤波器,进行内插值计算,最终完成定时信息的恢复。

2 FPGA设计

2.1 整体结构设计

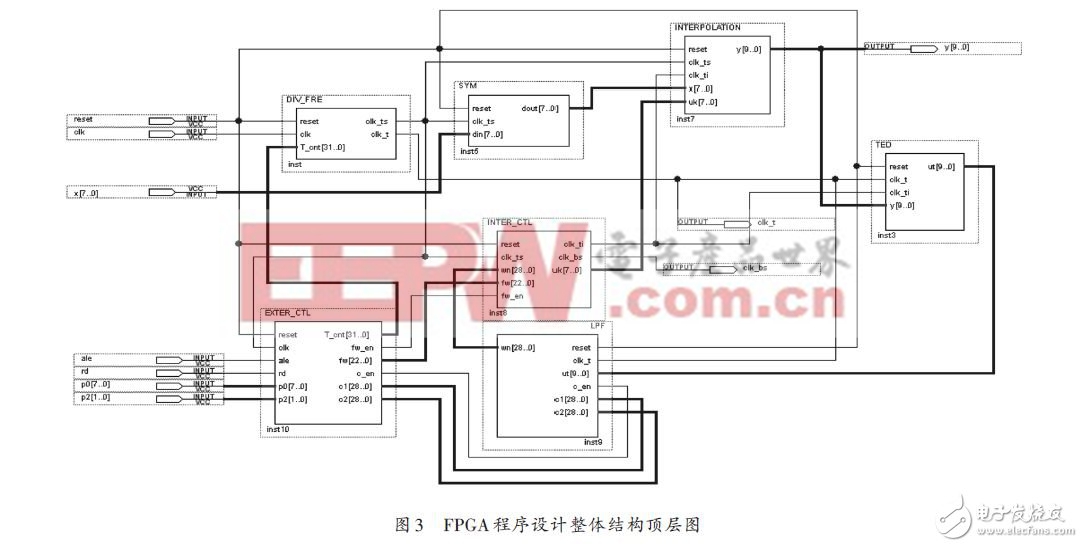

根据图2的算法结构,FPGA设计采用模块化方式,整体结构的顶层图如图3所示。

从图3可以看到,该设计包含分频器(DIV_FRE)、符号化(SYM)、内插滤波器(INTERPOLATION)、定时误差检测(TED)、环路滤波器(LPF)、内部控制器(INTER_CTL)和外部控制器接口的时序电路(EXTER_CTL)共7个模块。其中,分频器由片外晶振提供时钟输入,分频后为片内其他模块提供相应时钟。其中码元时钟的分频系数可由外部控制器通过接口进行设置。符号化是将A/D采样产生的无符号数转换为有符号数,以便后续模块进行带符号的运算。

外部控制器接口的时序电路将外部控制器送来的控制信号(ALE和RD)、地址信号(P2.0、P2.1)和数据信号(P0口)、转换为FPGA 内分频器、环路滤波器和NCO的使能信号和参数,实现对位同步器各参数的设置。

分频器、符号化和外部控制器接口模块实现较为简单,不再赘述。而内插滤波器、定时误差检测、环路滤波器和内部控制器的实现较为复杂,且本设计通过采用相应算法和改进结构,实现了位同步器的通用性。本文将详细阐述这些模块的设计。

2.2 模块详细设计

2.2.1 内插滤波器设计

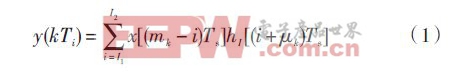

内插滤波器是完成算法的核心,它根据内插参数实时计算最佳判决点的内插值,即:

式中:mk 为内插滤波器基点索引,决定输入序列中哪些采样点参与运算,它由插值时刻kTi 确定;μk 为误差间隔,决定了内插滤波器的冲激响应系数[1].kTi 和μk 的信息由内部控制器反馈回来。

本设计的内插滤波器采用基于4 点分段抛物线多项式的Farrow结构实现。将式(1)变换为拉格朗日多项式,即令:

滤波器相关文章:滤波器原理

fpga相关文章:fpga是什么

滤波器相关文章:滤波器原理

电源滤波器相关文章:电源滤波器原理

数字滤波器相关文章:数字滤波器原理 锁相环相关文章:锁相环原理

评论