如何减轻EMI的电路设计方法

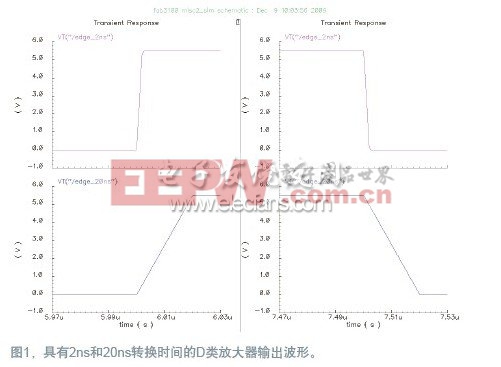

用于缓减EMI辐射的一个方法是减低放大器输出的转换速率(slew rate)。图1所示为时域中的一个例子,其上方迹线有2ns的上升和下降时间,而下方迹线有20ns的上升和下降时间。

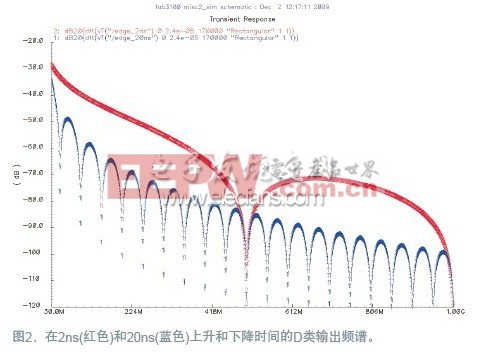

转换速率的减小(这里的因数为10) 对于D类放大器产生的辐射能量有着显着的影响。图2 显示了两种波形的频谱,此时D类输出正处于静默(无音频,占空比=50%),开关频率为333kHz。可以看到贯穿于30MHz~1GHz之间的大部分频谱,其高频(HF)内容减少约20dB。在包含有FM广播接收电子设备(88MHz ~ 108MHz)手机或无线互联网电路(700MHz ~ 2.7GHz)的系统中,这可大幅减少EMI,从而降低了可能影响系统性能的风险。

图2清楚地显示了边缘速率控制(edge rate control,ERC)技术减少EMI的优势,不过代价是增加了损耗。首先是D类放大器提供的效率优势,主要来自于输出器件始终完全开启或完全关闭,因此输出器件中的瞬时耗散功率P= VI,在所有时间里基本上保持为零 (不同于AB类放大器,其功率器件的VI乘积从不为零)。在每次开关转换时引入(或增加)时间跨度,其间V ≠ 0,同时负载电流I ≠ 0,导致片上功耗适度增加,因而带来效率的降低。其次,一个非ERC输出级在本质上仅是一个大型逆变器(可能包括直通或短路冲击电流的缓减),而一个ERC输出级包含附加电路,能够调节上拉和下拉器件的触发电压,以便在输出端上产生期望的、受控制的转换速率。取决于所使用的方法,这增加了芯片面积(成本)和电流消耗(降低效率)。总的来说,由于增添ERC而产生的效率代价可能为1% ~ 2%。

扩频时钟

上述讨论的边缘速率控制(ERC)是一个有效的方法,可减弱在30MHz以上频率范围产生的EMI (也受限于FCC法规的限制),而D类放大器开关输出的基本载波频率和其落在30MHz以下范围的相关奇次谐波(方波),则不太好采用这项技术来处理。

为了减小D类输出频谱中的基音和泛音尖峰高度,可以在放大器的时钟电路中加入少量频率调制——也许调制指数在±5%左右,不会影响所放大音频信号的质量。针对调制信号源的特性有许多选择,一个常规作法是使用带有重复频率(全模式重复频率)的伪随机模式,其超出最高预期音频信号频率(通常为20kHz)一个适当的余量,这可防止产生可能落入音频频带的音调。

单边调制

可以采用一种附加方法来减少EMI,通过修改调制方案,当音频基带信号振幅变得足够大时,允许单边差分或桥式D类输出对停止切换。这本质上允许反向输出,一直持续到开关,以便进行全面调制,将输出信号保持在剩余间隔直至其最高峰值。此方案,在很大比例时间内(取决于音频源材料),仅有一个输出在开关,因而EMI(在那个时间内)减少了一半。这增加了优势,减少了由于功率器件门和其它寄生电容充放电带来的固定开关损耗。它还缩短了输出在ERC转换方面的时间,如上所述,该转换有少量的效率代价。此技术的缺点是放大器的整体前向增益会有些许降低,同样地,总体谐波失真(total harmonic distortion,THD)和噪声也有少量增加。

结论

D类技术的主要缺点是其固有的EMI,会对周边电子设

EMC相关文章:EMC是什么意思

评论