SPI4.2总线应用和调试

SPI4.2总线(System Packet Interface,系统间数据包接口)是一种速度高达10 Gb/s的芯片间互连总线,主要应用于ATM信元传输、POS(Packet Over SONET/SDH,基于SONET/SDH的包传输)和10 Gb/s以太网等高端场合。特别在通信领域,很多高端处理器和网络处理器,如Intel公司的IXP2800、Cavium公司的多内核处理器CN58xx系列、NetLogic公司的XLR732、Broadcom的BCM1480,几乎都集成了SPI4.2接口,以提高芯片的吞吐能力,适应通信产业朝着LTE(长期演进)发展的需求。还有众多的物理层芯片,例如Cortina公司的CS1331,可以将SPI4.2总线转换成8个千兆以太网接口。SPI4.2总线之所以被众多的高端芯片所采用,与其高速、灵活、可靠的特性是密不可分的。

1 SPI4.2总线基本原理

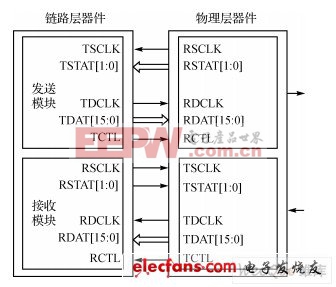

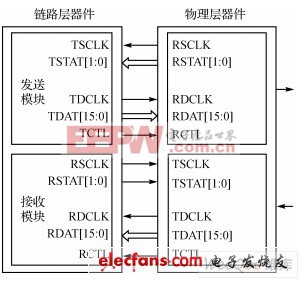

SPI4.2总线是一种芯片间的互连总线,连接芯片的链路层和物理层模块。其工作时钟是源同步双边沿触发时钟,至少为311 MHz。图1是使用SPI4.2总线连接两个芯片的示意图。可见,SPI4.2总线的信号在发送和接收方向完全对称而又互相独立,数据链路和状态链路分开,并且其时钟也是完全分开的。因此,该总线不仅适合于双向通道,而且适合于只收不发或者只发不收的单向通道。

图1 SPI4.2连接示意图

SPI4.2总线具有以下特点:

① 点对点互连,收发数据链路宽度为16位。

② 发送和接收模块的信号各分为两组,即数据信号和状态信号,分别对应数据链路和状态链路,每个链路具有自己的时钟。数据链路发送和接收数据,状态链路传输相应链路的状态信息。

③ 数据链路包含DCLK、DAT[15:0]和CTL三种LVDS(低压差分传输)信号。前面加“T”表示信号属于发送模块,加“R”表示信号属于接收模块。以发送模块为例,TDCLK是双边沿触发时钟,TCTL是控制信号,TDAT[15:0]承载了数据和控制信息。当TCTL为高电平时,TDAT[15:0]传送的是数据包;当TCTL为低电平时,TDAT[15:0]传送的是控制包。数据采用DIP4校验交织码。

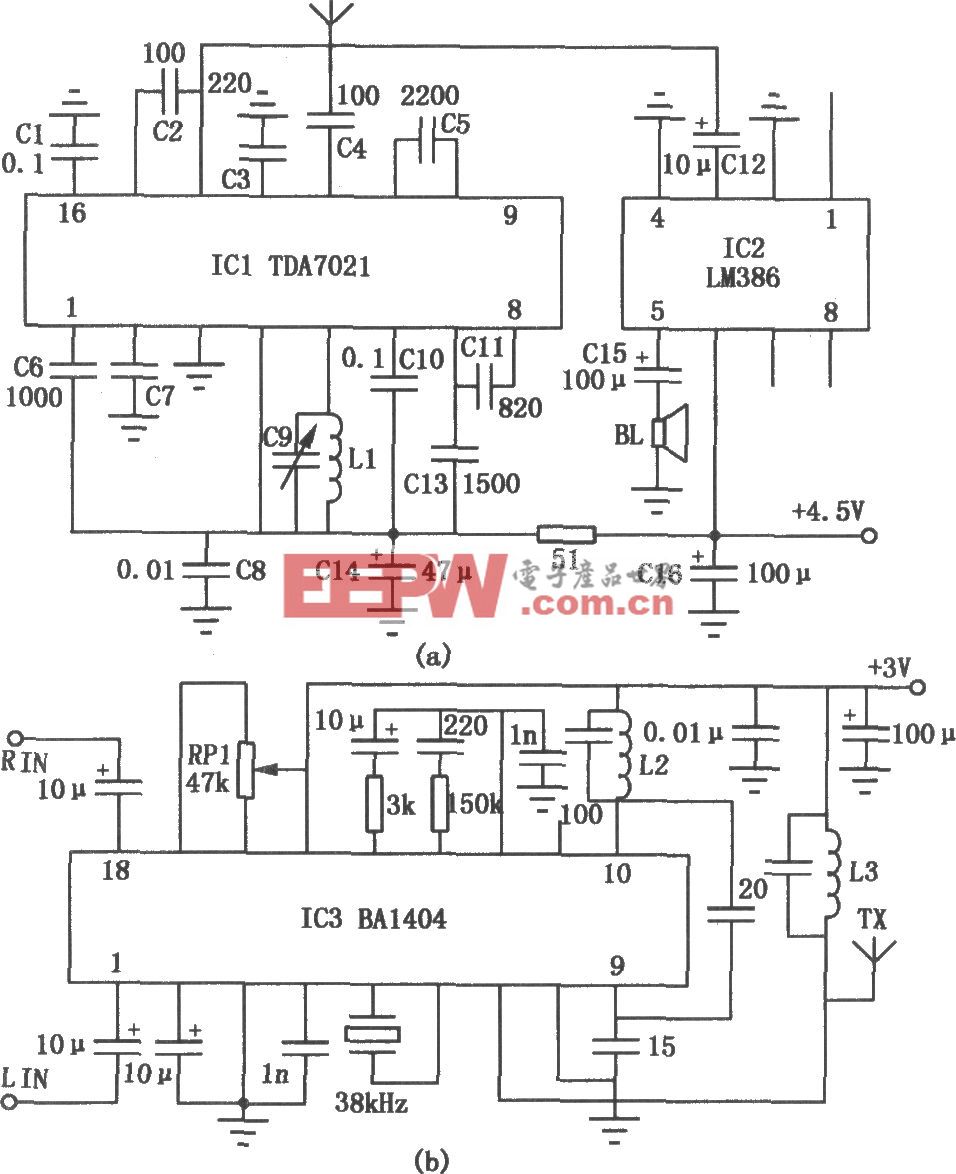

④ 状态链路包括SCLK时钟信号和STAT[1:0]状态信号,信号类型是LVTTL或LVDS。SPI4.2 发送时序如图2所示。如果选择LVTTL,则SCLK时钟频率是数据链路时钟速率的1/4。如果选择LVDS,则SCLK时钟频率和数据链路时钟频率相同。下文中均以LVDS为例进行阐述。状态链路主要用于流控。

⑤ 接收和发送模块都含有一个FIFO队列,用于缓存数据,队列长度由芯片设计而定。队列的状态信息通过状态链路周期性地发送,接收模块和发送模块的状态信息是独立的。状态信息附加了DIP2交织校验码,以提高传输可靠性。

图2 SPI4.2 发送时序

评论