基于BU-65170的1553B终端设计

关键字:内部资源;1553B终端;模式命令

Abstract: The internal registers and RAM resources of 1553B RT interface chip BU-65170 is described, and it introduced the methods of designing the hardware interface and software interface between BU-65170 and 16 bit single chip processor Intel80C196. The data communication between 1553B RT and BC is realized effectively and credibly.

Keywords: internal resources,1553B RT,mode code

1. 引言

MIL-STD-1553B总线最初是由美国在70年代为适应飞机的发展提出来的飞机内部电子系统联网的标准。MIL-STD-1553B具有高可靠性和灵活性,从而使得它的应用范围推广到卫星、舰船、坦克等领域。在我国,MIL-STD-1553B总线系统的应用正逐步深入,具有广阔的前景。目前,我们使用的1553B总线接口芯片主要是DDC公司的ACE(Advanced Communication Engine),常用的有BU-65170、BU-61580、BU-64843等。1553B终端系统可以使用8位单片机[1],16位单片机,32位单片机[2]来实现。本文选用BU-65170接口芯片,详细介绍了终端系统设计中关键的部分,即芯片内部寄存器和RAM资源,设计了基于Intel80C196单片机的硬件接口电路,完成了软件接口程序,最终实现了1553B终端RT与总线控制器BC之间高可靠的数据通信。

BU-65170芯片的功能特点

BU-65170由两个低功耗双端收发器、协议逻辑、存储器管理逻辑、处理器接口逻辑及 内置共享静态RAM和直接面向主微处理器的缓存接口等组成。BU-65170的特点包括:

a. 全集成化的1553B总线标准接口协议终端

b. 灵活的处理器和存储器接口

c. 内部具有17个通用命令寄存器, 共享RAM,可外扩64K 16RAM

共享RAM,可外扩64K 16RAM

d. 先进的RT特性:支持单消息模式、双缓冲模式和循环缓冲模式三种工作方式

e. 支持可编程非法化指令和可编程忙位指令

2. BU-65170内部RAM资源分配

BU-65170内部具有  共享RAM。在RT增强模式中,两个堆栈指针分配在固定的位置:0100H是堆栈指针A的地址;0104H是堆栈指针B的地址。0000-00FFH是256字的堆栈A空间,也是1553B接收信息描述符区,每个描述符占4个字,一共可储存64个描述符。描述符的四个字分别是块状态字、时间戳,接收数据块指针、接收命令字。

共享RAM。在RT增强模式中,两个堆栈指针分配在固定的位置:0100H是堆栈指针A的地址;0104H是堆栈指针B的地址。0000-00FFH是256字的堆栈A空间,也是1553B接收信息描述符区,每个描述符占4个字,一共可储存64个描述符。描述符的四个字分别是块状态字、时间戳,接收数据块指针、接收命令字。

0108-010FH是模式命令选择中断表,设置每一个接收、发送、广播接收、广播发送的模式命令时,是否产生中断。

0110-013FH是模式命令返回数据的固定地址,当RT接收到一个模式命令时,将储存于对应位置的数据自动返回给BC。

0140-01BFH和01C0-023FH分别是RT的A/B区域地址查询表。对于A区域,地址分为4部分0140-015FH分别对应子地址0到子地址31的接收数据缓冲区的首地址。0160-017FH分别对应子地址0到子地址31的发送数据缓冲区的首地址。0180-019FH分别对应子地址0到子地址31广播模式数据缓冲区的首地址。01A0-01BFH分别对应子地址0到子地址31的子地址控制字,可以设置数据缓存区的大小和工作方式,如:单消息模式、双缓冲模式和循环缓冲模式。

0240-0247H是忙位查询表,其中每一位分别对应子地址0到子地址31的忙状态,0表示不忙,1表示忙。当RT收到的消息对应的子地址为忙时,将向BC端返回状态字的忙位置1。

0300-03FFH是非法化指令查询表,分为4部分:0300-033FH对应广播接收非法化命令;0340-037FH对应广播发送非法化命令;0380-03BFH对应非广播式接收非法化命令;03C0-03FFH对应非广播式发送非法化命令。当RT收到非法化命令字时,将向BC返回对应的状态字。

0260-02FFH和0400-0FFFH为数据缓存区。这部分空间可以由子地址0到子地址31的子地址控制字设置每个子地址对应的数据缓存区空间大小和工作方式。

3. BU-65170与Intel80C196的接口设计

3.1 硬件接口设计

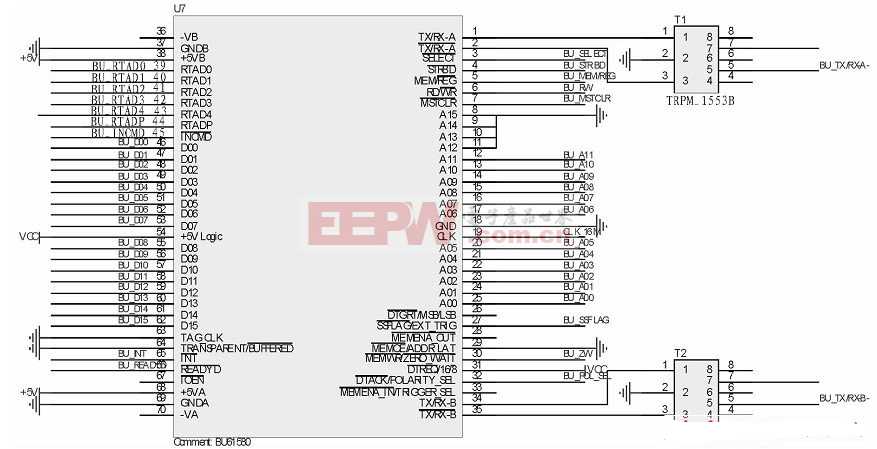

图1. BU-65170与Intel80C196的硬件接口图

本文采用16位处理器Intel80C196与BU-65170相连接。BU-65170的16位双向地址总线A0-A15与数据总线D0-D15分开,处理器Intel80C196通过地址总线A1-A12以字为单位访问BU-65170的内部寄存器和 的RAM。

的RAM。

Intel80C196处理器的数据线和地址线通过两片锁存器锁存,实现分时复用目的。地址总线高10位A6-A15通过地址译码得出BU-65170的片选信号以及片内寄存器和 RAM存储器切换选择信号

RAM存储器切换选择信号 。引脚RTAD4-0和RTADP通过跳线可以选择BU-65170的地址编号。芯片采用外部接16MHz晶振工作方式。BU-65170与Intel80C196之间的硬件接口如图1所示。

。引脚RTAD4-0和RTADP通过跳线可以选择BU-65170的地址编号。芯片采用外部接16MHz晶振工作方式。BU-65170与Intel80C196之间的硬件接口如图1所示。

4.2软件接口设计

BU-65170内部具有25个寄存器,包括17个通用控制寄存器和8个测试寄存器。其中,设置17个通用控制寄存器是软件接口设计的关键。

设置启动/复位寄存器,先进入复位状态;设置配置寄存器3,进入增强模式;设置中断屏蔽寄存器,使能消息结束中断;设置配置寄存器2,进入增强型RT存储器管理模式;设置配置寄存器3,增强模式允许。设置配置寄存器1,进入RT工作方式,开启RT。

主程序对1553B信息的处理采用中断处理方式。从BC端发送来的1553B命令有两种要求:不需要RT回传数据和需要RT回传数据。

a) 不需要RT回传数据

BC端发送命令字为非模式命令,要求RT接收信息,单片机终端收到信息进入中断程序,设置相应的任务标志,然后进入主程序,根据1553B接收信息描述符区中接收数据块指针,找到1553B接收数据缓冲区,然后执行这些数据对应的任务,然后在主程序循环等待下一次中断。

图2 (a)主程序流程图 (b)中断程序流程图

b) 需要RT回传数据

首先BC端发送命令字为非模式命令,要求RT接收信息,单片机终端收到信息进入中断程序设置任务标志,然后进入主程序,找到1553B接收数据缓冲区,执行相关任务,

并把需要返回给BC端的数据准备好,保存在1553B发送数据缓冲区,且将需要回传数据字个数保存到模式命令对应的地址单元,然后设置服务请求,将配置寄存器1中的第9位设为0。与此同时,BC端向RT一直发送空指令,得到相应的返回状态字,判断状态字的第11位,若为1,表示RT将数据准备好,BC向RT发送模式命令,命令编码为10000,即为发送向量字命令,要求RT发送消息。RT收到模式命令后,返回状态字,且将准备好的数据个数返回给BC;然后BC端再发送一次非模式命令,要求RT发送消息,数据个数为刚才收到的返回值。此时,BC端再次收到返回的状态值和RT回传的有效数据。基于BU-65170的单片机终端系统程序流程图如图2所示。

4. 结论

本文重点介绍了BU-65170接口芯片的内部寄存器和RAM资源,并且给出了基于BU-65170的MIL-STD-1553B单片机终端系统的硬件和软件设计方法。在多次的系统调试试验中,RT终端系统与BC总线控制器之间实现了高效,可靠的数据通信。该单片机终端系统对1553B总线应用具有普遍的实用性。

本文作者创新点:

1. 采用16位Intel80C196处理器处理能力强,增加系统可靠性,能适应地面和星上各种环境要求,且接口电路设计简单,实用性强。

2. RT数据回传过程中采用了模式命令方式,将回传字个数返回BC端,节约了系统处理器开销,提高了处理速度。

参考文献

[1] 任承志等. 基于BU65170与单片机系统的RT设计与实现. 微计算机信息. 2006年第22卷第6-2期

[2] 邓平科等. 基于ARM 的1553B总线应用. 微计算机信息. 2006年第22卷第9-2期

[3] 徐爱卿. Intel 16位单片机(修订版). 北京航空航天大学出版社. 2002.7 第2版

[4] DDC. MIL-STD-1553A/B ACE User’s Guide. 1999 Data Device Corporation.

[5] COMMENTARY OF MIL-STD-1553, NOTICE 2 User’s Manual[M/CD]. USA. Excalibur Corporation. 2002

评论