DSP应用系统中的硬件接口电路设计

关键词:DSP硬件接口电路电平变换

数字信号处理(Digital Signal Processing ,DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科,自DSP芯片诞生的二十多年来,其在控制、通信等领域得到了广泛的发展。在众多的DSP器件中,以TI公司的DSP应用最为广泛,本文以TI DSP为例介绍系统接口电路的设计。一个完整地DSP控制系统的硬件接口电路一般包括电平变换电路、仿真器接口JTAG电路、以及可扩展的硬件接口(如A/D、D/A、SRAM等)电路,而这些硬件接口电路是DSP系统工作的基础。

一、电平变换接口设计:

DSP系统是一个混合电压系统,存在着5V/3.3V混合供电现象:DSP芯片的I/O供电电压一般是3.3V,而外围芯片工作电压为5V,如EPROM、SRAM、A/D器件等。通常它们之间是不能直接相连的,设计中必须进行电平变换。

1、 在混合电压系统中,不同电源电压的逻辑器件接口时存在的问题

(1)加到输入和输出引脚上允许的最大电压限制问题。器件对加到输入或者输出引脚上的电压通常是有限制的。这些引脚上一般有二极管或者分离元件接到电源。如果接入的电压过高,则电流将会通过二极管或者分离元件流向电源。例如I/O为3.3V供电的DSP,其输入电平不允许超过电源电压3.3V,而5V器件输出信号高电平可达4.4V,它会向3.3V电源充电,持续的电流将会损坏二极管和其它电路元件。

(2)两个电源间电流的互串问题。在等待或者掉电方式时,3.3V电源降到OV,大电流将流通到地,这使得总线上的高电压被下拉到地,这些情况将引起数据丢失和元件损坏。必须注意的是:不管在3.3V的工作状态还是在OV的等待状态都不允许电流流向电源。

(3)接口输入转换门限问题。5V器件和3.3V器件的接口有很多情况,同样TTL和CMOS间的电平转换也存在着不同情况。驱动器必须满足接收器的输入转换电平,并且要有足够的容限以保证不损坏电路元件。而输出电平一般无需变换。

2、 在混合电压系统中,必须处理的信号电平配置

(1)5V TTL器件输出驱动3.3V TTL器件(LVC)输入。通常5V TTL器件可以驱动3.3V TTL器件的输入,因为典型双极性晶体管的输出并不能达到电源电压幅度。当一个5V器件的输出为高电平时,内部压降限制了输出电压,典型情况是VCC-2VBE,即约为3.6V,这样工作通常不会引起5V电源的电流流向3.3V电源。但是因为驱动器结构会有所不同,所以必须控制驱动器的输出不宜超过3.6V,以防万一。

(2)3.3V TTL器件输出驱动5V TTL器件输入。由于二者的电平转换标准是一样的,因此不需要额外的器件就可将两者直接相连。只要3.3V器件的VOH和VOL电平分别是2.4V和0.4V,5V器件就可将输入读为有效电平,因为它的VIH和VIL电平分别是2V和0.8V。

(3)5V CMOS器件输出驱动3.3V TTL器件输入。显然二者的转换电平是不一样的,但二者虽存在一定的差别,若设计时使用能够承受5V 电压的3.3V TTL器件,则5V器件的输出是可以直接与3.3V器件的输入端接口的。

(4)3V输出驱动5V CMOS输入。二者的转换电平标准是不一样的,3.3V器件输出的高电平最高值是3.3V,而5V CMOS器件要求的高电平最低值是3.5V,因此3.3V器件的输出不能直接与5V CMOS器件的输入相接,这种情况下就需要用双电压(一边是3.3V供电,另一边是5V供电)供电的驱动器,如使用TI总线收发器SN74LVTH245A(8位)、SN74LVTH16245A(16位)等。图1给出了利用总线收发器SN74LVTH245A的3.3V DSP芯片与5V EPROM的连接。

图1

另外电平转换还可用以下器件:

(1)使用总线开关。主要应用于McBSP(Multichannel Buffered Serial Port)多通道缓冲性串行接口等外设信号的电平转换,5V供电。常用器件:SNCBTD3384(10位),SN74CBTD16210(20位)

(2)使用2选1切换器。实现2选1,4.1V供电,主要适用于多路切换信号的电平转换,如双路复用的McBSP信号的电平转换等,常用器件为SN74CBT3257(4位)、SN74CBT16292(12位)

(3)使用CPLD器件。可以通过双电压工作的CPLD可编程器件实现电平之间的转化,如Altera公司的MAX7000S系列器件等。

二、DSP与JTAG接口设计:

同单片机控制系统一样,DSP应用系统也必须具有与仿真器连接的标准接口,通过这个接口用户可以通过PC机进行调试、下载应用软件到指定的应用板上。图2给出了DSP系统的JTAG接口与应用板中DSP芯片连接的原理图。在图中给出的是TI公司的IEEE1149.1标准的通用JTAG接口,其引脚的定义的顺序不同于一般的集成芯片的顺序,是从上到下、左右交替排列。JTAG引脚的功能定义如下:

EMU0: EMU0引脚,需要接3.3V上拉电阻。

EMU1: EMU1引脚,需要接3.3V上拉电阻。

GND:地。

PD(VCC):此引脚必须连接到DSP应用板的+5V电源端。

TCK:测试时钟引脚,该信号来自于仿真器。

TCK_RET: 测试时钟返回引脚。

TDI:测试数据输入引脚。

TDO:测试数据输出引脚。

TMS:测试模式选择引脚。

:测试复位引脚。

三、DSP的A/D、D/A接口设计:

DSP与外部模拟信号的接口主要包括A/D、D/A两大部分,而TI DSP内部大多已包含了A/D转换模块,所以在这里只介绍外扩D/A转换接口。

1、通过DSP片内SPI(串行外设接口)实现串行D/A接口

由于DSP内部包含有串行外设接口SPI模块,SPI 是同步串行外围接口,它允许1~8 位的串行比特流以特定的传输速率移进移出芯片,主要用于与各种外围器件进行通讯,这些外围器件可以是简单的TTL移位寄存器或是复杂的LCD显示驱动器或A/D、D/A转换子系统。SPI 接口很容易与许多厂家的各种外围器件直接相连。其中,MAX5120/5121是适合于SPI通信的D/A转换芯片。它是Maxim 公司生产的12位,具有两级输入缓冲区:输入寄存器和DAC寄存器。SPI总线上接收到的数据位首先进入到16位的移位寄存器,然后进入输入寄存器和DAC寄存器进行D/A转换。

MAX5120/5121与DSP的SPI接口连接进行DAC转换的电路如图3所示,其中DSP设置为主机工作模式,MAX5120/5121设置为从机模式。工作时,通过SCLK引脚接收外来时钟驱动,在此时钟下,从DIN引脚接收串行数据到移位寄存器中,并进行D/A转换,在OUT引脚输出模拟信号。图中,当开关S闭合到S1端时,为双极性输出;当开关S闭合到S2端时,为单极性输出。

2、DSP并行D/A接口

DSP对并行D/A接口芯片的访问形式是只写不读,下面介绍DSP与AD7837的接口方法。如图4所示电路,AD7837为12位D/A转换器,对每个内部转换器(A或B)来讲,完成一次D/A转换操作的过程是:首先将待转换的低8位数据送到AD7837,然后再写高4位,最后通过I/O引脚输出一个转换锁存信号到AD7837的引脚,从而启动D/A转换。地址信号A0和A1用来决定AD7837中的A或B转换器中的哪一个。

四、DSP与SRAM接口设计:

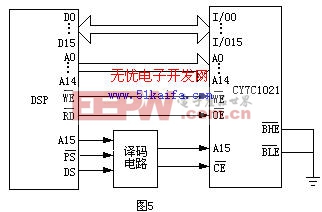

SRAM时DSP最常用的外围存储设备,它具有接口简单、读写速度快等优点,常用的SRAM芯片有IDT7128、CY7C1024、CY7C1021等。图5给出了CY7C1021与DSP的接口电路。

CY7C1021是高性能、16位、CMOS静态RAM,对其基本操作有两种:使能的同时进行读或写。当输入信号 和

和  同时为低电平时,写选通该芯片。当低字节使能位BLE变低时,选通低8位数据端口,即来自I/O引脚I/O1~I/O8的数据被写入到地址引脚A0~A15所指定的位置;当BHE变低时,选通高8位数据端口,即来自I/O引脚I/O9~I/O16的数据被写入到地址引脚A0~A15所指定的位置。

同时为低电平时,写选通该芯片。当低字节使能位BLE变低时,选通低8位数据端口,即来自I/O引脚I/O1~I/O8的数据被写入到地址引脚A0~A15所指定的位置;当BHE变低时,选通高8位数据端口,即来自I/O引脚I/O9~I/O16的数据被写入到地址引脚A0~A15所指定的位置。

当输入信号  和

和  为低电平时,同时迫使

为低电平时,同时迫使 变为高电平时,读选通该芯片。当低字节使能位

变为高电平时,读选通该芯片。当低字节使能位 变低时,存储器中指定位置中的数据将出现在I/O引脚I/O1~I/O8上;如果当高字节使能位 变低时,选通高8位数据端口,存储器中指定位置中的数据将出现在I/O引脚I/O9~I/O16上。

变低时,存储器中指定位置中的数据将出现在I/O引脚I/O1~I/O8上;如果当高字节使能位 变低时,选通高8位数据端口,存储器中指定位置中的数据将出现在I/O引脚I/O9~I/O16上。

从电路可知,每次读、写操作的是整个16位数据,不分高低字节。通过译码器电路将64KB的SRAM空间分为两个地址区间(由地址的最高位A15的值决定),即数据区和程序区,具体区间的划分由用户的译码方法决定,DSP可方便的对CY7C1021进行读写操作。

五、要注意接口电路设计时的时序问题

时序问题是任何数字电路设计所必须重视的问题。在低速数字系统设计中要着重解决的问题为时序的逻辑性是否正确,而在高速数字系统设计中除了要解决时序逻辑性问题外,还要着重解决时序的时延性问题。为保证DSP在规定的时间内正确读/写外部扩展器件,首先要选用高速器件,要求扩展器件的读/写周期小于DSP的机器周期的60%,否则要插等待周期,但这样DSP的高速特性就不能得到充分发挥。其次,要求扩展器件的总线接口电路的时延尽量小,否则需要另外插入等待周期。解决此问题的方法是尽量采用高速接口器件和单级接口电路。另外,在设计时一般还要用CPLD实现一些特殊的逻辑:如用来控制外设的驱动时钟、各种同步控制时钟(A/D转换、数字信号存取)以及存储器地址的产生等。使用CPLD实现,具有明显的优点:它可使时序关系整齐,延迟一致,易于修改,并且具有高集成、高可靠性。

六、结论

具体的DSP应用系统接口电路的设计,可能在性能指标、器件选取、外围电路设计等方面会有所不同,所以在设计DSP应用系统接口电路时,一定要根据具体情况综合考虑,仔细选取器件,合理布局布线,精心设计电路,才能达到理想的设计效果。

本文作者创新点: 给出了DSP应用系统的硬件接口电路的设计方法,介绍了接口电路在设计时须注意的几个问题

六、参考文献:

[1] TMS320 DSP Designer’s Notebook: Volume1,Texas Instruments, 2001.

[2] Texas Instruments,TMS320C54xx DSP CPU and Peripherals Reference,1999.

[3] 张雄伟 陈亮 徐光辉, DSP芯片的原理与开发应用(第3版),北京, 电子工业出版社, 2003.2.

[4] 徐文;王峻峰。基于DSP和AD7846的高精度控制系统。微计算机信息,2006 年第 17 期

评论