IC上电和关断(2):断电还是关断?

现代集成电路采用精密复杂的电路来确保其开启后进入已知状态,保留存储器内容,快速引导,并且在其关断时节省功耗。本文分两部分,提供有关使用上电复位和关断功能的一些建议。

本文引用地址:https://www.eepw.com.cn/article/201808/387436.htm断电还是关断?

当然是关断!对这个问题感到吃惊的人会大声说道。其他人可能会寻思二者有何差异。关断模式常常会保留存储器内容,启动时间更短,漏电流超低,而如果切断电源,这一切都不复存在。但是,假如不需要这些特性呢?设计人员会让电源保持稳定并使用关断模式而浪费电源吗?为何不能简单地通过切断电源来降低漏电流?关断模式是否存在一些基本的深层次的要求?感到迷惑不解?请看下文。

诱惑与风险

现代系统包含丰富的特性,这是通过多层次的复杂设计实现的,常常涉及到不止一个芯片。功耗是很多应用都关心的,诸如便携式医疗设备,因此这些芯片常常包含一种或多种关断模式。这些模式提供存储器内容保留、外设使用和快速开启等特性,而消耗的电源电流非常少。另一种方法是完全关断电源。这会完全切断芯片的电源,不允许任何电流进入电源引脚。虽然能够降低功耗,但这种方法存在一些严重的副作用。

考虑一个包括多个芯片的复杂系统,这些芯片通过多路复用总线相连。如果该系统设计用于功耗受限的应用,简单地切断未在使用的芯片电源似乎有利可图,尤其是在不需要关断模式提供的其他特性的时候。切断电源可降低漏电流,但没有电源时,引脚对输入信号可能起到低阻抗节点的作用,导致不可预测的操作和潜在的系统级威胁。虽然断电选项可能很诱人,但关断模式对复杂系统有着根本上的好处:它使各芯片处于已知的、希望的状态,即使芯片在低功耗与高性能模式之间循环,也能维持安全可靠的操作。详细情况可通过考察一个I/O节点来了解。

简单示例

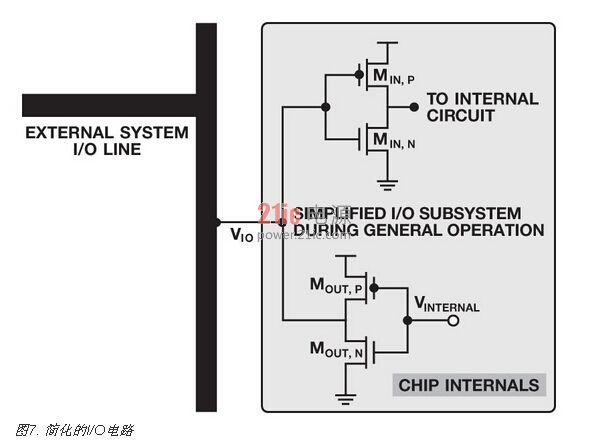

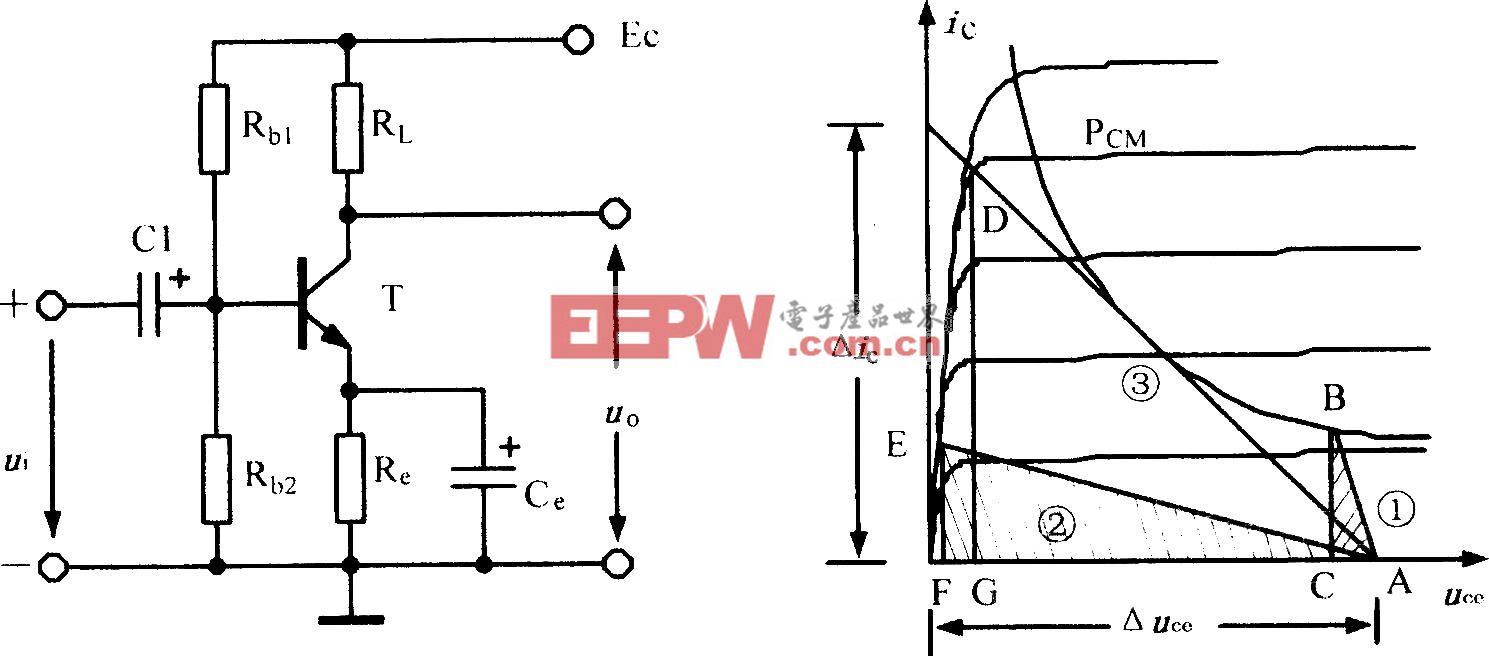

图7中的引脚连接到一个复用节点,其操作由一个经验证的系统架构设定。作为I/O引脚,它同时拥有输入和输出功能。

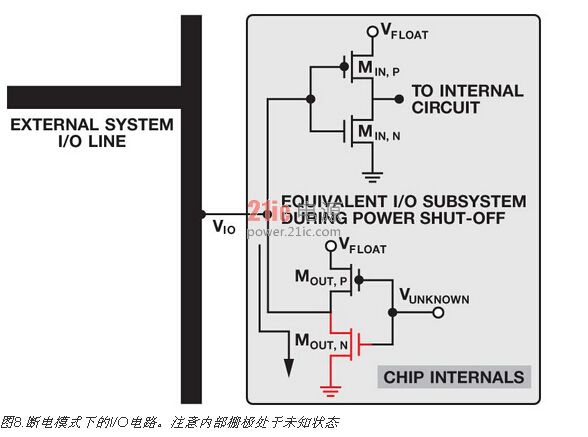

不考虑功率开关所用器件的问题,断开此芯片的电源(假设不需要任何芯片操作)将导致图8所示的情况,芯片内核到处都是未知状态。在最坏情况下,浮置栅极输出器件(MOUT, p 和MOUT, n)可能会在休眠时暴露于意想不到的外部电压下。对于本例所示的CMOS I/O,这可能产生一个经由NMOS漏极连接的对地低阻抗连接(红色亮显)。高电流将导致前一级的驱动能力透支,从而损害芯片中的MOS电路,甚至芯片本身。即使未损害系统,其性能也会降低。

关断模式

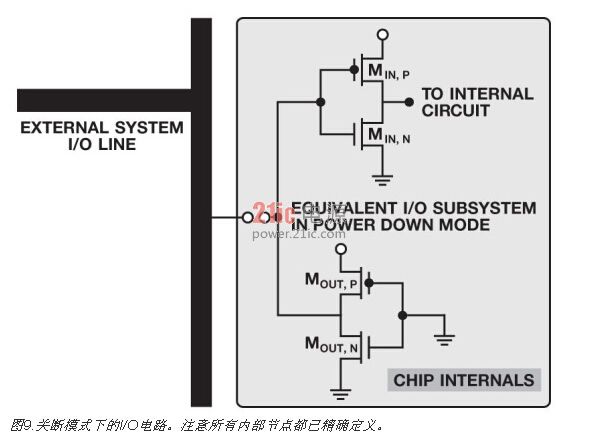

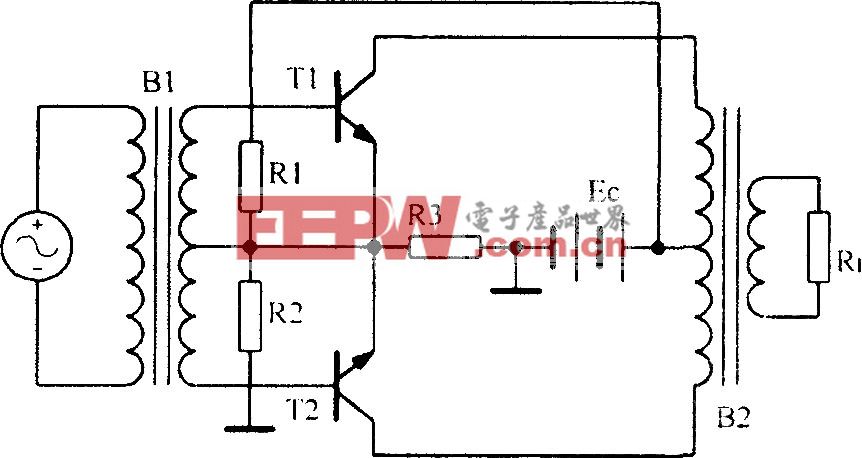

关断模式为芯片提供额外的一重保护,可防范上述意外工作状况。实现方式会因不同的模式、产品系列和供应商而异,但重点是在芯片内核休眠时提供安全的I/O边界,维持已知的、可信赖的低功耗状态。好处是系统器件之间的I/O操作(例如通过系统级多路复用总线)不会威胁到休眠中的器件。一个实现方案是在低功耗模式下将I/O引脚置于高阻态,使连接到边界引脚的内部节点处于已精确定义的状态。图9 显示了一个简化的实现方案。信号对内部电路无影响,从根本上保证其安全。其他实现方案(例如浅休眠模式)也可以让I/O外设保持上电,同时确保在关断模式期间芯片外设与内核之间的操作得到验证。这使得芯片在保持低功耗的同时,能够处理激活状态下的使用情形。此外,该系统降低了功率开关的成本;如若不然,将需要使用一个很大的低电阻器件,其漏电流和导通状态功耗均会相当大。

关断模式因芯片和供应商而异,因此,浅休眠模式之类名称的含义并不总是相同。有些支持保留存储器内容,有些则提供更多的中断数或其他类似特性。与完全断电相比,这些模式的一个突出优势是可以缩短系统响应时间。有些电路提供单独的I/O电源和内核电源。这种分离的一个优点是,电路板设计人员可以切断内核电源以降低漏电流,而I/O 则保持上电。强烈建议一定要从产品数据手册获得准确的详细信息,确保所需的特性和保护方法受到产品的支持。

尺寸不断缩小的影响

作为器件尺寸缩小的自然后果,现代IC工艺技术提供更高密度的封装,使得关断模式的优化使用越来越重要。不过,这也降低了器件的压力处理能力。例如,28nm 器件的栅极氧化物就比相应的180nm 器件要薄。这样,断电模式下栅极电压所施加的压力更有可能损坏较小的器件。此外,布局相关的参数也可能导致尺寸较小的器件发生灾难性故障。

所有这些影响使得关断模式对现代器件越来越有吸引力。现代芯片充盈着各种特性,包括成百上千万的元件;如果保持开启,每个器件都可能产生漏电流。优化特性使用并关断芯片中不使用的部分,可以消除其中的大部分漏电流。然而用户应该确保供应商明确支持这些模式,而不要试图自行开发关断功能。

更多情形

关于关断的完整拼图还缺几片。如果同时切断接地连接(这将形成另一条低阻抗路径)会怎样?这与直接驱动I/O引脚而不使能电源的ESD 情况相似,如果信号足够强,可能会触发ESD 保护结构,导致高电流流经其他相连的I/O引脚,产生假上电情况。更有可能的情况是信号稍弱一点,但仍然强到足以通过一条路径(如I/O箝位)抵达电源。信号可能无法触发电源箝位,但会在电源上引起意想不到的虚电压,从而造成未知工作状态,具体情形取决于芯片的拓扑结构。任一情况下,如果电路状态持续如此,则芯片可能受损,除非前一级已经停止供应高电流。如果信号强度不足以触发I/O箝位,它仍可能会对所遇到的第一个晶体管施压,长时间操作后可能会损坏该晶体管。

如果断开电源并拉低电源输入呢?这种情况下,芯片无浮动电源,不可能触发任何ESD 结构,但PMOS漏极电压可能高于主体电压,使漏极-主体二极管正偏。这样,来自前一级的电流将经过PMOS 器件流至地,直至器件烧毁、前一级停止提供电流或设计人员注意到报警。

结论

关断模式使得系统级响应更快速、更安全,因而是不可缺少的特性,尤其是在考察复杂系统中的完整信号链时。如果器件之间的交互很有限,或者系统整体很简单,足以确保不会出现复杂情况,则可以考虑完全切断电源。

评论