适用于低通跨阻滤波器的低噪声低失调斩波全差分运放

作者 张阳 电子科技大学 微电子与固体电子学院(四川 成都 610054)

本文引用地址:https://www.eepw.com.cn/article/201807/389579.htm张阳(1992-),硕士生,工程师,研究方向:集成电路。

摘要:零中频接收机的核心模块低通跨阻滤波器需要低噪声低失调的全差分运放,针对传统全差分运放具有高噪声高失调的缺点,设计了一种嵌套式斩波全差分运放。基于hlmc40lp工艺,通过Spectre仿真工具进行仿真与验证。斩波频率fchopper,low=1 kHz、fchopper,high=1 MHz时的仿真结果表明,设计的运放具有较低的输入等效噪声(输入等效噪声功率谱密度在100 Hz处仅为7.668 nV/sqrt(Hz)),较低的输入失调电压(1.007 V),运放的开环增益为84.6 dB,运放的增益带宽积为140 MHz。

0 引言

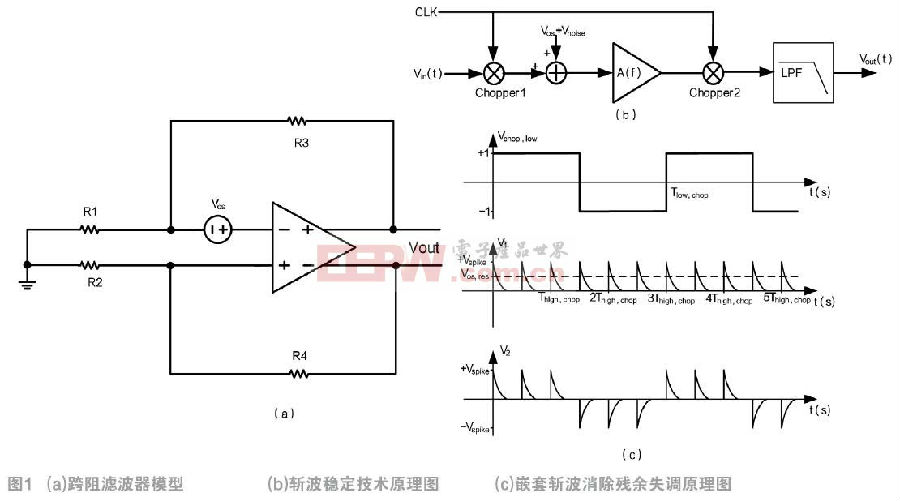

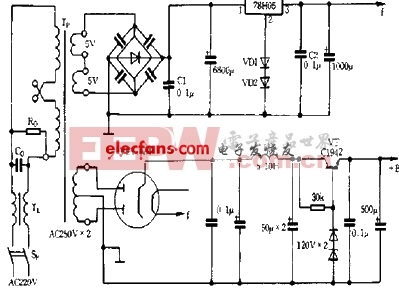

低通跨阻滤波器是零中频接收机中一个核心模块,主要作用是将前级电路的直流小信号电流信号放大以及转换为电压信号,从而供后级电路处理。基于噪声的考虑,接收机一般采用无源混频器,原因在于无源混频器不存在直流电流,它本身的噪声对整个系统的贡献可以忽略不计[1-2]。但是,这也使得低通跨阻滤波器必须具有更好的低频噪声性能[3],运放在低频段的噪声主要是1/f噪声。如图1(a)所示,其中R1=R2,R3=R4。R1与R2为跨阻滤波器输入端等效电阻,跨阻滤波器增益与电阻R3、R4的阻值相等。因为我们需要检测微弱信号,R3、R4阻值相对较大。跨阻滤波器输出端固定失调电压等于运放输入失调电压值乘以R3/R1,假如运放的输入失调电压过大,则跨阻滤波器输出端固定失调电压相对较大,而跨阻滤波器的输出动态范围(输出摆幅)是固定的,固定失调电压会大幅减小跨阻滤波器的输出摆幅,从而减少跨阻滤波器能够无失真放大电流的范围,所以减小全差分运放的输入失调电压是势在必行。同时,为了减小跨阻滤波器的增益损失以及增大混频器的线性度[4],运放的增益需要大于80 dB,带宽需要大于100 MHz。

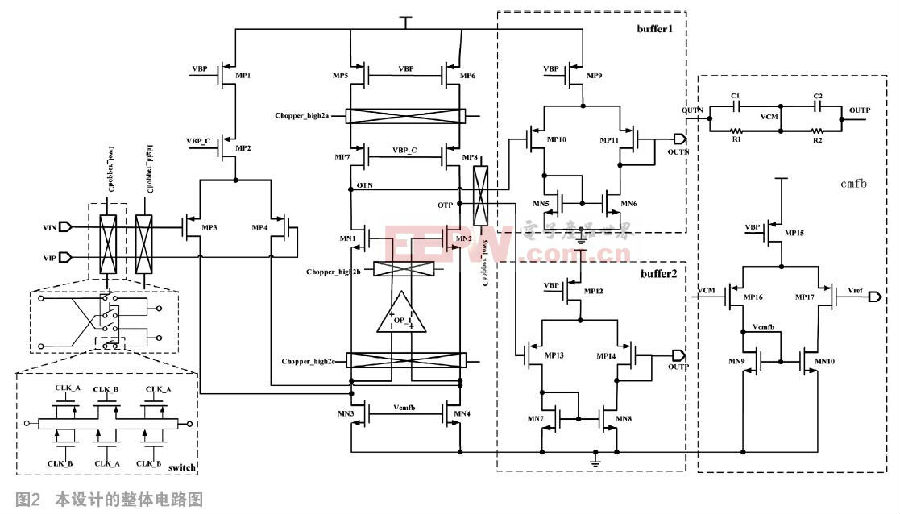

针对运放需具备低噪声、低失调以及高增益的特性,本文提出了一种满足要求的同时结合嵌套斩波技术以及增益自举技术的全新的全差分折叠共源共栅式运放结构。由于嵌套斩波技术可以大幅消除运放输入失调以及低频噪声,同时能够减小因斩波开关动作引起的残余失调量,而增益自举技术可以大幅增加运放增益,避免使用两级运放结构,从而减小需要的共模反馈电路数量,而增益自举技术使用的运放可以作低功耗设计,相应地减少了运放功耗。由于跨阻滤波器后面接有大电容负载,本文利用接成单位增益负反馈的运放作为缓冲级来驱动后级负载,这也同时避免了后级小电阻负载减小主运放的增益。同时,利用本文设计运放结构的特殊性,直接利用并联的电阻与电容在单位增益负反馈的运放输出端取共模电平,然后使用简单的共模反馈电路稳定整体电路的静态工作点,如图2所示,这样设计的优势在于,电阻阻值可以设计得较小且不会减小主运放的增益。文献[5]为了保证高增益而采用了两级运放结构,同时为了使共模反馈电路不影响整体运放增益,使用两个差分对检测共模电压的结构,以达到与本文设计的共模反馈电路相同的带宽,文献[5]的共模电路消耗的电流需要是我设计的电路的两倍,而且两级运放结构需要两级共模反馈电路,因此本文设计的运放相对于文献[5]的设计复杂性大大降低,同时降低了消耗的电流。

1 斩波稳定原理以及非理想因素分析

斩波稳定(CHS:Chopper Stabilization)技术是E.A.Goldberg在1948年提出的[5]。CHS技术主要将低频的噪声以及失调调制到高频,之后通过一个低通滤波器将它们完全滤掉。在理想情况下,斩波技术能够完全消除掉直流失调以及低频段1/f噪声。

1.1 基本原理

如图1(b)是一个斩波放大器的基本架构[6]。首先,输入信号由斩波器chopper1调制到高频。之后,被调制到高频的输入信号、直流失调以及输入1/f噪声同时被放大器放大。然后,经过放大的输入信号被斩波器chopper2还原,而直流失调以及1/f噪声被调制高频。最终,一个低通滤波器将调制到高频的噪声以及失调滤除,得到的输出信号就是经过放大的输入信号,这样就消除了直流失调以及噪声对信号的影响。

1.2 嵌套斩波技术

斩波器的开关一般由CMOS管构成。由于控制斩波器开关管栅端的信号为具有斩波频率的时钟信号,时钟信号的跳变会通过栅漏或栅源交叠电容耦合到信号通路,从而引入残余失调。同时,由于该CMOS开关管不是理想的开关管,开关管的通断会产生沟道电荷注入效应,在信号通路引入失调。上述两个因素共同作用效果如图1(c),每次开关动作会在开关切换边缘引入一个幅度很大的毛刺电压。经过输出快速斩波器的调制,这个毛刺电压变为平均值为Vos,res的高频纹波V1,V1信号频率是斩波频率的两倍,如图1(c)所示。V1信号能量平均值为Vos,res,经过末端低通滤波器之后形成输出残余失调。控制斩波开关的时钟信号频率越高,开关管面积越大,输出残余失调就越大。

嵌套斩波技术工作原理如图1(c)所示,利用两组快慢斩波开关,快速斩波时钟频率是慢速斩波时钟频率的整数倍,这样输出慢速斩波器正好可以将快速斩波开关引入的高频纹波V1转化为电压V2,V2能量平均值为0,信号周期等于Tlow,chop。在理想情况下,V2信号会被滤波器滤除而不会产生残余失调。使用嵌套斩波需要注意的是:输入信号的频率不能超过低频斩波信号的频率。

选择合适的斩波频率直接关系着整个斩波放大器的性能。为了减小运放的增益损失,斩波频率需要小于运放的3 dB带宽;同时为了有效地减小1/f噪声,斩波频率需要大于噪声转角频率[5],该斩波频率是嵌套斩波技术中的高频斩波信号的频率。为了有效减小快速斩波引入的残余失调,低频斩波信号的频率一般设置为高频斩波信号频率的1/1000。

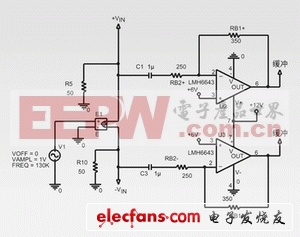

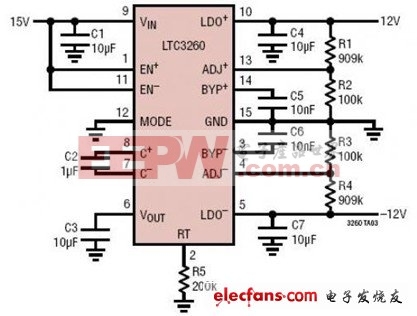

2 整体电路设计

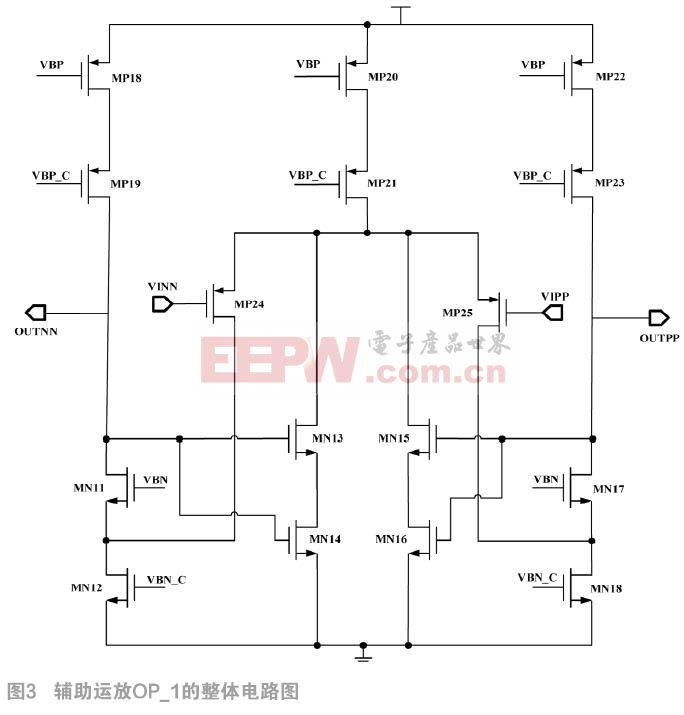

本文设计的斩波全差分运放是具有增益自举结构的全差分折叠共源共栅式运放,整体电路图如图2所示。由于低通跨阻滤波器需要运放增益大于80 dB,普通的折叠共源共栅式运放无法达到要求,因此本论文采用增益自举结构来提高运放增益,辅助运放OP_1的结构如图3所示。根据文献[7]所述,我设定辅助运放的单位增益带宽在无增益自举技术的主运放的3 dB带宽以及单位增益带宽之间,这样辅助运放引入的零极点对不会影响运放的整体稳定性。因为要使在跨阻滤波器输出端的低阻抗负载不影响整体运放的增益,我们需要在折叠共源共栅式运放以及跨阻滤波器输出端的低阻抗负载之间加上一级缓冲器,如图2所示,buffer1以及buffer2可以确保低阻抗负载不会影响主运放的增益。同时,缓冲器的引入可以简化共模反馈电路设计,我们可以直接使用电容C1与C2以及电阻R1与R2在buffer1与buffer2输出端提取输出电压共模电平,通过cmfb运放得到共模反馈电压Vcmfb,返回到主运放,稳定主运放的输出端OTN以及OTP的输出共模电压。

在图2中,Chopper_low1、Chopper_high1、Chopper_high2a、Chopper_high2b、Chopper_high2c和Chopper_low2是斩波开关模块,其中Chopper_low1与Chopper_low2是慢速斩波模块,Chopper_high2a、Chopper_high2b与Chopper_high2a、Chopper_high2c是快速斩波模块。Chopper_low2被放置在折叠共源共栅运放的输出极点(同时是运放的主极点),Chopper_high2a与Chopper_high2c放置在低阻节点,实现快速斩波。由于辅助运放OP_1的噪声对总体运放噪声有一定贡献,所以利用Chopper_high2a与Chopper_high2c在辅助运放的环路中可以减小辅助运放对噪声的贡献。PMOS管MP3、MP4、MP5与MP6以及NMOS管MN3与MN4是主要贡献噪声的管子,必须取大尺寸的管子。同时,MP3与MP4的过驱电压可以减小,增大其跨导,而MP5、MP6、MN3与MN4作为负载管,可以适当增大其过驱电压,减小其跨导。辅助运放OP_1电路图如图3所示,想减小辅助运放的输入等效噪声,MP18、MP22、MP24、MP25、MN12与MN18取大尺寸管子。MN13、MN14、MN15与MN16构成共模反馈电路,稳定辅助运放的输出共模电平。

设计斩波调制器,主要考虑减小开关的沟道电荷注入以及时钟馈通效应,同时我们还要主要减小开关导通电阻,减小开关消耗的电压余度。采用带虚拟管的开关有助于减小部分电荷注入以及时钟馈通的影响,虚拟管在开关管两侧,源漏短接,尺寸是开关管的1/2,具体电路如图2所示[9]。小的开关尺寸能减小时钟馈通,Chopper_low1与Chopper_low2采用1.6μm/0.27μm。而为了减小导通电阻,Chopper_high1、Chopper_high2a、Chopper_high2b与Chopper_high2c采用3.2 /0.27 的较大尺寸。版图设计时,要特别注意增加开关管的匹配性,从整体减小电荷注入以及时钟馈通影响。

3 仿真结果分析

因为包含斩波操作的运放实际上是周期性工作,所以我使用Cadence公司的spectre仿真工具中的PSS、PAC、Pnoise对其周期性幅频特性以及噪声特性进行仿真。本文设计使用hlmc40lp工艺,电源电压为2.5 V,斩波频率fchopper,low=1 kHz、fchopper,high=1 MHz。

采用PAC仿真结果表明,其开环增益为84.6 dB,增益带宽积为140 MHz,带宽为9.218 kHz。其消耗的总功耗为2.8 mA,buffer1与buffer2每支都消耗1.038 mA的功耗,所以该跨阻滤波器的带负载能力较强。

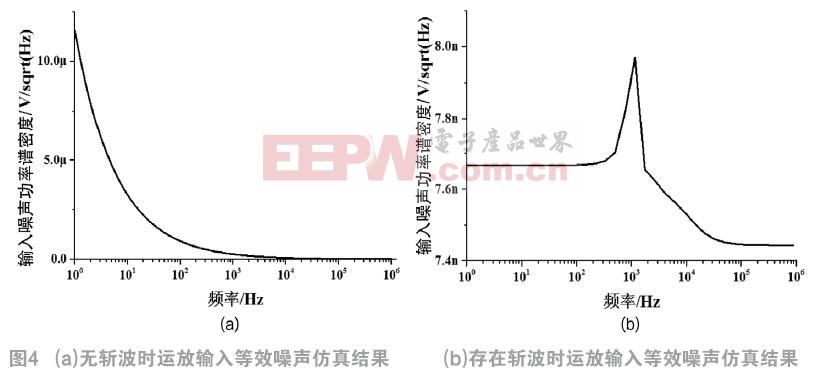

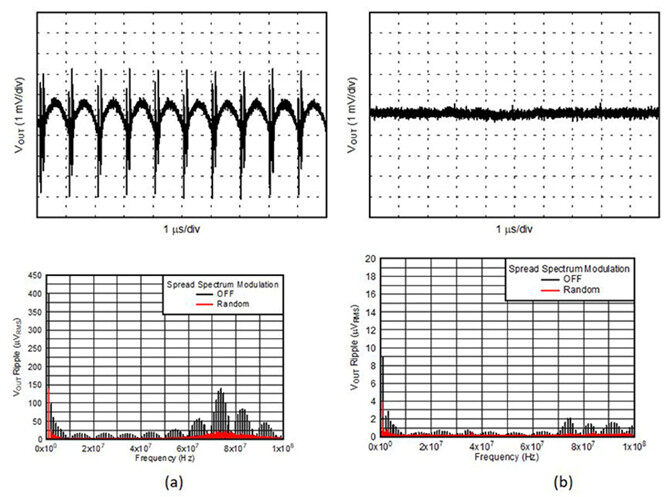

采用Pnoise仿真得到仿真结果如图4所示 ,放大器输入等效噪声功率谱密度在100 Hz处仅为7.668 nV/sqrt(Hz),而无斩波时放大器输入等效噪声功率谱密度在100 Hz处为1.254 μV/sqrt(Hz),噪声性能有明显改善。图4(b)中1 kHz出现了一个尖峰,说明噪声被调制到高频,这对工作在低频的运放是个理想的结果,被调制到高频的噪声不会影响运放的性能,这也证明斩波技术能极大的提高运放性能。

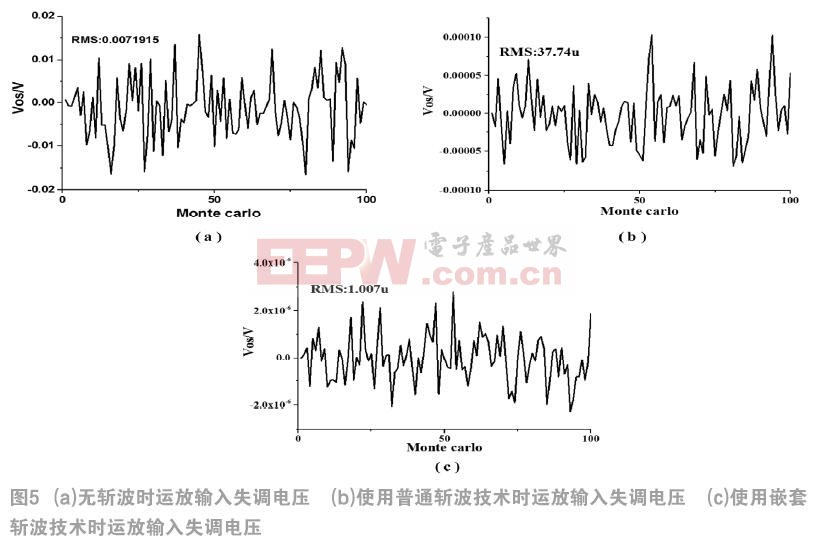

为了仿真斩波运放输入失调电压,我使用斩波运放搭建单位增益负反馈电路,然后给每个管子加上偏差进行蒙特卡罗瞬态仿真,取斩波运放正负输出端电压之差在固定一段时间内的均值作为运放单个失调电压。最后对蒙特卡罗仿真得到的多个失调电压值直接取均方根值(RMS值)作为斩波运放的输入失调电压,仿真结果如图5所示。图5仿真结果表明斩波技术能够有效地减小运放的失调电压,而嵌套斩波技术相对于普通斩波技术能有效减小因开关引起的残余失调量。

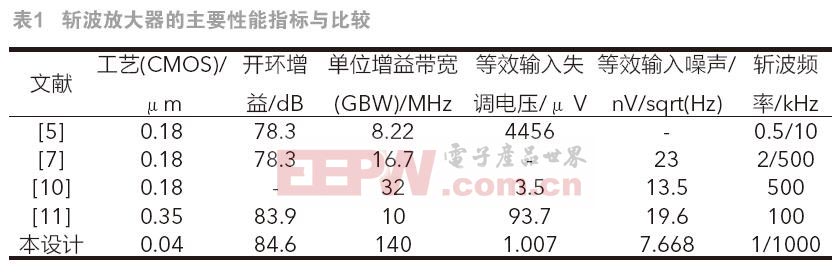

表1给出了本设计与其他论文的性能的比较。与其他论文相比,本文设计的斩波运放等效输入失调电压以及等效输入噪声相对较低,本设计在综合整体性能具有相当的优势。

4 结论

本文设计了一种应用于跨阻滤波器的低噪声低失调斩波运放电路。仿真结果表明,本文设计的运放具有较低的输入等效噪声(输入等效噪声功率谱密度在100 Hz处仅为7.668 nV/sqrt(Hz)),极低的输入失调电压(1.007 μV),开环增益为84.6 dB,增益带宽积为140 MHz。本文设计的斩波运放电路完全能满足跨阻滤波器对运放的要求。

参考文献:

[1]J. Crols and M. Steyaert, “A 1.5GH.z Highly Linear CMOS Downconversion Mixer,” IEEE J. of Solid State Circuits, vol. 30, no. I, pp.736-742, 1995

[2]J. van Sinderen, F. Seneschal, E. Stikvoort, F. Mounaim, M. Notten, H. Brekelmans, O. Crand, F. Singh, M. Bernard, V. Fillatre, and A. Tombeur, “A 48-860MHz digital cable tuner IC with integrated RF and IF selectivity,” in Intl. Solid-State Circuits Conf, San Francisco, pp. 444- 506 vol.1,2003.

[3]W. Redman-White and D. Leenaerts, “1/f Noise in Passive CMOS Mixers for Low and Zero IF Integrated Receivers,” in IEEE European Solid-State Circuits Conf., 2001.

[4]Hodgson J K. Design of a 10 MHz Transimpedance Low-Pass Filter with Sharp Roll-Off for a Direct Conversion Wireless Receiver[J]. Texas A & M University, 2009.

[5]张锗源,杨发顺,杨法明,张荣芬,邓朝勇.嵌套式斩波运放的分析与设计[J].微电子学,2012,42(01):25-29,33.

[6]杨银堂,贺斌,朱樟明. CMOS斩波稳定放大器的分析与研究[J].电子器件,2005,(01):167-171.

[7]李威,张兆浩,吴次南.低噪声低功耗斩波运放的分析与设计[J].电子科技,2016,29(05):26-29.

[8]K. Bult and G. Geelen. "The CMOS gain-boosting technique," Analog Integrated Circuits and Signal Processing, vol.1, (no.2), Oct. 1991. pp. 119-35.

[9]孙鹏.用于植入式生物医疗系统的高性能仪表放大器的研究与设计[D].杭州:浙江大学,2013.

[10]I. Akita and M. Ishida “A 0.06mm2 14nV/√Hz chopper instrumentation amplifier with automatic differential-pair matching,” ISSCC Dig. Tech. Papers, pp. 178-179, Feb. 2013.

[11]尹韬,杨海钢,刘珂.一种适用于微传感器读出电路的低噪声、低失调斩波放大器[J].半导体学报,2007(05):796-801.

本文来源于《电子产品世界》2018年第8期第53页,欢迎您写论文时引用,并注明出处。

评论