印制电路板上的干扰及抑制

印制电路板设计是电子产品制作的重要环节,其合理与否不仅关系到电路在装配、焊 接、调试和检修过程中是否方便,而且直接影响到产品的质量与电气性能,甚至影响到电路功能能否实现。因此,掌握印制电路板的设计方法十分重要。

本文引用地址:https://www.eepw.com.cn/article/201807/383843.htm一般说来,印制电路板的设计不需要严谨的理论和精确的计算,布局排板并没有统一的固定模式。对于同一张电路原理图,因为思路不同、习惯不一、技巧各异,就会出现各种设计方案,结果具有很大的灵活性和离散性。

印制电路板的设计是电子知识的综合运用,需要有一定的技巧和丰富的经验。这主要取决于设计者对电路原理的熟悉程度,以及元器件布局、布线的工作经验。对于初学者来说,首先就是要熟练掌握电路的原理和一些基本布局、布线原则。然后通过大量的实践,在实践中摸索、领悟并掌握布局、布线原则,积累经验,才能不断地提高印制电路板的设计水平。

印制电路板上的干扰及抑制

干扰现象在整机调试中经常出现,其原因是多方面的。不仅有外界因素造成的干扰(如电磁波),而且印制电路板绝缘基板的选择、布线不合理、元器件布局不当等都可能造成干扰,这些干扰在电路设计和排版设计中如予以重视,则可完全避免。相反,如果不在设计中考虑,便会出现干扰,使设计失败。

(一)电源干扰与抑制

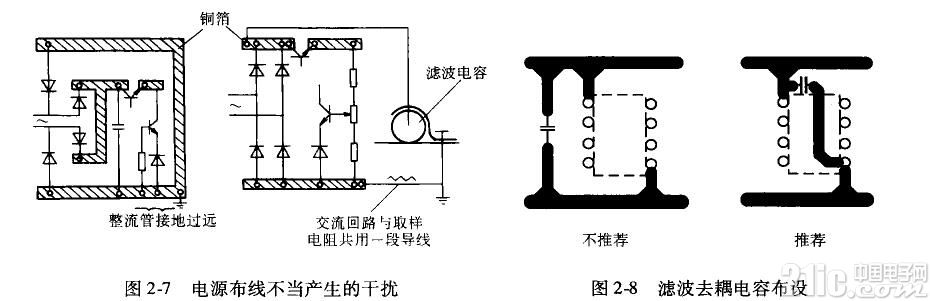

任何电子产品都需要电源供电,并且绝大多数是由交流市电通过降压、整流、稳压后供给。供电电源的质量直接影响整机的技术指标,而电源的质量除原理设计本身外;工艺布线和印制电路板设计不合理,去耦电容放置的位置不正确,都会产生干扰,特别是交流电源的干扰。例如在图2-7所示的稳压电路中,整流管接地过远,交流回路的滤波电容与直流电源 的取样电阻共用一段导线接地,都会由于布线不合理导致直流回路彼此相连,造成交流信号对直流信号产生干扰,使电源质量下降。

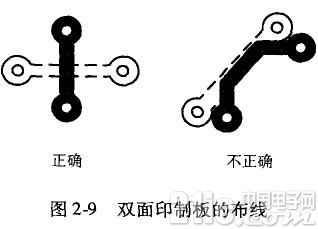

在印制电路板上,若直流电源的去耦电容所放位置不正确,也起不到去耦的作用。一般用铝电解电容器(lOF左右)滤除低频干扰并将其放置在电路板电源入口处(不推荐);陶瓷电容器(0.1uF-680pF)用于滤除高频干扰,必须将其靠近集成电路的电源端且与其地线连接 (推荐),如图2-8所示。陶瓷电容的容量根据1C的速度和电路的工作频率选择,速度越快,频率越高,电容量越小。

(二)磁场的干扰及抑制

印制电路板的特点是使元器件安装紧凑、连接密集,这一特点无疑是印制电路板的优点。如果设计不当,这一特点就会给整机带来麻烦。例如印制电路板分布参数造成的干扰、元器件相互之间的磁场干扰等,在排版设计中必须引起重视。

1.印制导线间的寄生耦合

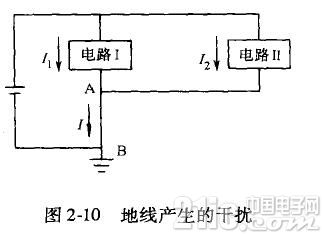

两条相距很近的平行导线,它们之间的分布参数可等效为相互耦合的电感和电容。当信号从一条线中通过时,另一条线内也会产生感应信号,感应信号的大小与电流的流向、原始的频率及功率有关,此感应信号就是由分布参数产生的干扰源。为了抑制这种干扰,排版前应分析原理图,区别强弱信号线,使弱信号线尽童短,并避免与其他信号 线平行;若不能避免平行线,可以拉开两平行线的距离 或在两平行导线间布上一根地线。对于双面板,两面的印制导线走向要相互垂直,尽量避免平行布线,如图 2-9所示。这些措施可以减少分布参数造成的干扰。

2.磁性元件的干扰

磁性元件对电路也会造成干扰。例如,扬声器、电磁铁产生的恒定磁场,高频变压器、继电器等产生的变化磁场,不仅对周围元件产生干扰,同时对印制导线也会产生影响。抑制这些干扰的措施有:

1)两个磁元件的相互位置应使两个磁场方向相互垂直,这样做使它们之间的耦合最弱。

2)采用导磁材料对干扰源进行磁屏蔽,它有两种形式:一是用屏蔽罩进行屏蔽,并且 屏蔽罩要良好接地;二是用铁氧体磁珠套在元器件的引脚上实现屏蔽。

(三)热干扰及抑制

温度升高造成的干扰在印制电路板设计中也应引起注意。例如,晶体管是一种温度敏感 器件,特别是锗材料的半导体器件,更易受环境温度的影响而使工作点漂移,造成整个电路 性能发生变化,因而在排版时应予以考虑。

1)对发热元器件,应优先安排在有利于散热的位置,尽量不要把几个发热元器件放在一起。必要时可单独设置散热片或加散热用的风扇以降低温度对临近元器件的影响。

2)对于温度敏感的元器件,如晶体管、集成电路、大容量的电解电容器和其他热敏元件等,不宜放在热源附近或设备的上部。

(四)地线的公共阻抗干扰及抑制

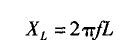

电子线路工作时,需要直流电源供电,直流电源的某一极往往作为测量各点电压的参考点,与此一极连接的导线即为电路的地线。它表示零电位的概念。但在实际的印制电路板上,由于地线具有一定的电阻和电感,在电路工作时,地线具有一定的阻抗,当地线中有电流流过时,因阻抗的存在,必然在地线上产生压降,这个压降使地线上各点电位都不相等,这就对各级电路带来影 响,如图2-10所示。由于电源提供的电流,既有直流分量也有交流分量,因而在地线中,由于地线阻抗产生的电压 降,除直流电压降外,还有各种频率成分的交流电压降,这 些交流电压降加在电路中,就形成了电路单元间的互相干扰。

实验证明:流过印制导线的电流频率越高,感抗成分占 整个阻抗的比例越大,干扰也就越大。例如,一块铜箔厚度为35um的印制电路板,印制导线宽度为lmm,则每10mm的电阻值为左右,其电感量为4nH左右,用公式

计算一下感抗,在10MHz时Xl=0.25Ω,在1000MHz时则是25Ω。当印制导线上瞬间有峰值1A的脉冲状噪声电流通过时,产生的噪声压降很大,影响电路正常工作,造成这类干扰的主要原因在于两个以上回路共用一段地线。为克服地线公共阻抗的干扰,在地线布设时应遵循以下几个原则:

1)地线一般布设在印制电路板边缘,以便于印制电路板安装在机壳底座或机架上。

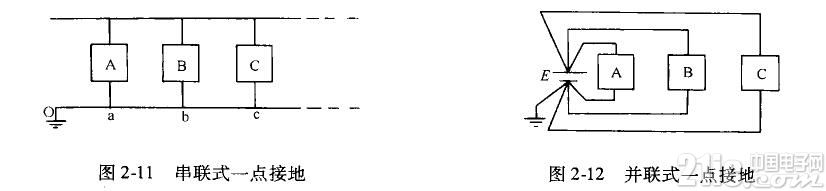

2)对低频信号地线,采用一点接地的原则。如果形成多点接地,会出现闭合的接地环路,当低频或脉冲磁场穿过该环路时将产生磁感应噪声,于是不同接地点之间会出现地电位差,形成干扰。通常一点接地有以下两种形式。

①串联式一点接地,如图2-11所示。各单元电路一点接地于公共地线,但各电路离电源远近不同,离电源最远的C回路因地线阻抗大所受的干扰大,而离电源最近的A回路因地线阻抗小所受的干扰最小。由于各电路抗干扰的能力不同,所以在这种地线系统中,除了要设计低阻抗地线外,还应将易受干扰的敏感电路单元尽可能靠近电源。串联式一点接地能有效地避免公共阻抗和接地闭合回路造成的干扰,而且简单经济,在电路中被广泛采用。

②并联式一点接地,如图2-12所示。以面积足够大的铜箔作为接地母线,并直接接到电位基准点,滞要接地的各部分就近接到该母线上。由于接地母线阻抗很小,故能够把公共阻抗干扰减弱到允许程度。

3)在小信号模拟电路和大信号功放电路并存的电路中,采用大、小信号地线分开的办法。大信号地线在布局时,接地点应安排在靠近电源的地方;小信号地线在布局时,接地点应安排在远离电源的地方。

4){频电路宜采用多点接地。在高频电路中应尽童扩大印制电路板上地线的面积,这样可以有效减少地线的阻抗。对于双固板,可利用其中一个导电平面作为基准地,需要接地的各部分可就近接到该基准地上。由于导电平面的高频阻抗很低,所以各处的基准电位比较接近,可有效地减少地线的阻抗。

5)在一块印制电路板上,如果同时布设模拟电路和数字电路,两种电路的地线要完全 分开,如图2-13所示。供电也要完全分裕以抑制它们相互干扰。

评论