全新CMSIS-NN神经网络内核让微控制器效率提升5倍

目前,在许多需要在本地进行数据分析的“永远在线”的物联网边缘设备中,神经网络正在变得越来越普及,主要是因为可以有效地同时减少数据传输导致的延时和功耗。 而谈到针对物联网边缘设备上的神经网络,我们自然会想到Arm Cortex-M系列处理器内核,那么如果您想要强化它的性能并且减少内存消耗,CMSIS-NN就是您最好的选择。基于CMSIS-NN内核的神经网络推理运算,对于运行时间/吞吐量将会有4.6X的提升,而对于能效将有4.9X的提升。

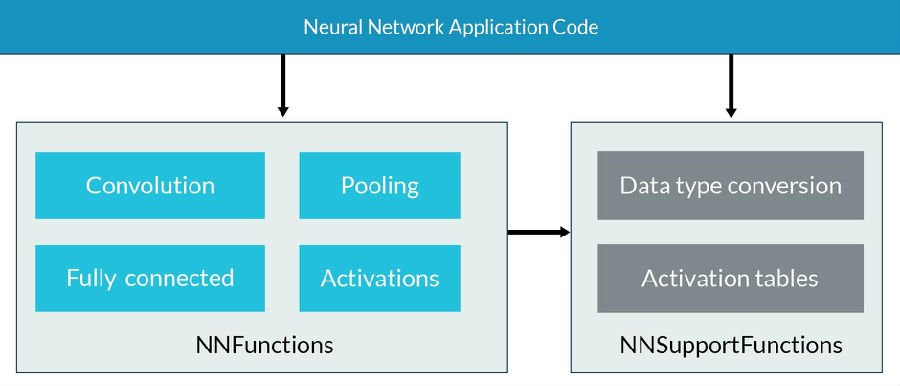

本文引用地址:https://www.eepw.com.cn/article/201801/375170.htmCMSIS-NN库包含两个部分: NNFunction和NNSupportFunctions。 NNFunction包含实现通常神经网络层类型的函数,比如卷积(convolution),深度可分离卷积(depthwise separable convolution),全连接(即内积inner-product), 池化(pooling)和激活(activation)这些函数被应用程序代码用来实现神经网络推理应用。 内核API也保持简单,因此可以轻松地重定向到任何机器学习框架。NNSupport函数包括不同的实用函数,如NNFunctions中使用的数据转换和激活功能表。 这些实用函数也可以被应用代码用来构造更复杂的NN模块,例如, 长期短时记忆(LSTM)或门控循环单元(GRU)。

对于某些内核(例如全连接和卷积),会使用到不同版本的内核函数。 我们提供了一个基本的版本,可以为任何图层参数“按原样”通用。 我们还部署了其他版本,包括进一步的优化技术,但会对输入进行转换或对层参数有一些限制。 理想情况下,可以使用简单的脚本来分析网络拓扑,并自动确定要使用的相应函数。

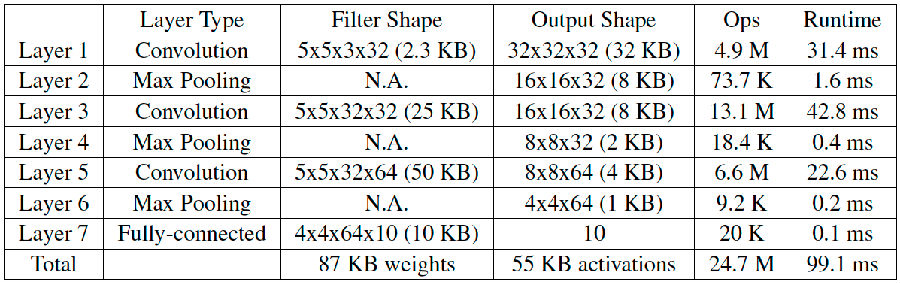

我们在卷积神经网络(CNN)上测试了CMSIS-NN内核,在CIFAR-10数据集上进行训练,包括60,000个32x32彩色图像,分为10个输出类。 网络拓扑结构基于Caffe中提供的内置示例,具有三个卷积层和一个完全连接层。 下表显示了使用CMSIS-NN内核的层参数和详细运行时结果。 测试在运行频率为216 MHz的ARM Cortex-M7内核STMichelectronics NUCLEO-F746ZG mbed开发板上进行。

整个图像分类每张图像大约需要99.1毫秒(相当于每秒10.1张图像)。 运行此网络的CPU的计算吞吐量约为每秒249 MOps。 预量化的网络在CIFAR-10测试集上达到了80.3%的精度。 在ARM Cortex-M7内核上运行的8位量化网络达到了79.9%的精度。 使用CMSIS-NN内核的最大内存占用空间为〜133 KB,其中使用局部im2col来实现卷积以节省内存,然后进行矩阵乘法。 没有使用局部im2col的内存占用将是〜332 KB,这样的话神经网络将无法在板上运行。

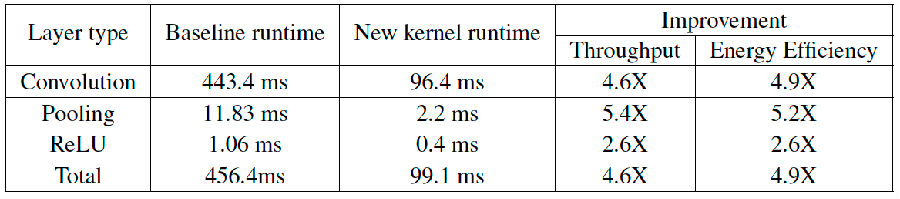

为了量化CMSIS-NN内核相对于现有解决方案的好处,我们还使用一维卷积函数(来自CMSIS-DSP的arm_conv),类似Caffe的pooling和ReLU来实现了一个基准版本。 对于CNN应用,下表总结了基准函数和CMSIS-NN内核的比较结果。 CMSIS-NN内核的运行时间/吞吐量比基准函数提高2.6至5.4倍。 能效提高也与吞吐量的提高相一致。

高效的NN内核是充分发挥ARM Cortex-M CPU能力的关键。 CMSIS-NN提供了优化的函数来加速关键的NN层,如卷积,池化和激活。 此外,非常关键的是CMSIS-NN还有助于减少对于内存有限的微控制器而言至关重要的内存占用。 更多细节在我们的白皮书中您可以读到,您可以使用下面的按钮从康奈尔大学图书馆网站下载。

CMSIS-NN内核可在github.com/ARM-software/CMSIS_5上找到。 应用 代码可以直接使用这些内核来实现Arm Cortex-M CPU上的神经网络算法。 或者,这些内核可以被机器学习框架用作原语函数(primitives)来部署训练过的模型。

如需进一步资源,更详细的产品信息和教程,帮助您解决来自边缘ML的挑战,请访问我们的新机器学习开发者网站。

参考:CMSIS-NN: Efficient Neural Network Kernels for Arm Cortex-M CPUs White Paper

评论