二阶有源带通滤波器原理图及设计流程

本文为您带来二阶有源带通滤波器设计具体流程,带通滤波器原理图电路图含义、带通滤波器方案选择、仿真,电路性能测试,直流稳压电源设计、运放及电压跟随器选择。

本文引用地址:https://www.eepw.com.cn/article/201710/368833.htm什么是带通滤波器?

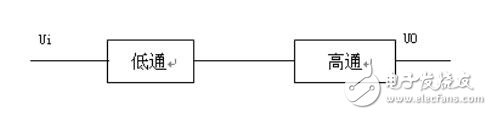

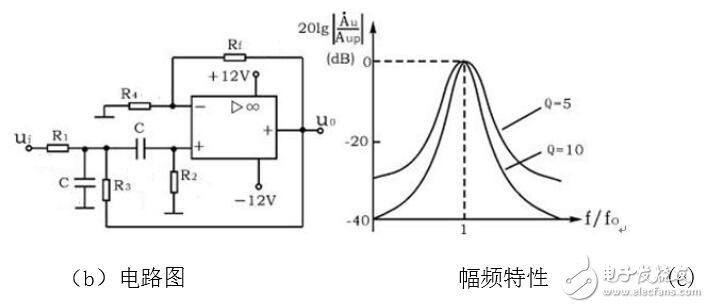

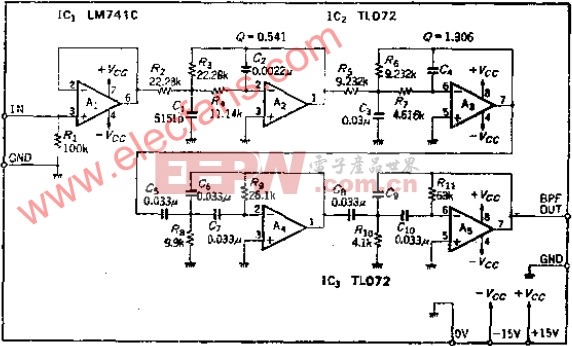

带通滤波器是指只允许在某一个通频带范围内的信号通过的滤波器,而比通频带下限频率低和比上限频率高的信号均加以衰减或抑制,注意:要将高通的下限截止频率设置为小于低通的上限截止频率。反之则为带阻滤波器。典型的带通滤波器可以从二阶低通滤波器中将其中一级改成高通而成。如图2-4所示。

(a) 带通滤波器原理框图

图2-4 二阶带通滤波器

带通滤波器电路性能、参数:

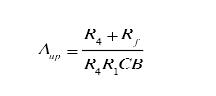

通带增益Aup:

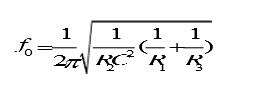

中心频率0f:

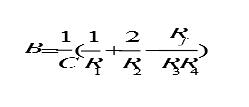

通带宽度B:

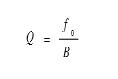

品质因素Q:

此电路的优点是改变R和R4的比例就可改变频宽而不影响中心频率。

有源带通滤波器的设计要求指标

1.带宽要求:15Hz~35KHz

2.带外抑制比要求:>=-20dB/倍频程

方案的选择及流程

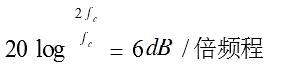

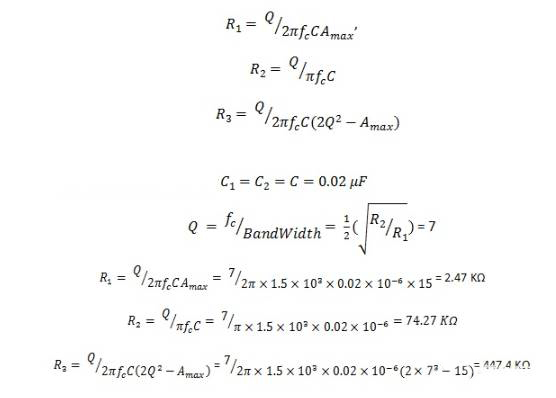

1.阶数的选择根据所需带外抑制比大于等于20dB/倍频程,我们选用了四阶带通滤波器,因为选用二阶时为:

选用三阶时为:

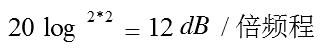

选用四阶时为:

此时可以满足要求带外抑制比≥20dB/倍频程

倍频程和10倍频程的选择:

对于滤波或运放放大倍数来讲是用dB来表示的。具体的公式是

A(w)=A0/(1+jw/w0),w0是滤波频率或运放的一个极点。

采用dB表示时是 20*log|A(w)|. A(w) 要取模,即A0/sqrt(1+w*w/(w0*w0)).

对于n倍频(靠近w0的频率不准确,n>0),w2=n*w1, w1>>w0.(开方中的1可忽略)则有:

A(w2)-A(w1) = 20*logA0-20*log(sqrt(w2*w2)/(w0*w0)) -20*logA0+20*log(sqrt(w1*w1)/(w0*w0))

= -10*log(w2*w2/(w1*w1) = -10*log(n*n)

这样对于两倍频,w2=2*w1,则此时下降是 -10*log4=-6.02dB 当w2=10*w1时 -10*log100=-20dB.

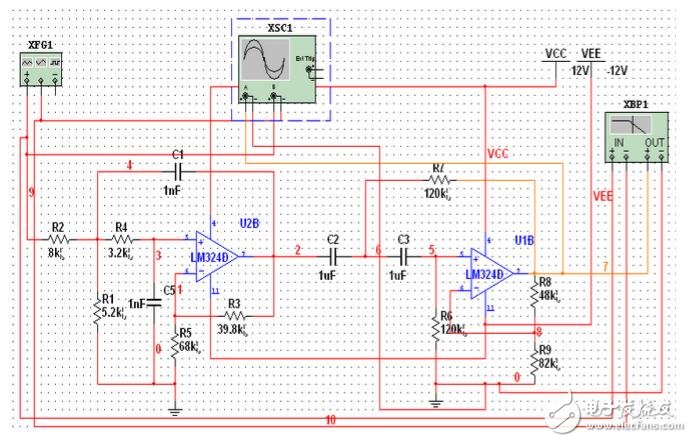

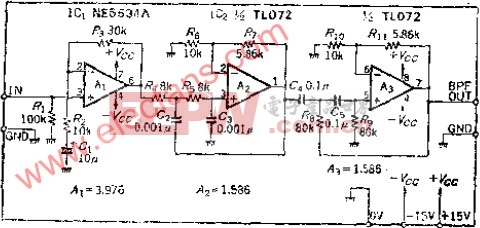

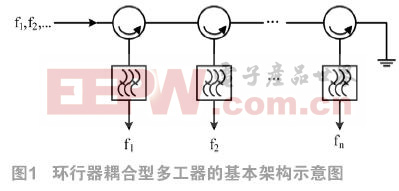

2.电路形式的选择由于我们所选的滤波器阶数n为偶数,所以我们选用n/2个二阶滤波器级联;

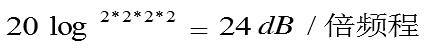

3.原理图仿真依原理图用MulTIsim 10.0进行仿真,使基本达标。我们用Protel99SE画出来的设计原理图:

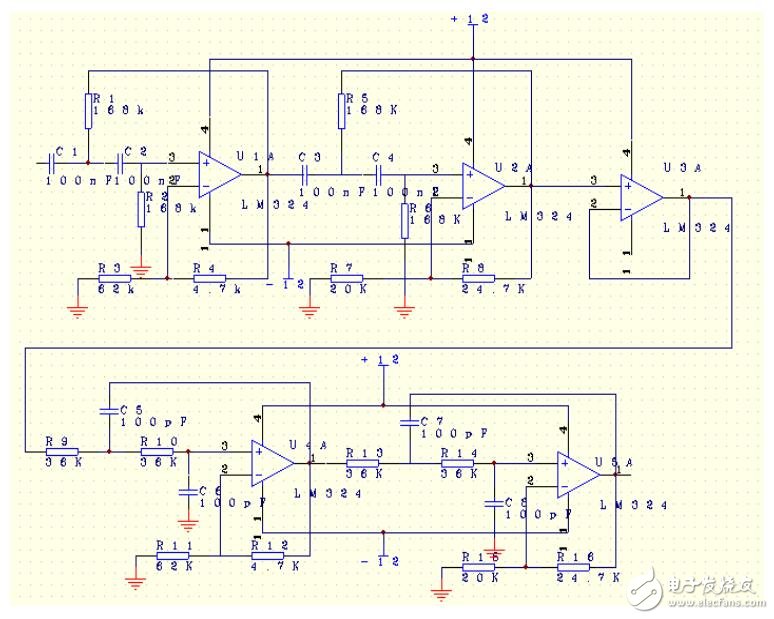

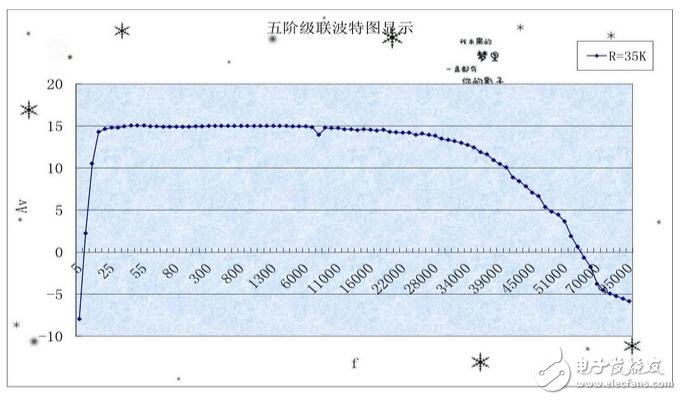

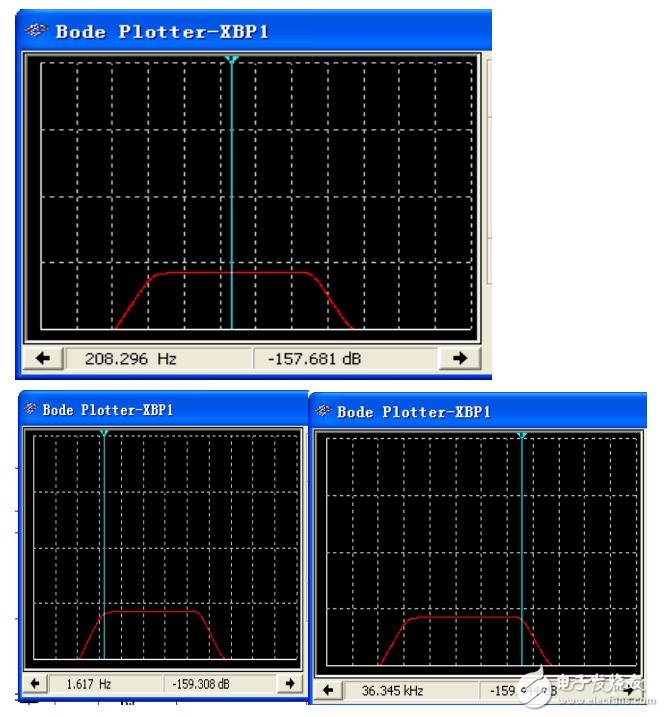

下面是我们的仿真结果:

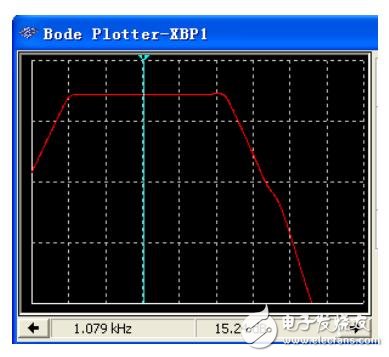

这幅图是我们在MulTIsim 10.0进行仿真时得到的波特图,其中给定

R9 = R10 = 8.2K

R13 = R14 = 8.2K

R4 = R12 = 4.7K

其它参数值如图所示,这也是我们组前期仿真过程中遗留下来的最不可原谅并且是最最核心的问题,在后面会对它做进一步说明。

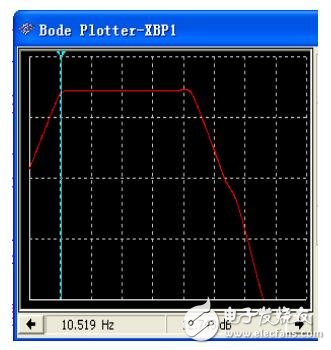

下面是我们的仿真结果:

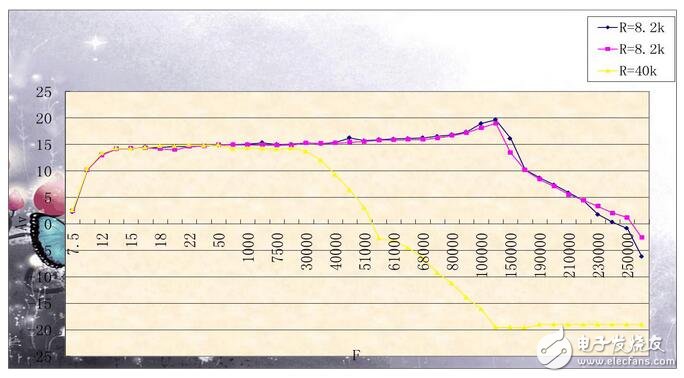

可以看到仿真出来的带宽已经非常宽了,上限频率很高,这与我们的初始仿真结果出现了很大的偏差。(初始仿真结果为:10.225Hz~61.743KHz)。

电路性能测试和改进

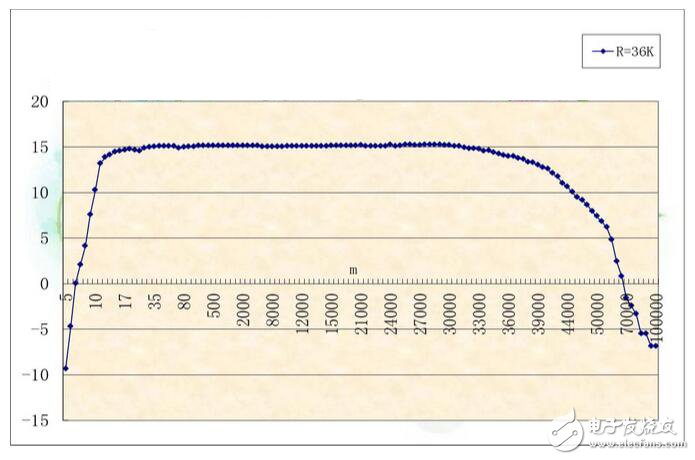

做出来的电路先出现了峰值:

电阻出了问题,改变阻值后:

再次改变阻值后:

带外抑制比不够:

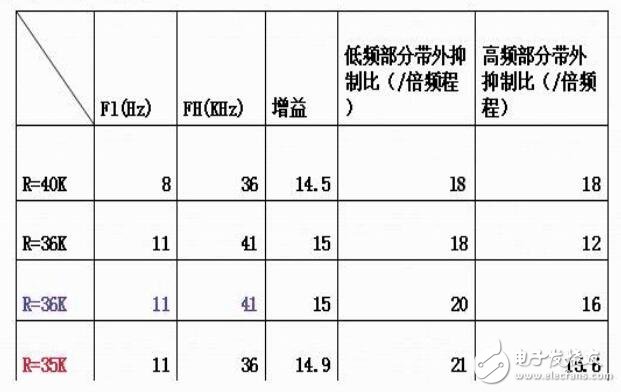

相关数据表

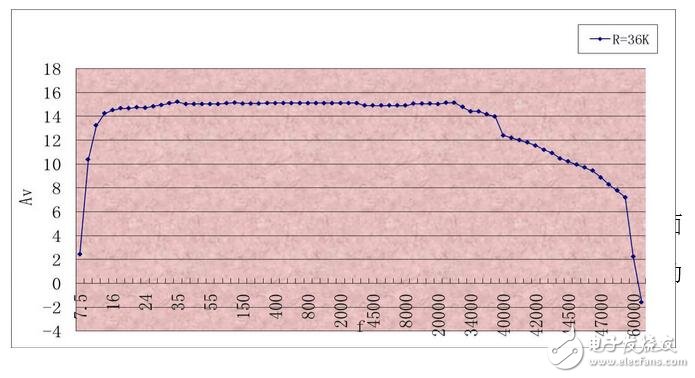

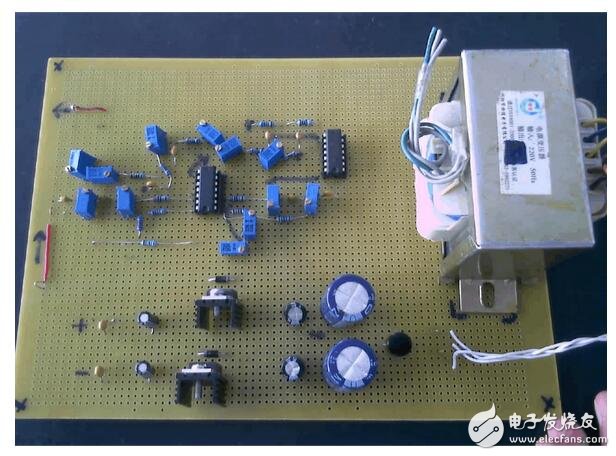

由此可以看出R的取值为40k或36k时,条件基本满足条件。下面所示是我在万能板上实际焊接出来的实物图:

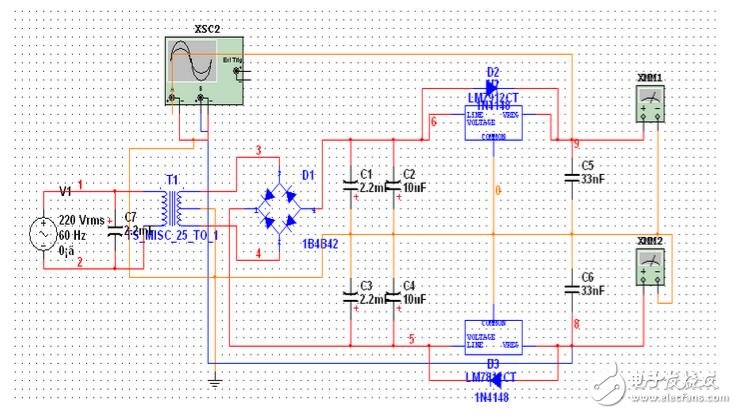

电源模块:

直流稳压电源的工作原理

电源是构成一个完整功放的重要组成部分,其稳定的向外电路提供能量,保证外电路能正常的进行工作。但一般地都是从市电经变压器降压而实现的,那么如何降压,如何把交流经某些元件变成直流,并保证其能稳定的输出是必须考虑的问题。

做为稳压电源它是由电源变压器、整流、滤波和稳压电路等四部分组成。电源变压器是将交流电网220v的电压变为所需要的电压值,然后通过整流电路将交流电压变成脉动的直流电压。而脉动的直流电压含有较大的纹波,必须通过滤波电路加以消除,从而得到平滑的直流电压。

A .变压器

变压器的种类有许多,单输出的双输出的,体型有大有小,输出电压、功率等依型号而定。外电路所需电压值、流过电源的电流、外电路的功率都将影响到电源输出电压的稳定性,因此输出电压、本身功率等都是必须考虑的,在本电路中我们选择双12v输出电压的变压器。

B .整流电路

要使交流电压变成直流电压,整流电路就是必须的。常见的整流电路有单相半波整流、单相全波整流、单相桥式整流和倍压整流电路。由于桥式整流电路输出电压高,纹波电压较小,管子所承受的最大反向电压较低,同时因电源变压器在正、负半周内都有电流供给负载,电源 变压器得到了充分的利用,效率较高。因此我们在此采用最大电流2A的整流桥。

C .滤波电路

滤波电路用于滤去整流输出电压中的纹波,一般由电抗元件组成。其工作机理是,点抗性元件在电路中有储能作用,并联的电容器C在电源供给的电压升高时,能把部分能量储有平波的作用。电感也有平波的作用,使负载电压比较平滑。电容滤波一般针对小功率电源,而电感滤波多用于大功率电源中。此电路中我们采用电容滤波方式。电容滤波时输出电压为U2=√2U1,其中U1为变压器输出电压,U2 为电容两端输出电压。

由于该电路采用双电源形式,我们将采取上下并联两组电容的形式来作为滤波电路。并且电容由大到小依次排列。第二级电容采用钽电解电容有效地防止了低频干扰成分对电路的干扰, 第三极电容采用独石电容防止了高频成分的干扰,同时也提高了电源的稳定性。

电源部分采用三端集成稳压块LM7812和LM7912制作,电路结构简单,电路中芯片所需电压为±12V,实际测得电压为11.86V和11.74V。我们在具体测量的时候选用此电源模块。

运放的选择

为了减少运放对滤波电路的负载效应,同时便于调整,我们刚开 始考虑选用LF412。这是一种具有JFET作为输入级的低失调、高输入阻抗运放。其输入阻抗可达1210Ω。单位带宽增益积为8MHz,能满足我们的要求,但因为此芯片大多为军用芯片,价位太高,所以我们选用了LM324,因为LM324系列器件为价格便宜的带有真差动输入的四运算放大器。与单电源应用场合的标准运算放大器相比,它们有一些显著优点。该四放大器可以工作在低到3.0伏或者高到32伏的电源下,静态电流为MC1741的静态电流的五分之一。共模输入范围包括负电源,因而消除了在许多应用场合中采用外部偏置元件的必要性。3dB带宽增益乘积:1.2MHz ,低功耗,已经可以满足我们的要求了。

电压跟随器

概括地讲,电压跟随器起缓冲、隔离、提高带载能力的作用。共集电路的输入高阻抗,输出低阻抗的特性,使得它在电路中可以起到阻抗匹配的作用,能够使得后一级的放大电路更好的工作。电压隔离器输出电压近似输入电压幅度,并对前级电路呈高阻状态,对后级电路呈低阻状态,因而对前后级电路起到“隔离”作用。电压跟随器常用作中间级,以“隔离”前后级之间的影响,此时称之为缓冲级。基本原理还是利用它的输入阻抗高和输出阻抗低之特点。电压跟随器的输入阻抗高、输出阻抗低特点,可以极端一点去理解,当输入阻抗很高时,就相当于对前级电路开路;当输出阻抗很低时,对后级电路就相当于一个恒压源,即输出电压不受后级电路阻抗影响。一个对前级电路相当于开路,输出电压又不受后级阻抗影响的电路当然具备隔离作用,即使前、后级电路之间互不影响。

利用电压跟随器的这些特点,我们在电路高低铜连接处增加了电压跟随器模块,是的电路性能大幅度优化,主要表现在通带内的平坦程度得以提升,带宽也有所增加。

存在问题解决情况

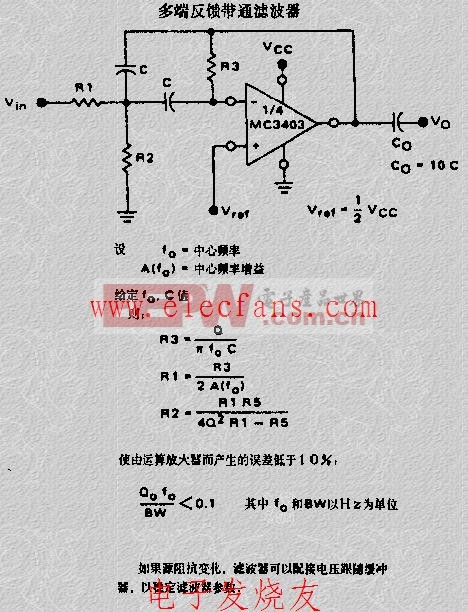

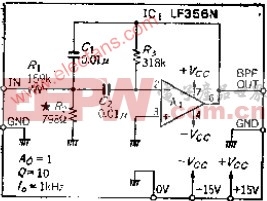

⑴ 滤波器的构架的选择在刚开始的原理建立及电路构架的确立时,我们也曾想过用两个二阶Delyiannis带通滤波器级联,也就是下面图中给出来的那样:

下面给出仿真得到的波特图:

由上图可以看到,当带宽可基本达标时,增益都到-157dB了,虽然我们的设计指标中没有增益限制,但我们不可能这么大倍数的衰减新号,所以我们放弃这种设计方案,转而采取高通与低通级联的方式,选用二阶Salley-key滤波电路为基础模块设计滤波器电路,在前面已做过重点说明,这里不再重复。

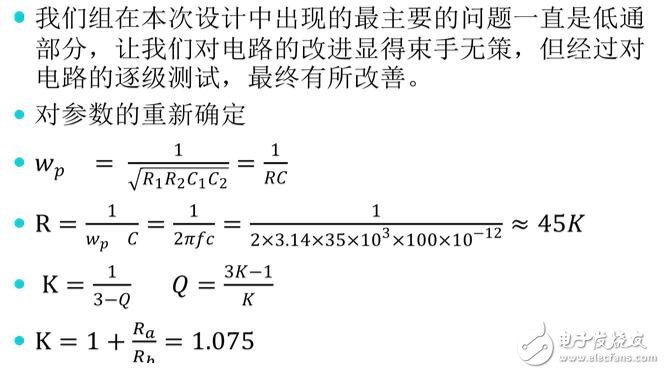

(2) 低通部分的改进由于在仿真阶段的疏忽和调节的盲目,使得地同参数出了很大问题,一直到实际电路搭接出来后还在为低通电路部分发愁。后来通过对仿真图的调节、实际电路的分块测试,低通滤波电路的不可行之处实实在在的摆在我们眼前,因此重新开始从计算开始,确立参数,在上面已经予以说明,但新的问题又出现了,高频部分波特图出现转折,且转折前后斜率不尽相同,在之前给出的方针和实测图中都有反映出来,其原因初步被判定为是两个二阶滤波电路频率不匹配,致使滤波通带没有能完全重合。

(3) 电源问题

我们的第二个电源出了一些问题,也耽误了很长时间,测量数据为:正电源11.6V、负电源为-22V.整流桥测过没出问题,电路都是通的,稳压块也换过,但一直没能解决,问题还是出在稳压块上,应该是被烧掉了。

(4) 带外抑制比

思路一:带外抑制比在比较精确的一组测量是几乎为20db,具体的思路是:由于电路是级联的,在高通部分他的带外抑制比比较高,但是第通的部分相应的低些,这时可以在他的低通部分在增加一个极点,使得在该点处他的下降先变化一次,这样就比较的陡了。

思路二:在电路设计的时候,我才用的电容比值太大了,达到了1000倍,这个可能是一个原因,导致带外衰减部分比较的低,此后我想过改变容值的方法来减小他们之间的系数,这样就可以使得他们的灵敏度减小,电路性能得到改善。

评论