分解MSP430G2553的时钟系统

MSP430G2553系统时钟和振荡器

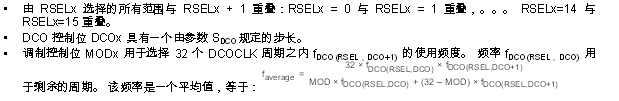

本文引用地址:https://www.eepw.com.cn/article/201710/366354.htm时钟系统由基本时钟模块提供支持,此时钟模块支持一个32768Hz手表晶体振荡器、一个内部超低功耗低频振荡器和一个内部数字控制振荡器(DCO)。基本时钟模块专为同时满足低系统成本及低功耗要求而设计。内部DCO提供了一个快速接通时钟源并可在不到1µs的时间里实现稳定。基本时钟模块提供了以下时钟信号:

•辅助时钟(ACLK),此时钟由一个32768Hz手表晶振或内部LF振荡器提供信号源。

•主时钟(MCLK),CPU所采用的系统时钟。

•系统子时钟(SMCLK),外设模块所采用的子系统时钟。

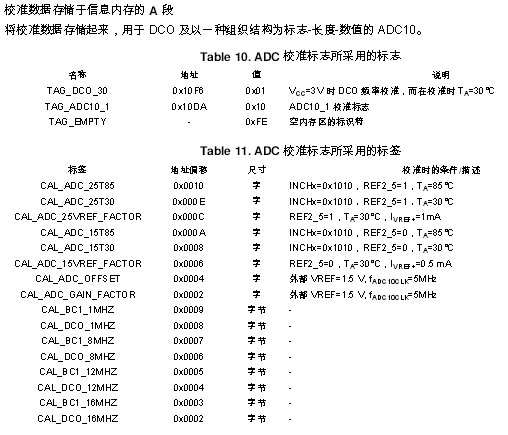

用于校准DCO输出频率的DCO设定值存储于信息内存的A段中。

主DCO特性

1,MSP430G2553能做到超低功耗,合理的时钟模块是功不可没的。但是功能强大的时钟模块设置起来也相对复杂一些。

2,MSP430G2553的时钟源有:

(1),外接低频晶振LFXT1CLK:低频模式接手表晶体32768Hz,高频模式450KHz~8MHz;

(2),外接高速晶振XT2CLK:8MHz;

(3),内部数字控制振荡器DCO:是一个可控的RC振荡器,频率在0~16MHz;

(4),超低功耗低频振荡器VLO:不可控,4~20KHz 典型值为12KHz;

3,时钟模块:430的时钟模块有MCLK SMCLK ACLK :

(1),主系统时钟MCLK:提供给MSP430的CPU时钟。可以来自LFXT1CLK XT2CLK DCO VLO可选,默认为DCO。

(2),子系统时钟SMCLK: 提供给高速外设。可以来自LFXT1CLK XT2CLK DCO VLO可选,默认为DCO。

(3),辅助系统时钟ACLK:提供给低速外设。可来自LFXT1CLK VLO。

4,内部的振荡器DCO和VLO提供的时钟频率不是很精确,随外部环境变化较大。

7,系统上电后默认使用的是DCO时钟,DCO默认的频率大概为800KHz,但我用示波器观察的为1.086MHz左右,当DCO设置的过高时,用示波器可以看到波形不再是方波,而是类似于正弦波。

DCO可以用CCS提供的宏定义进行相对比较精确的设置,如下:

DCOCTL = CALDCO_12MHZ; //DCO设为12MHz 这种方法设DCO频率比较精确,实际测得为12.08MHz左右 正弦波

BCSCTL1 = CALBC1_12MHZ;

用这种方法可以设置1,8,12,16MHz

宏定义如下:

#ifndef __DisableCalData

SFR_8BIT(CALDCO_16MHZ);

SFR_8BIT(CALBC1_16MHZ);

SFR_8BIT(CALDCO_12MHZ);

SFR_8BIT(CALBC1_12MHZ);

SFR_8BIT(CALDCO_8MHZ);

SFR_8BIT(CALBC1_8MHZ);

SFR_8BIT(CALDCO_1MHZ);

SFR_8BIT(CALBC1_1MHZ);

#endif

评论