基于PXI平台的下一代半导体ATE解决方案

半导体测试行业现状

本文引用地址:https://www.eepw.com.cn/article/201708/363140.htm电子行业正处于不断的压力下必须降低其制造成本。上市时间给半导体制造商很大的压力,在新产品投入市场后的很短时间内,利润是最高的,随后,由于竞争者开发了类似底价产品,利润水平开始下降。开发一个有效的节省费用的测试程序往往是阻碍新产品投入批量生产的瓶颈。

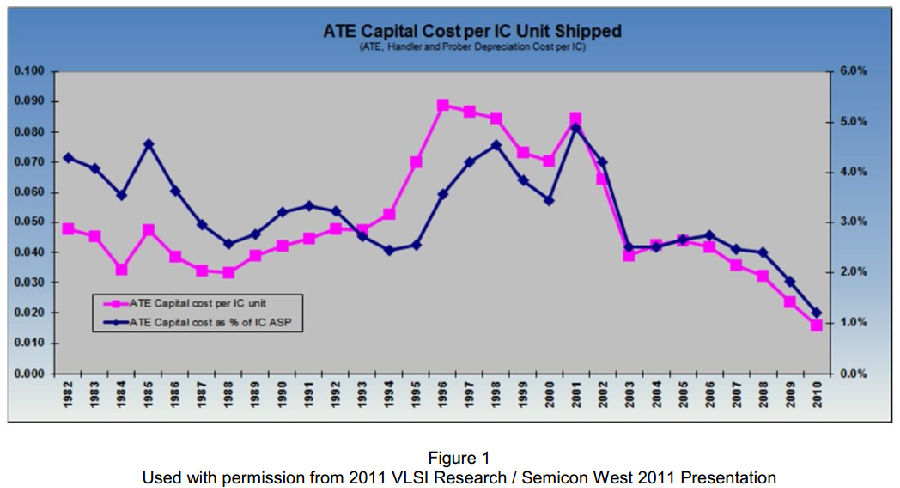

对于半导体供应商来说,其中测试成本一直被视为没有“增值”的成本。如图1所示,ATE资本成本占IC平均销售价格(ASP)的百分比逐渐变小 - 从2001年的5%上升到2010年的约1%。然而,整体器件的ASP也在减少,意味着在绝对成本方面,测试成本需要以与器件ASAP的减少相同或更大的速率降低,这使得测试工程师面临更大的压力以找到更具成本效益的测试解决方案。

实际情况是,通过采用诸如并行测试(也叫多点测试)等技术来提高传统或“big ATE”测试系统利用率,只会在测试费用方面产生有限的改进,而不真正解决测试系统成本的核心问题。对于开发实验室,故障分析实验室或小批量生产的测试需求,多站点测试策略不会提高测试的经济性。

当今的半导体器件包括各种数字,存储器,模拟,混合信号和RF模块等,所有这些都集成在单个封装或SoC(system on chip,系统芯片)中。 结果是,测试解决方案不仅必须是成本有效的,而且必须灵活以便解决包括逻辑,存储器,模拟,MEM和RF模块的一系列电路类型的测试需求。 测试解决方案要能够为工程师提供成本有效的自动化设计验证,故障分析和试生产测试活动的能力,而无需使用昂贵的“big ATE”。

今天的测试工程师面临的挑战是创建新的测试方法和系统,可以显著的降低测试成本,以及解决可配置,灵活的测试解决方案的需求。基于PXI(Compact PCI Extensions for Instrumentation)数字,模拟和射频测试产品和系统的最新进展使测试工程师能够利用PXI平台满足一系列ATE设备的测试需求。特别是,PXI数字产品中提供每引脚具备参数测量单元(PMU)功能,现在提供具有高价值和性能的ATE半导体测试功能。此外,PXI测试系统为测试工程师提供了经济高效的ATE,可用于故障分析,原型设备验证和试验/早期生产运行 - 允许“big iron”ATE专注于批量生产测试应用程序,同时在紧凑和可配置的平台中提供工程测试功能。

半导体测试要求

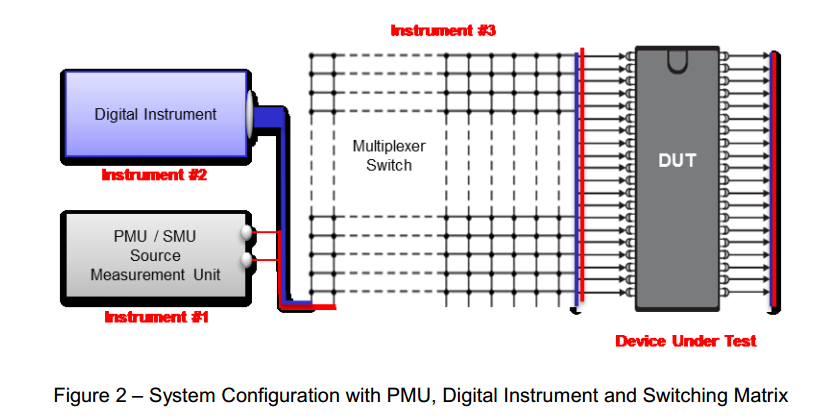

数字和混合信号器件的基本测试需求包括直流参数测试和功能测试。 对于DC测试,必须表征器件的引脚,需要一个PMU(参数测量单元)。 如果使用单个PMU,需要通过多路复用开关能够访问的所有器件的引脚,以实现激励电压/测量电流或激励电流/测量电压。 一旦DC参数测试完成,就可以执行器件的功能测试。在这种情况下,具有足够深的存储器,每通道可编程性(电压,负载和方向)和实时比较的数字化仪成为执行功能测试的关键。 解决这些功能的基本配置如图2所示。

如图2所示的单个PMU,开关网络(多路复用)和数字化仪的组合对于中等到高引脚数器件而言,迅速变得笨重且性能受限。此外,用于DC测试的开关时间和编程/测量时间的组合很轻易就需要10甚至100毫秒,用于DC参数测试的时间就会变得很长。

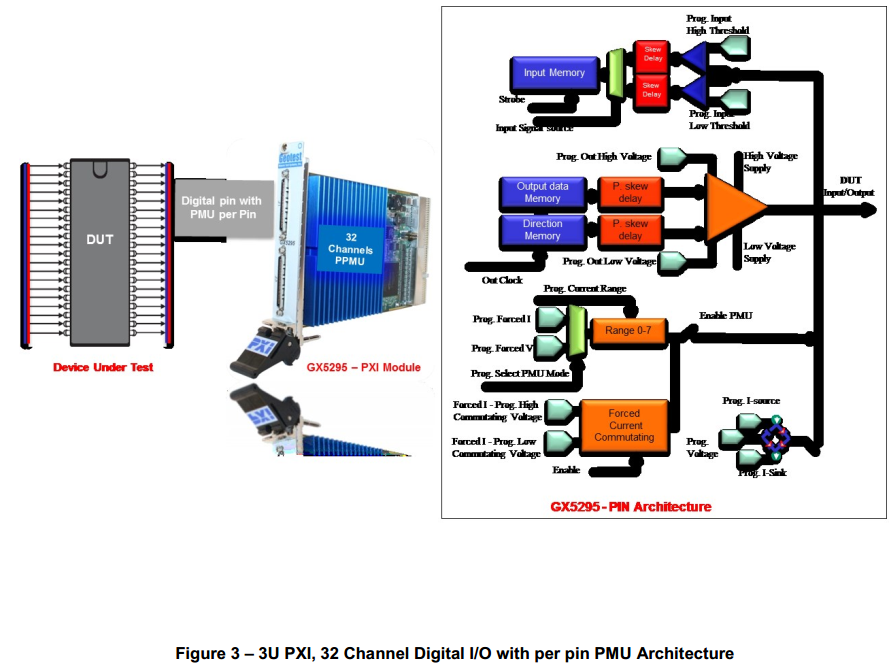

一个更好的解决方案和专业的ATE或“big iron”系统通常使用的是每个引脚或通道包含一个PMU,从而提供出众的测试性能(包括速度和测量精度)。 图3详细说明了每引脚配置的PMU的数字仪器的架构。

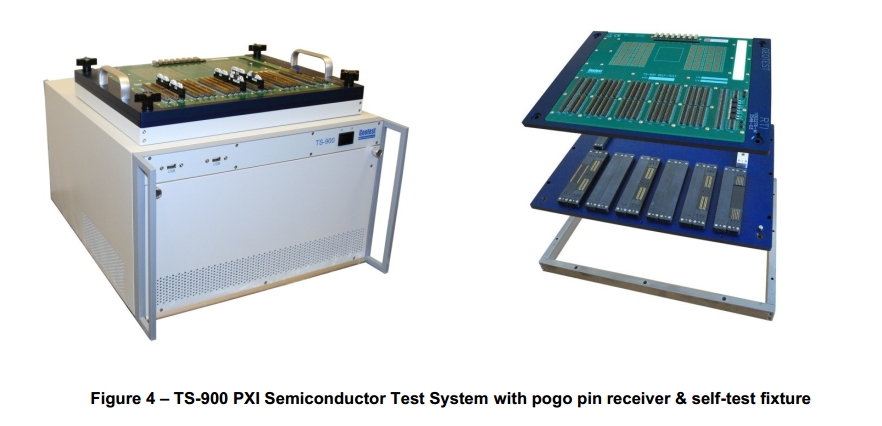

现今,Marvintest的半导体测试解决方案的GX5295具有32通道数字I / O和每引脚PMU架构,可作为紧凑型PXI测试平台的一部分,例如TS-900半导体测试系统 - 为用户提供多通道数数字和 混合信号测试系并且具有小型,紧凑的PXI机箱占地面积。 (图4)

直流参数测试

如前所述,PMU可以使用两种模式之一,以对数字设备的输入和输出线执行直流特性测试:

§ 强制电压/测量电流

使用这种方法,PMU施加恒定电压并使用其板载测量能力来测量被测试的设备/引脚所汲取的电流,还可以测量由PMU提供的电压。

§ 强制电流/测量电压

使用这种方法,PMU强制恒定电流流过器件或从器件引脚吸收恒定电流,然后测量电压,还可以测量PMU的灌电流/源电流。

通过将每个通道的PMU与数字测试功能组合在一个仪器中,可以显著简化对数字和混合信号器件执行的一系列直流测试。在半导体器件上执行的常见直流测试包括:

n VIH:(高电平输入)施加到器件输入的最小正电压,器件将被逻辑高接受

n VIL:(低电平输入)施加到器件输入的最大正电压,器件将被逻辑低接受

n VOL:(低电平输出)器件输出的最大正电压定义为“保证”指定负载电流下的最大低正电平

n VOH:(高电平输出)器件输出的最小正电压定义为“保证”指定负载电流下的最小高正电平

n IIL:(低电平输入漏电流)当输入为逻辑低电平时测量的输入漏电流

n IIH:(高电平输入漏电流)当输入为逻辑高电平时测量的输入漏电流

n IOS(H):(高电平短路输出电流)输出为逻辑高电平时的短路输出电流

n IOS(L):(低电平短路输出电流)输出处于逻辑低状态时的短路输出电流

示例:VOH,VOL和IOS测试

输出电压电平测试用于在指定负载条件下使用时验证数字输出的操作。它们还可以用于模拟最差情况下的负载条件,以观察在输出负载超过其指定极限时(例如,当对地短路时)DUT的工作情况。当执行这些类型的测试时,应选择不会损坏被测器件(DUT)的测试电流范围以充分测试输出。

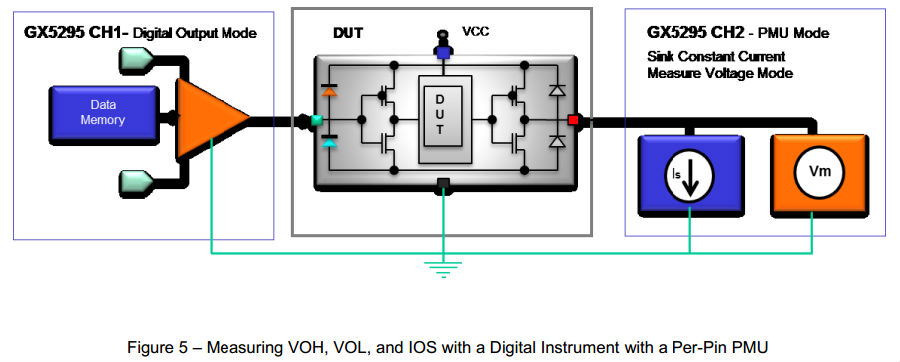

以下示例显示如何对数字输出执行VOH测试。此测试的目的是确保DUT在提供其最大额定驱动电流的同时保持高于其指定输出高电平的输出电压。对于该测试,PMU被编程为从DUT吸收电流,模拟负载条件。图5显示了DUT和数字仪器的连接方式。

为了执行该测试,DUT被通电,并且仪器的一个通道(在该示例中为Ch1)用于施加输入逻辑电平,该输入逻辑电平迫使DUT的输出为逻辑高。请注意,每个仪器通道可以配置为PMU或数字I / O模式,提供所需的灵活性和功能以支持VOH,VOL和IOS测试,这些测试要求在执行PMU测量之前将器件的输出编程为正确的状态。

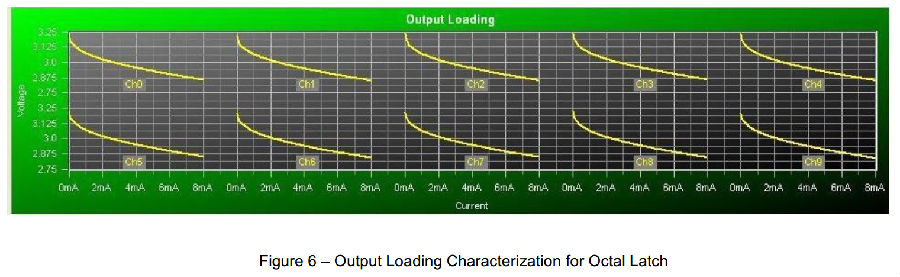

第二个数字通道(本例中为Ch2)被设置为PMU强制电流/测量电压模式,初始电流吸收值不会损坏DUT输出引脚。然后,PMU被编程为使器件电流从最小到最大测试值。在每个测试电流值下,测量DUT的输出电压,以确保其处于逻辑高电平的指定电压范围内。还可以测量实际PMU测试电流,并用于为每个提供负载与输出电压电平曲线(参见图6)。在这种情况下,被测器件(DUT)是八进制锁存器,每个输出都测试输出电平与电流负载。

上述测试技术也可用于VOL和IOS测试。 对于VOL测试,DUT的输出将被编程为逻辑低电平,并且在测量输出电压电平时将输出施加到输出的指定负载,以确保其在器件的规格范围内。 对于IOS参数,输出将被编程为指定的逻辑状态,应用于输出的短路和测量的结果电流。

示例:漏电流测试(IIL,IIH)和V-I测试

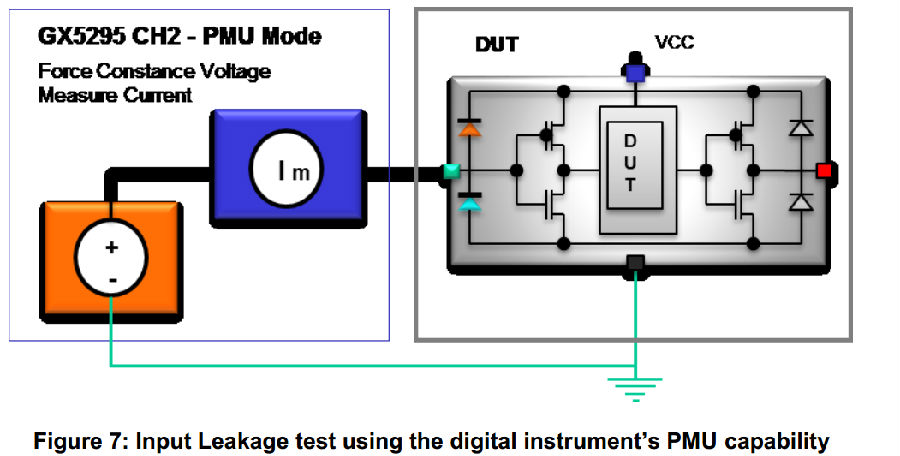

测试器件的输入包括泄漏电流测试以及表征DUT的每个输入端上的保护二极管。 这些测试通过在DUT输入引脚上逐步施加恒定电压并在每个步骤测量输入电流来执行(图7)。 由于漏电流通常在uA范围内,PMU应设置为更灵敏的电流范围,以实现更准确的测量。

要进行漏电流测试,DUT将被通电,PMU引脚将设置为强制电压/测量电流模式。在每个输入电压设置下,PMU测量输入所汲取的电流,然后根据DUT规格验证该值。也可以测量PMU正在采集的实际测试电压。此处所示的测试技术也可用于VIL和VIH测试。

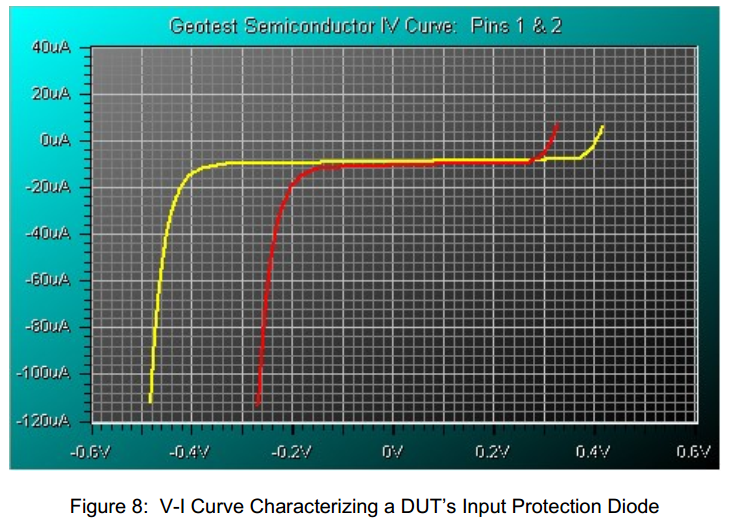

用于测量/表征连接到设备与地和VCC的输入保护二极管引脚,PMU被配置为强制电压/测量电流,其中电压依次以小增量步进以产生每个二极管的V-I曲线。 图8显示了TTL数字器件的保护二极管的V-I曲线。 注意器件在约0.4伏的结电压下开始导通。

半导体测试自动化

今天的测试工程师正在不断的压力下缩短测试开发时间,并在创建测试程序时变得更有效率。 测试开发框架与可以自动创建和执行设备测试的软件工具结合在一起,为测试工程师提供了强大的软件开发环境,以提高测试开发和部署生产力。 例如,Marvin测试解决方案的TS-900包括ATEasy - 一个用于管理程序开发和部署的全功能测试执行环境,以及简化了标准测试的创建和执行的测试库,它提供了用于绘制IV特性曲线和支持二维Shmoo图的交互式工具。

直流参数自动测试创建

ICEasy的库包括一整套测试功能,用于表征器件的输入和输出直流特性。利用TS-900的每引脚PMU功能,用户能够快速创建用于以下类型测试的测试程序:

§ Openand Shorts

§ Input Leakage (IIL, IIH)

§ Input Voltage Threshold (VIH, VIL)

§ Output Short Circuit (IOSH, IOSL)

§ Output Voltage Threshold (VOH, VOL)

§ Power Consumption (IDD, IDDQ)

这些预配置的测试结合了ICEasy的器件引脚和引脚组映射功能,为用户提供了一种简单而简化的方法,可以将特定的器件引脚分配测试以及指定每个测试的通过/失败限制,而无需执行低级别的仪器设置和控制。 结果是更快的测试创建和更短的测试时间。

I-V Curve Tool

ICEasy的电流 - 电压(I-V)曲线工具使用户能够以图形方式绘制器件的ESD二极管的I-V特性。 该测试方法可以深入了解可能影响设备I/O引脚的器件故障机制,如电应力(EOS),静电放电(ESD),接合线问题和封装问题。 而且最近,使用I-V曲线图作为“阻抗特征”可能有助于识别假冒产品,其中将已知真实部件的阻抗或I-V标签出来并与可疑部件形成对比。

ICEasy的I-V曲线工具允许用户轻松设置电压和电流范围以及步进增量以及按名称定义要测试的特定引脚(或引脚)。 此外,所有I/O引脚可以绘制在同一个图形上,提供了一种比较所有器件I-V曲线的简单方法。 (见图9)绘图数据也可以通过TS-900的测试执行环境(ATEasy)轻松导出。 易于测量I-V特性并绘制结果的能力是故障分析和设计验证应用的关键特性。

Shmoo Plot Tool

ICEasy的Shmoo绘图工具允许用户在X和Y轴上轻松更改测试参数,无需编程 - 允许测试工程师直观地观察被测设备的通过/失败操作范围。 TS-900的Shmoo绘图功能是设备表征和鉴定的公认测试方法,为用户提供了强大的设计验证和早期生产测试资格认证技术。 ICEasy的Shmoo工具支持自动化和交互式控制,允许用户即时更改参数或通过TS-900的测试管理器(ATEasy)控制测试以及记录生成的数据。 如图10所示,Shmoo工具允许用户轻松地改变测试参数范围,例如VCC,时钟频率,边沿放置,输入电平等,以便完全表征器件的通过/失败操作条件。

PXI半导体测试系统

考虑解决半导体测试需求的仪器和软件的可用性,测试工程师现在可以选择采用PXI架构来满足当前和未来的ATE要求。 诸如TS-900的系统为专有的ATE系统提供了可比较的功能和性能,如今,可以在使用16块32通道GX5295数字I/O(每引脚带PMU)的紧凑型20插槽PXI机箱中支持多达512个数字I / O通道。

此外,通过在PXI平台上进行标准化,用户可以通过结合包括SMU,数字化仪,AWG以及RF信号源和分析仪在内的各种仪器来扩充系统。

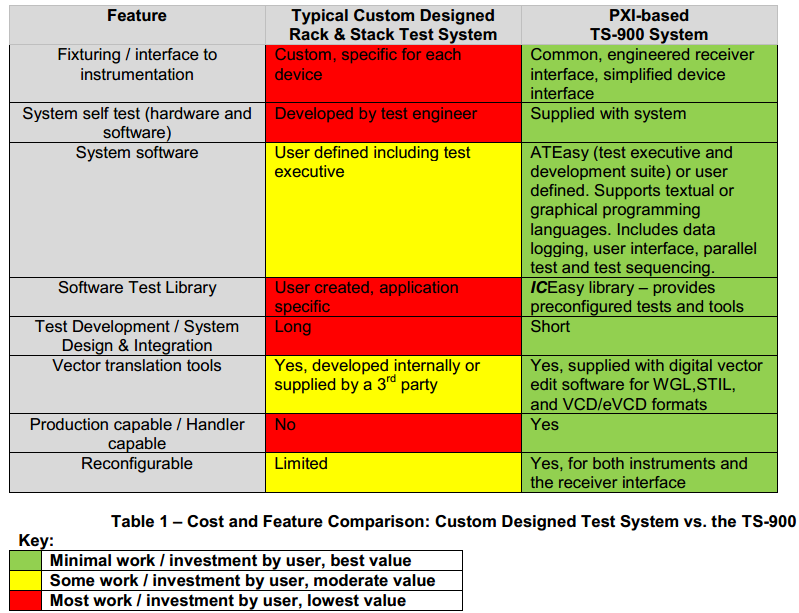

TS-900具有集成的高性能模块化接收器接口,是用户希望优化产品生命周期整体测试策略的理想平台。如表1所示,与手动或半自动台式测试配置相比,TS-900作为新产品具有显着的优势。采用TS-900等测试系统可为工程师提供更快更自动化的过程,用于表征器件,从而将器件表征和验证从几周缩短到几天。此外,TS-900可以有效地解决早期生产设备的测试成本,而不用昂贵的资本成本(测试时间),固定和长时间的测试开发时间,而不依赖“大铁”ATE。凭借广泛的软件工具和直观的软件开发/测试执行环境(ATEasy),TS-900满足了测试平台的需求,可以弥补工程实验室和批量生产测试之间的测试差距。

评论