一种面向系统芯片的FPGA协同验证方法

1引 言

随着SOC(系统芯片)设计任务复杂度的提高,功能验证已成为系统设计中最大的瓶颈。对于百万门级的SOC芯片,每次投片的NRE是巨大的,预计,在未来两年,验证在设计中所占的比重将达到50%以上。由于SOC系统普遍涉及实时环境下的应用,现有的仿真工具不可能解决所有的功能验证问题,有必要利用FPGA在接近实时的条件下进行软硬件协同验证。基于多片FPGA实现的验证往往面临系统分割的挑战。盲目的、缺少优化的系统分割,不仅很可能在综合、分割、板上实现出现多次反复,浪费大量的时间,而且也难以保证FPGA验证结果与ASIC设计的一致性。

本文在传统边界划分的基础上,通过静态时序分析工具,利用关键路径时延信息,对分割过程进行约束。新的验证策略注重系统分割在时序收敛、面积、数量和管脚数等方面的平衡,目的是使分割结果趋于合理,验证环境更加接近SOC设计原型,避免传统FPGA验证在系统分割、综合和设计等环节的反复迭代,实现了验证和SOC开发调试的同步。文章同时讨论了该方法对于信号完整性分析的贡献。

最后,通过一个分割实例,就分割效率与传统方法进行了对比。

2传统的FPGA验证流程

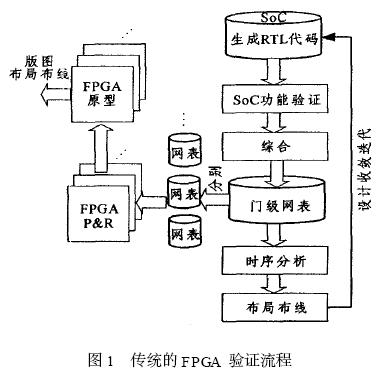

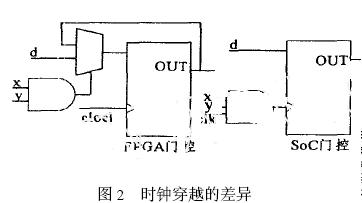

传统的FPGA验证流程如图1所示。这种综合与分割相互无关的验证流程存在诸多缺陷。首先,从ASIC结构到FPGA结构的转换存在差异,例如,很多SOC系统设计经常会处理时钟信号穿越“与”、“或”、“与非”等门的情况,如图2所示。

此时,综合工具一般不会自动选用FPGA专有的时钟结构,其结果是产生时钟歪斜(clockskew),导致ASIC代码和综合出来的FPGA在功能上不一致。即,如果忽略时钟树在时钟域范围的扩散效应,分割时很有可能导致从ASIC结构到FPGA结构的转换的不一致。这个例子同时说明,类似的问题同样会在其它电路网络中发生,RTL设计在满足时序收敛要求的开发过程中,无论采用的是动态验证还是静态验证技术,都应当重视电路网络中路径延迟的影响。传统FPGA验证的系统分区分割策略通常采用沿自然边界划分的方式,设计者主观上通常过分依赖几何拓扑关系和层次化的系统模块划分,特别是忽略了分割过程与综合和时序分析的关系。这种过于简单化的分割策略很可能会导致不合理的结果,FPGA验证所映射的可能是没有意义的ASIC结构。

3 基于关键路径时延约束的FPGA验证流程

3.1关键路径时延提取

关于FPGA验证,我们认为,高效率的系统分割至少应该具备两个条件:找到最佳的分割点和在系统级上逼近设计。首先,分割在技术上是可行的,允许将设计划分为多个适于单个FPGA实现的模块,在接近实时的环境下进行验证。目前最大的FP2GA标准封装可提供400到440个I#710;O,对I#710;O的管脚数目的支持不再成为分割的瓶颈,这也为传统的沿着内核或模块的边界进行直接划分提供了空间。在确定最佳分割点的反复迭代过程中,我们发现,利用静态时序分析获得的关键路径时延信息,完全可以用于实现收敛性更好的系统分割。静态时序分析是一种检查ASIC设计逻辑和时序的工具,其主要目的是计算各通路的性能,识别可靠的踪迹,诊断建立和保持时间的配合。静态时序分析会分析报告所有关键路径,包括一些重要的调试信息,比如每个网络节点的扇出或容性负载等。

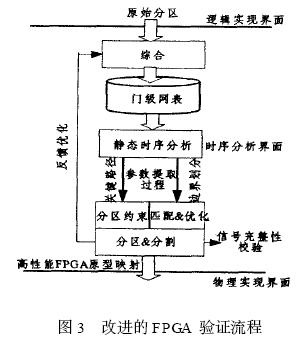

通过实践发现,利用关键路径时延信息对系统分割和综合进行约束,可以保证分割按照相对确定的标准进行,获得时序优化的结果,从而有效地减少了功能验证过程中的反复。同时,为使验证过程更为接近ASIC功能,分割时尽量做到面积、晶体管数量和管脚的匹配,保证分割的结果对面积和I#710;O利用而言都是合理的故障定位要求。这些措施均优化了FPGA验证过程,所获得的综合分区和时序收敛结果更好,为最终物理版图验证铺平了道路。我们采用的具体办法是,首先根据静态时序分析报告确定关键路径的分区门限,然后原则上沿着功能边界将延迟长的路径分割到同一个FPGA分区,通过更进一步的综合分区,获得收敛性更好的路径。其结果是,可以将需要验证的探测点更多地分割到FPGA边界,达到提高I#710;O利用率的目的。显然,高的I#710;O利用率能够有效地拓宽FPGA验证范围。经过改进的FPGA验证流程如图3所示。

该流程的优势在于:分割是按照确定的标准进行的,针对传统验证流程的时序分析,仅仅对布局布线有效的缺陷,围绕时序分析这个中心,将逻辑实现和物理实现有机地结合在一起,着重考虑了关键路径时延对FPGA分割效率的影响,使分割结果更为合理。此外,新流程通过在综合、时序仿真过程、分割验证中交互进行静态时序分析,实现了综合、分割、验证、设计的高效同步。在关键的时延信息和边界条件约束下,经过迭代,功能块延时和布线延时,能够取得与实际比较一致的效果,多片FPGA实现时的代码修改量也得到减少。Xilinx、Altera等FPGA生产商大多支持兼容的第三方时序分析工具,应用时选用Synopsys的PrimeTime进行静态时序分析。该工具的优势在于不要求用户输入激励或测试矢量,可通过调用db格式的网表文件,方便地查看关键路径或指定通路的时序。

3.2 信号完整性的保证

新流程对SOC验证效率的另一贡献,是提供了一种在代码级优化信号完整性的途径,有利于在综合和板级验证的过程中对信号完整性实施动态的控制,及早发现设计中隐藏的严重的信号完整性缺陷。信号完整性(SignalIntegrity,SI)是指传输线上的信号质量及信号定时的准确性。SOC芯片设计一般要求数据必须在时钟触发沿建立之前稳定,才能保证逻辑控制的准确性。应当注意到,摩尔定律所隐藏的另一层含义是,RTL系统设计要随时应付工艺实现条件的变化,因为设计不可能总是针对最新的工艺条件实现的。

新的工艺条件可能会给原设计带来影响。例如,设计从0125Lm工艺转向0118Lm工艺实现时,就存在信号完整性问题。随着系统速度和处理带宽的增加,信号完整性的影响会表现得更加突出。另一方面,传统的RTL设计在设计和验证环节存在与信号完整性分析脱节的现象,难以发现并修正信号完整性缺陷,或者在向更高标准工艺迁移时,由于代码修改量太大,势必加重系统验证等环节的负担,从而使设计效率大打折扣。因此,我们的出发点是,争取以最小的代码修改量,实现RTL代码与FPGA的直接映射,保证FPGA功能验证的要求;同时,将信号完整性的影响在验证过程中以更直观的方式体现出来。

分析表明,最直观的信号完整性问题通常与电路模块之间的互连点有关,这在静态时序分析中实际上有所反映。特别需要指出的是,新的FPGA验证流程是建立在经过优化的系统分割基础上的。正如上一节所指出,延迟长的路径基本约束在同一个FPGA分区。经过这样的优化处理,实际上,一方面是对信号完整性有一定的优化;另一方面,由于I#710;O利用率的提高,更多的故障探测点分割到了FPGA的边界,信号完整性在协同验证中会得到更多的反映,通过软件全速仿真,比较容易查找和定位设计缺陷,及早消除设计隐患;同时,为RTL代码的动态优化提供了依据,有利于在设计前期尽量减少信号完整性缺陷,使之适应工艺条件变化的能力更强,提高设计的稳健性。通过采取以上措施,我们在原SOC设计的基础上,以较小的代码修改量,实现了从0125Lm向0118LmCMOS工艺的平滑过渡,并通过了系统后仿真。

4 系统分割验证结果

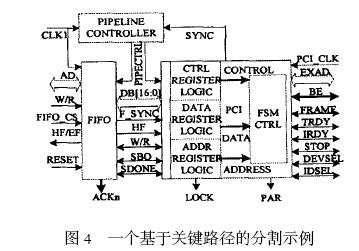

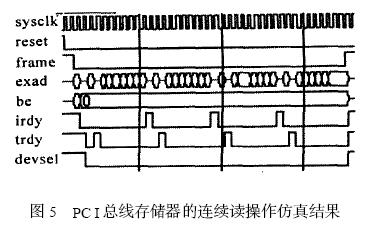

FPGA分割选用XilinxISE基于网表的集成验证环境,采用三种XC4000系列器件(XC4003、XC4005、XC4010)生成验证原型。该系列器件能生允许范围内的任意频率,可方便地提取片上和片外的精确50#710;50占空比的时钟,时钟边缘的定时精度达到1%。加之经过改进的时钟布线,验证环境比较接近高性能SOC的实际要求,能够保证验证环境与SOC系统保持最大限度的一致。图4是采用地址#710;数据复用实现的PCI接口模块的FPGA分割结果。其中,PCI控制单元采用两级控制流水方式实现与FIFO的高速数据交换,流水线控制信号完全约束在FPGA边界内部。图5是FPGA在布局布线后,50MHz系统时钟下PCI接口64字节数据缓冲存储器读操作的后仿真结果。

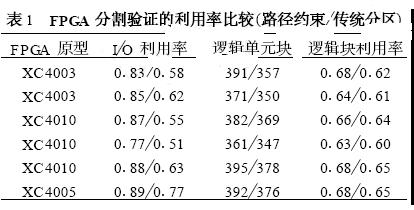

这种更为准确的分割验证同样会给板级测试带来方便。硬件仿真时,可以利用逻辑分析仪的数据接口测试流到探测头的信号,也可以通过串口或以太网接口对逻辑分析信道进行采集分析,便捷地测试FPGA之间的传递信号。经过改善的FPGA分割验证策略比较准确地反映了信号网中的路由拓扑,包括FPGA内部组合逻辑延迟、信号通过FPGA边界所需的时间;故障的定位也相对容易,某些故障还可以提前预知。在进一步的验证工作中,使用了6片XC4000对一个基于Verilog语言实现的的SOC系统(包括VLIW处理器核、总线控制器、I#710;O接口等)进行了分割(设计是以较小粒度的方式实现的,这样分割效果更为理想)。全芯片软件固化激励测试的结果与RTL测试结果完全一致。表1列出了改进方案与传统分割结果的数据对比。结果表明,I#710;O利用率有明显的提高,逻辑控制块的利用率也有所改进,进一步证明了方案的有效性。

5结 论

本文探讨了一种经过优化的SOC系统的FP2GA协同验证策略,依靠静态时序分析工具,利用关键路径时延对分割过程进行约束,显著改善了传统的沿自然边界分割的效率,验证结果更为接近SOC运行环境。新的协同验证流程实现了SOC设计与FPGA验证的同步,减少了不必要的反复迭代环节,有利于排除系统设计阶段可能导致系统失效的因素,加大了系统设计生产调试一次成功的可能性。

评论