DH中STM-1/TU-12解复用的设计及FPGA实现

SDH(Synchronous Digital Hierarchy)作为当今世界信息领域在传输技术方面的发展和应用的热点,其有效地结合了高速大容量光纤传输技术和智能网络技术。不仅充分显现出全球统一标准的接口、光纤通信容量大、高可靠的自愈能力、低成本、抗干扰能力强、保密性好等优点,而且突现出其复分接简单、电路调度和网络管理方式灵活、管理信息丰富等技术优越性。为能与现有的准同步数字体系(PDH)网络兼容,因此对2.048Mb/s的E1信号的支持就尤为重要。SDH采用标准的一套信息结构等级,其基本信号传输结构等级为同步传输模块STM-1,对应速率是155.52Mb/s。从SDH中解复用出E1信号,是实现PDH在SDH上兼容的重点和难点。

本文涉及的工作基于SDH帧结构.综合运用了并行帧同步码组检测、并行解扰码、段开销处理、指针解释与调整、VC-4抽取处理、TU-12支路抽取处理等技术,用以最终完成从STM-1中抽取TU-12支路的处理过程。

以下详细介绍STM-1/TU-12解复用的设计与实现。笔者以支路净荷处理作为主线,根据STM-1的帧结构确定了具体电路的实现方案。本文的创新之处在于系统地实现了从STM-1到TU-12支路的解复用详细过程,通过并行化处理方式与简化,把若干复杂模块的设计集中在一个系统中。另外对VC-4和TU-12进行系统化抽取处理和FIFO缓存,旨在降低电路规模和增加处理效率。

2设计思想

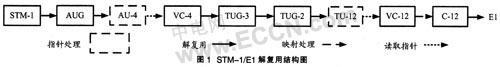

根据ITU-TG.707协议推荐,STM-1/E1解复用结构如图1所示。鉴于图中解复用过程,STM-l到TU-12需一次指针处理AU-PTR、若干次解复用操作。对本设计中从VC-4中抽取TU-12的过程.根据需提取的目标TU-12的Number(0-62)号码.直接就可完成VC-4到TU-12的提取过程,无需TUG-3和TUG-2的中间过渡。本系统设计据此进行简化。

STM-1的帧结构为9行270列的数据块,传输时由左向右,由上至下顺序发送。每帧的周期为125微秒。因为TU在VC-4中所占据的列是固定的,由于指针调整的存在,TU在STM-1中所占据的列并不固定。从STM-1中抽取TU-12时应首先完成对VC-4的解复用,然后再对VC-4中抽取其对应的列。另外由于指针的缘故,高阶虚容器VC可以有微小的频率和相位差异,因此处理高阶VC需要指针解释。

对于一个完整的STM-1/E1过程:经过光电转换的STM-1信号进入接收端,再经时钟和数据恢复、串/并转换、帧定位、BIP-8校验比较、并行解扰码、BIP-24校验比较.进入段开销处理阶段。此后经过通道开销处理、指针解释及调整、净荷定位后,定位后的净荷即完成解复用。该过程的原理如图2所示。

段开销处理中,再生段和复用段的误码检测.对应使用BIP-8、BIP-24校验算法。通过AU-4处的指针解释,准确抽取出VC-4,进而最后准确抽取出TU-12。

本设计的实现目标:

(1)将输入的STM-1信号字节串行流中的管理单元AU-4支路净荷,以VC-4的形式输出,并进一步将低阶支路TU-12净荷转移到相应输出支路单元中。

(2)处理管理单元指针,补偿STM-1帧与高阶虚容器速率间的准同步关系。

(3)检测管理单元指针的指针丢失(LOS)、告警指示、新数据标识NDF,给出指针工作状态,确定其调整方式。

(4)误码检测B1(再生段层的误码检测)、B2(复用段层的误码检测)、B3(VC4误码性能,通道BIP-8码)。

(5)利用搜捕校核/同步保护的措施(置位同步法),识别帧同步状态。

3模块设计

STM-1/TU-12具体实现电路可划分为5个功能模块,按其在解复用中的先后顺序加以介绍,其中每个功能模块还可划分为若干子功能模块。

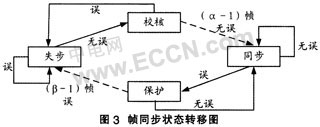

(1)并行帧同步码组检测模块同步码组长度n、校核计数长度α和保护计数长度β是本模块的重要参数。帧同步状态转移是在校核、失步、同步和保护4个状态中完成,综合考虑其性能参数,选择2、4、16作为α、β、n的数值,在此不作详述。依照相异度最大原则选取A1 A2字节为帧同步码组,即f628H。帧同步状态转移图如图3所示。

串行帧同步码组检测方式,由于其工作在155.52MHz的速度上,同步码组匹配的脉冲宽度只有6.43ns,对于FPGA器件的工艺条件很难达到稳定性能。故而通过8位移位寄存器进行串/并转换,并行方式的脉冲识别宽度为串行方式的8倍。

时钟单元完成clk信号与8分频后的elk8之间的分频转换。STM-1帧时钟为155.52MHz的clk时钟,其它模块则对应8位并行数据的clk8时钟,其时钟频率为19.44MHz。

并行帧同步比较电路模块通过对输入的并行数据的移位,不断与同步码组以字节为单位匹配比较,直至连续2次识别到帧同步码组出现在两帧的同一位置出现,进而选通帧同步使能信号framehead。该信号作为对帧头的识别,为STM-1帧的操作提供了同步保障。

(2)并行解扰模块ITU-T G.707/Y.1322建议给出的SDH串行帧同步扰码器,其伪随机序列发生器的生成多项式为由于扰码器从初始状态到任意时刻的状态都可预先确定,这就为加扰和解扰的并行处理提供了可能。此处的并行扰码/解扰的处理算法通过并行化的处理方式,使用矩阵法对串行的处理算法的状态转移矩阵取八阶即可[5]。

根据ITU-TG.707建议,通过对STM-1帧中段开销SOH区域第一行的所有1行x9N列字节不扰码.进行透明传输,STM-1帧中的其余字节必须扰码后传输。因此,解扰选择模块完成对SOH首行9字节的不选通,对其余字节则选通。

8路并行解扰模块,完成的是并行解扰码的处理过程,以并行状态转移矩阵作为该模块的处理算法,该模块只作解扰处理。

解扰输出模块,利用解扰选择模块的选通和不选通,针对选通字节的使用并行解扰处理后的数据作为输出,不选通字节使用原始数据。不选通的数据在整个过程中都是以无须扰码及解扰的原始状态存在。该模块完成了对并行数据的扰码剥离,输出真实数据。

(3)指针解释&恢复模块本系统只涉及对指针AU-4处理,位于STM-1帧的第4行1~9列,用于指示VC-4的首字节J1在净负荷中的具体位置,以便接收端能够据此正确分离出VC-4。

根据ITU协议,H1、H2字节对应STM-1帧中管理单元指针AU-PTR的第一和第四个字节。读取H1、H2模块,用于读取出存放在H1和H2中的2字节的数值。H1 H2的前四比特位为新数据标志NDF,第三、四比特位是SS比特,后十个比特位存放指针值。

指针解释模块完成对指针值的读取解释。根据H1和H2字节的数值,判断NDF的状态是正常态、无效态、净负荷新数据态,给出指针值、NDF状态使能、CI、AIS使能,若指针有效给出有效使能信号并输出其值。指针FSM模块针对于指针解释模块的输出情况,相应根据指针有限状态机的状态转移图,转换范围在正常状态、指针丢失状态、全1指示状态三者之间.并得到指针值、正负指针调整情况用来从AU-4中准确定位并精确提取出VC-4。

(4)VC-4抽取解复用模块VC-4在STM-1中抽取处理,其主要部分是一个FIFO(又称先入先出存储器),是进行跨时钟域数据传输的重要器件。该模块分为VC-4写模块、VC-4读模块和FIFO(VC-4)三部分。

VC-4写模块,依靠指针值提取出STM-1中的VC-4部分。根据指针解释和恢复模块的输出信号(指针值、指针正调整使能、指针负调整使能),选择正调整和负调整位置相应字节使能,选中所有VC-4的信息字节,写入到FIFO中。

VC-4读模块,根据系统中时钟频率,计算得到读出数据的对应时钟。在无任何调整情况下,STM-1是9行270列的结构中,每行中VC-4占据的是270列中的10~270列,每一行都是如此。因此计算9/270=1/30.式中270代表总的列数,9代表9列的段开销部分.即得到每30次周期中就有1次的段开销处理。使用模30计数器,使用帧同步信号的标识,每30次中只有1次不选通且需扣除。

FIFO(VC-4)采用的是带溢出、临近溢出、半满、临近空白、空白检测状态标记的FIFO,确保系统的运行无误。系统并行数据宽度为8位,故FIFO的数据带宽也应为8。设置堆栈的高度为16字节。溢出、临近溢出、半满、临近空白、空白检测的位数相应为16、14、8、2、0。VC-4写模块的输出VC4Write是FIFO的写入信号,VC-4读模块的输出VC4Read是FIFO的读出信号。VC-4写模块的输出信号J1作为FTFO开始工作的启动信号,鉴于VC-4的首字节为J1,此处的J1用以识别VC-4起始位置。通过对写入数据缓存处理.确保以读出数据速率输出得到VC-4信息。

(5)TU-12支路抽取解复用模块该模块的结构与VC-4抽取解复用模块结构完全类似。TU-12支路抽取解复用模块分为TU-12写模块、TU-12读模块、FI-FO(TU-12)三部分。TU-12Delay模块通过延迟处理,实现数据流与控制信号的对齐。

TU-12写模块依靠J1识别出VC-4信息的到来.其中J1和VC4Write信号作为其输入。由于VC-4中包含63路TU-12支路。若需输出某一路TU-12支路,那么对这63路的分别抽取就要借助其编号TU12Num。TU12Num用于直接选中目标TU-12支路,实现对其的准确抽取。该模块用于把VC-4中的某一TU-12支路的抽取处理,并把得到的目标TU-12送到FIFO(TU-12)模块的写输入端,同时还给出通道BIP-8码B3字节(VC-4在STM-1中传输的误码性能)。

根据STM-1帧结构,对某一固定的TU-12而言,它固定地占有经处理后的VC-4净荷区的四列.且其在VC-4中列号是差值为63的等差序列。

TU-12读模块的设计需要借助频率的计算.根据输人的STM-1的时钟频率,换算得到TU-12的时钟频率。计算4/270=1/67.5=2/135,其原理同上,即采用模135计数器,对应读取计数位置67和134来完成135的二分频。

此处的FIFO(TU-12)同上面的完全一致,系统并行数据宽度为8位,故FIFO数据带宽也应为8。设置堆栈的高度为4字节。溢出、临近溢出、半满、临近空白、空白检测的位数相应为4、3、2、1、0。TU12Write和TUl2Read作为写、读输入,最终输出TU一12支路信号信息净荷,且可以指定输出63路中的任一路TU-12净荷。

总之,上述五大模块中,并行帧同步码组检测模块、指针解释&恢复模块中还分别涉及帧同步状态转移、指针解释状态转移的有限状态机器FSM,对应所有可能状态的转移,因此本设计兼顾了状态连续性以保证都是连续事件。

除了以上五大模块外,还有针对段开销的处理.以B1和B2字节的误码校验作为重点。再生段层BIP-8码的取出及校核、复用段层BIP-24的取出及校核,还分别对应相关模块。复用段开销中的B2字节需要扣除再生段RSOH全部比特。因此还需扣除处理模块。BIP-8(B1)和BIP-24(B2),分别对应解扰前、解扰后的数据进行BIP算法,两者分列并行解扰模块的一前一后。

4编译及仿真结果

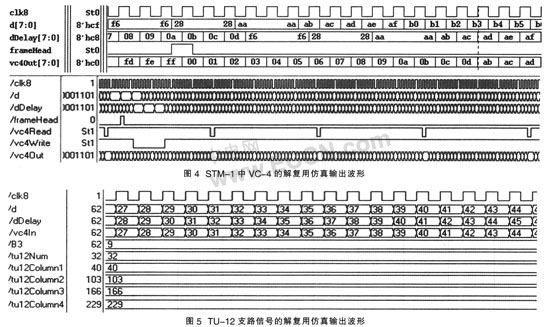

笔者使用可综合的硬件描述语言Verilog HDL,实现了对STM-1/TU-12的解复用系统的设计,在Synop-sys公司VCS平台和.Mentor Graphics公司ModelSim平台上完成了功能仿真,并在Quartus Ⅱ平台上完成动态时序仿真。图4给出了功能仿真图,从解扰后的STM-1信号中解复用出VC-4净荷信号,可以看出处理过程中的适当延迟。

由图5可看出,对于每TU-12支路信号都固定占据每STM-1帧中固定的四列情况,输出的四列信号共同组成一路TU-12,本仿真选择输出的仅为序号为32的TU-12支路情况,若选择其它支路只需改变TUl2Num的输入值即可。

5结束语

本文分析了STM-1/VC-4解复用过程的具体实现方法。提出了整体设计方案并实现了具体的电路设计。本设计方案具体到每模块端口,并通过仿真结果验证了方案的可行性和有效性。设计使用ALTERA公司的Cyclone系列FPGA EP1C6T144C8器件验证通过。

评论