基于平台FPGA实现流量管理和背板设计

平台FPGA结合硬件并行处理、硬件-软件协同子系统和IP内核等技术,为开发下一代业务流量管理系统,实现分组处理、分类和策略、流量管理、背板通信和系统接口等功能提供了一种高性能的灵活平台。

能够产生营收的路由器需要一种技术平台,这种技术平台既要能够提供强大的分组处理能力(即使在最坏的流量情况下),又要能够以较低的成本提供足够的灵活性。FPGA技术的快速发展使得基于FPGA设计完整的路由器和交换刀片成为可能。现在的平台FPGA为实现分组处理、分类和策略、流量管理、背板通信和系统接口等功能提供了一个完整的平台。

网络处理

网络处理器是高度优化的用于处理网络业务流的器件,与传统的ASIC相比,具有产品上市时间快、灵活性高两方面的优点。网络处理器抽取、分类和过滤输入的位流,决定其目标端口,并将数据分组转发到交换矩阵,同时还提供可选的流量管理功能。

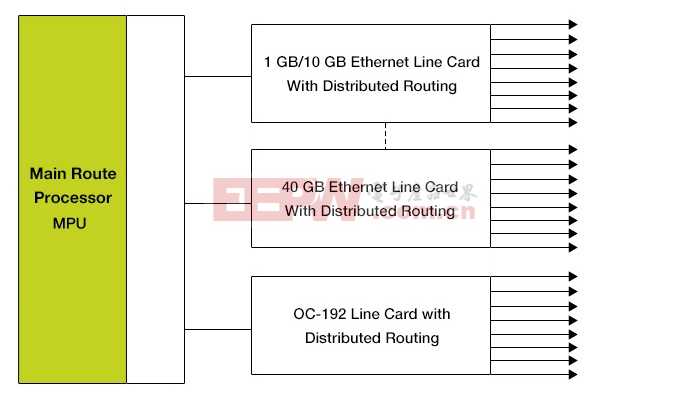

为达到分组处理所需要的性能,一些供应商的解决方法是将功能(图1)分成:

1.分类协处理器:将分组归入某类业务流。

2.策略引擎:保证业务流实际使用的带宽不超过其服务水平协议(SLA)中所分配的带宽。策略通常在服务质量(QoS)网络边缘执行,违规的分组或者被丢弃,或者被打上标记用于后续处理。

3.业务流量管理器:执行相应业务流的服务水平协议(SLA)。通常,来自遵守不同SLA的不同业务流的分组会被重新排序,有时其中有些分组会被丢弃。同一业务流中的分组不会被改变次序。

在网络处理流程中,包括流量整形、队列和调度在内的流量管理功能是带宽需求最密集的关键功能。流量整形帮助管理网络拥塞和应付网络流量的猝发特性。队列和调度引擎决定分组发送出去的时间和顺序。它们通过创建层次化队列来将业务流汇聚为类,将类汇聚为端口。层次的每一级可使用不同的队列算法来确定不同业务流的优先级。

典型情况下,流量管理器是独立的芯片,根据分类器管理的策略集,执行流量整形、排队和调度功能。它们提供了细粒度的QoS控制并负责保证实现服务质量协议。可能会需要一个外部处理器,用于设置或删除业务流配置,此工作不需要逐个分组或信元处理。每个系统在流量管理协议、存储器管理、净荷、接口等方面都有所不同。典型的策略算法包括漏桶(leaky bucket)、令牌桶(token bucket)算法等。拥塞管理算法包括随机早期检测(RED)和加权随机早期检测(WRED)等。调度算法包括优先级队列(PQ)、公平队列(FQ)、加权公平队列(WFQ)和轮询队列(RR)等。

现有的网络处理单元(NPU)器件很少能够满足性能要求,典型的Packet over SONET/SDHOC-48c流量管理器在入口和出口路径需要有独立的流量管理器,或者需要一个全双工(5Gbps)的流量管理器。现有的NPU器件还很少能够支持所有需要的算法。而且,在ASIC方面的投资成本高昂。

平台FPGA实现流量管理和背板设计

流量管理需要高性能、足够的灵活性,并且要支持多种队列和调度算法和协议以及多种存储器类型和接口。平台FPGA器件提供的下述特点为流量管理提供了关键优势:

高速接口

1.多达24个嵌入式千兆位级收发器(MGT)支持高速传输(高达10.3125Gbps),同时抗噪声能力更高、功耗更低并且可减少信号数量并降低电路板复杂性。

2.这些器件还支持17种单端和6种差分电平标准,调度器需要使用的有:

A.用于成帧器和存储器高速接口的HSTL

B.用于成帧器、存储器和ASSP接口的SSTL

C.用于时钟输入/输出的PECL

D.用于刀片或背板通信的LVDS/CML

E.用于实现与CPU芯片组接口的PCI

F.几乎所有其它地方都可使用LVCMOS/LVTTL

3.提供大量封装类型以及大量IO引脚数(最大1200),从而可满足接口所需要的吞吐量要求 。

4.FPGA的每个引脚都支持数字控制阻抗匹配(DCI)技术,可减少成百/上千的片外端接匹配电阻,因此可以简化电路板布局布线工作。因此可以减少电路板的层数,缩短布线长度,从而可获得更高的系统可靠性。

数字时钟管理器(DCM)和时钟分配树

流量管理器需要连接多种外部器件,因此必须面对具有不同频率的多个时钟域。DCM可以补偿由于时钟传输延迟以及电路板布局限制所产生的信号畸变。通常每一外部高速接口使用一个DCM和时钟树。12个DCM提供了相位移动和频率合成能力,特别适合具有多个时钟域和关键时序要求的系统。

DCM支持超过 400MHz的时钟输出,从而可支持领先的总线接口标准,如RapidIO和SPI-4。DCM的数字化特点使其可不受系统温度和电压波动的影响。DCM提供了一个可保证精确50/50占空比的零延迟时钟缓冲。DCM可精确控制一个时钟周期内的相移,精度达到时钟周期的1%,这对建立和保持时间的调整非常关键。DCM支持精确生成24MHz至420MHz范围间的频率。

块RAM(BlockRAM)

超过10Mb嵌入式BlockRAM 对于存储经常访问的对象非常理想,从而可以提高性能。嵌入式存储器适用于多种应用,如:存储器的高速缓冲存储器、存储统计数据和临时数据(Scratch pad)、存储用于发送调度和存储器管理操作的位图、跨越时钟域、以及片内通信的弹性缓冲。

乘法器

流量管理器需要大量的算术运算来完成分组调度计算。调度引擎需要大量的整数和浮点数间的乘法运算(Tsi(t+)=Tsi(t)+Lpkt/rj)。典型的算法需要 100MHz性能的18位乘法运算。平台FPGA器件在单个器件中可提供高达556个运行在300MHz以上的18×18乘法器。乘法器和逻辑资源配合可以设计出定制硬件加速器内核,如加密、校验和计算以及DSP。

大量高性能的可编程逻辑资源(高达1千万门)和布线资源

调度器以极高速度完成大量复杂的运算。而且,操作数存储在寄存器中。由于在每个周期都需要做出调度决策,需要采用深流水线,因此在处理数据风险时,会严重降低处理效率。为了满足这些设计目标,需要使用大量的片上触发器。FPGA提供了超过 300MHz的逻辑性能,并为大量的宽数据通路和链接存储提供了大量内部互连线资源。

PowerPC 处理器、CoreConnect以及工具

现在的平台FPGA嵌入了多达4个300MHz (420 D-MIPS) IBM PowerPC内核来帮助实现诸如统计监控、控制和异常处理等功能。整个解决方案包括:用于访问外设的IBM CoreConnect总线;通过System Generator for PowerPC、GNU编译器和软件调度器工具链、风河VxWorks、MontaVista HardHat Linux等提供的平滑硬件和软件设计环境;同时还提供ChipScope Pro等调试工具。

本文结论

仅仅依赖蛮干的方法并不能满足现代分组交换平台的设计目标。平台FPGA器件的性能水平和特性,为构建能够盈利的路由器和交换机提供了一个强大的平台。平台FPGA结合硬件并行处理、硬件-软件协同子系统和IP内核等技术,为开发下一代业务流量管理系统提供了一种高性能的灵活平台。

评论