基于VHDL的旋转编码器接口电路的实现

旋转编码器是一种高精度的角位置测量传感器,具有分辨率高、响应速度快等特点,被广泛应用在以位置或角度为对象的控制系统中。将编码器安装在电机轴的非负载端跟随转动,其反馈信号传递给控制器,构成对电机的闭环控制[1]。

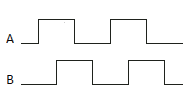

增量式旋转编码器发出两路正交脉冲,即两路(A、B)相位差90°的方波,其相位关系标志电机的转向,当A相超前B相90°时,标志电机正转,如图1所示;当B相超前A相90°时,标志电机反转,如图2所示。编码器旋转一圈,输出脉冲数固定,通过累加A、B两相信号的脉冲数可以计算电机转过的角度。

本文用VHDL语言设计了一种增量式旋转编码器的接口电路,可以配置在CPLD或者FPGA上,实现对编码器输出信号的四倍频、双向可逆计数和与单片机接口的功能。下面介绍各个电路的设计原理和实现源码。

1 四倍频电路设计原理

对于每个确定的编码器,其脉冲周期T对应的角位移固定为q,其量化误差为q/2。若将A和B信号四倍频,则计数脉冲的周期将减小到T/4,量化误差减小为q/8,从而使角位移测量精度提高4倍[2]。

如图1和图2所示,在任意一个周期T内,A、B两路信号各变化了两次,分别产生一次上升沿和一次下降沿,若用Y对A、B两路信号的跳变沿计数,则在一个脉冲周期内,信号Y就会出现4次变化,实现编码器信号的四倍频。

2 转向鉴别电路设计原理

在信号跳变沿时检测另一相信号的电平值可以判断转向[3]。例如,在A相信号上升沿时检测B相信号电平,若B为低电平(如图1),表示电机正转;若B为高电平(如图2),表示电机反转。结合上面所述四倍频原理,计数规则总结如下。

(1)检测到以下状态表示电机正转,加计数:

①A相上升沿,B=0;②A相下降沿,B=1;③B相上升沿,A=1;④B相下降沿,A=0。

(2)检测到以下状态表示电机反转,减计数:

①B相上升沿,A=0;②B相下降沿,A=1;③A相上升沿,B=1;④A相下降沿,B=0。

3 与单片机接口设计原理

编码器的脉冲计数值一般要传送给单片机或其他控制器进行处理,而CPLD的全局时钟的频率高于单片机的时钟频率,为保证CPLD和单片机之间计数值传输的正确性,单片机首先发送信号给CPLD,将计数值锁存后再进行传输。CPLD与单片机接口示意图如图3所示。本设计中CPLD检测到单片机锁存信号的上升沿后将当前计数值锁存[4],然后在单片机位选信号的上升沿和下降沿分时将16 bit计数值的高8位和低8位传送给单片机8 bit I/O端口。

4 实现电路的源代码

本设计利用D触发器的延时作用检测信号跳变沿,D输入端接脉冲信号,则Q输出端是上一个CLK周期的脉冲信号状态。在CLK的上升沿检测Q端输出和D端信号电平值是否一致,不一致表示出现跳变沿。

设A和B是A、B相的源信号,经过D触发器后A、B相信号记为A1、B1,则计数规则表示为:

5 仿真结果

利用ALTERA的开发工具MAX+PlusⅡ,输入VHDL文本文件,目标设备为EPM7128SLC84[5],CLK周期为200 ns,A、B的周期为2 000 ns,编译后仿真波形如图4~图7所示。

图4是编码器正转时的仿真波形,在A相信号的1个周期,两条标记线内,计数值OUTPUT由初始值4增加到8,实现四倍频加计数。

图5是编码器反转时的仿真波形,在A相信号的1个周期内,计数值OUTPUT由初始值15减少到11,实现四倍频减计数。

图6是编码器由正转切换为反转时的仿真波形。如图中标记线所示,B相超前A相后的第一个CLK的上升沿,计数方向立即改变,由加计数变为减计数。

如图7中标记线所示,在锁存信号lock上升沿时16 bit计数值锁存于OUT_lock;位选信号choose上升沿后的第一个CLK上升沿,8 bit计数值OUTPUT8输出OUT_lock的高8位;choose下降沿时OUTPUT8输出OUT_lock的低8位。

由上述仿真波形可以看出,本电路的设计实现了编码器的转向鉴别、四倍频、双向计数以及与单片机通信的功能。

本文设计的编码器接口电路,结构简单、可靠性高,即使在正反转频繁切换的场合也能高精度地工作。本接口电路已应用在单级旋转倒立摆控制系统中,且运行良好。

评论