基于VHDL的HDB3编码器设计

HDB3码具有无直流成分、低频成分少和连续0最多不超过3个等明显的优点,对信号的恢复十分有利,而成为CCITT协会推荐使用的基带传输码型之一。因此,针对HDB3编码器的优化设计具有重要的意义。在本文中,利用VHDL硬件描述语言设计了不同结构的HDB3编码器,在Quart usⅡ中对设计的HDB3码的功能、特性进行了分析。并在EP2C5T144C6中对设计进行了实现。实验结果表明,所设计的HDB3码达到了编码器功能要求。

本文引用地址:https://www.eepw.com.cn/article/201706/349040.htm1 HDB3码编码原理及实现

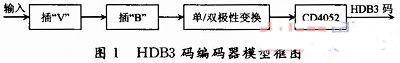

HDB3码是AMI码的改进码型,输入码组中如果出现4位连续位0,就用特定码组来替代,称为三阶高密度双极性码。它克服了AMI码的长0串现象。HDB3编码的主要特点为:基带信号无直流成分,且有很小的低频成分;0串符号最多只有3个具有检错能力,如果接收端信号1电平的交替规律被破坏,认为出现了差错;利于定时信息的提取;不受信源统计特性的影响。因此,HD83编码被广泛运用于脉冲编码调制的线路传输码型。在对代码编码的时候,先不对输入的代码进行极性变换,而是先检测是否插入“V”,再检测插“B”,这样做就使得输入进来的信号和插“V”、插“B”功能电路中处理的信号都是单极性信号,且需要的寄存器的个数很少。当然,在检测插入“V”较为简单,只需设计一个计数器记下连续0的个数,出现4个连0时即可将第4个0用二元码表示。而在插“B”时,首先把信号寄存在寄存器里,同时设计一个计数器计下两个“V”符号之间0的个数,再由一个判偶电路来给寄存器发送是否插“B”的判决信号,决定是否插入“B”,从而实现插“B”功能。至此,代码全部都由双相码表示。最后,极性变换可以将原来的“1”码和插入的“B”合在一起做极性变换,将插入的“V”单独做极性变换,这样就完成了HDB3码的编码。它的编码模型如图1所示。

要识别编码中的“1”,“V”和“B”。在编码中最终的表现形式还是逻辑电平“1”。解决的方法是利用双相码,将其用二进制表示。双相码的编码规则是:对每个二进制代码分别利用两个具有两个不相同相位的二进制码去取代。如:用10表示1,用00表示0等。

2 基于VHDL硬件描述语言的HDB3码编码器建模及程序设计

在设计中,根据HDB3编码器的结构模型和VHDL语言程序设计的特点,采用进程语句和元件例化语句实现HDB3码编码器的设计。其中,在采用进程语句实现的设计中,主要是一个结构体中包括4个进程,分别是序列发生器、插入“V”、插入“B”和极性变换。而在该方法中,又分别使用了二进制三位码元和二进制二位码元来对HDB3码进行编码。在元件例化语句中,主要分为5个文件,分别是序列发生器、插入“V”、插入“B”、极性变换以及顶层文件,各进程之间通过信号传递编码值,在编码中也将采用2位二进制来编码。

2.1 四进程三位编码的HDB3编码器程序设计

在该方法中,将用VHDL语言的四进程语句描述方式来实现HDB3码编码器,分为4个进程。首先设计一个序列发生器,产生输入序列,作为HDB3码编码器的输入。利用3位二进制代码对插入的V,B进行编码,用000表示0码、010表示-1、110表示1、011表示-V,111表示+V、101表示+B、001表示-B。在插V和插B结束后,输出代码均变为用3位二进制编码的序列。然后要将3位二进制代码进行极性变换,输出2位的二进制编码序列,分别表示+1,-1,0。

2.1.1 输入序列发生器的设计与实现

首先,设计一个计数器,用来对产生序列的位数进行控制。设计中,利用5位计数器“cnt”,其可以控制产生47位的输入序列用以供后续的编码器的仿真分析使用,产生的序列为:100001000011000000001。要求,序列发生器和HDB3码编码器均在同步时钟脉冲上升沿的作用下工作,保证产生一个代码就能迅速的输入编码器进行编码。

2.1.2 对输入序列做插“V”的设计与实现

在插“V”符号时,首先要判断输入的信号是1码还是0码,若输入的是0码,则接着判断输入的是第几个0码,如果是第4个0码,则把这个0码变换成V码,否则,保持原码输出。在程序中将用两个信号flag0和flag1来标识V和非0码的极性,并且flag0和flag1的初始值均为0。再设计一个计数器记录下连0的个数,用以判断是否插入“V”。若flag0和flag1均为0,则说明前-“V”或“非0码”极性为负,此时的“非0码”或“V”极性为正,用110代替。

对于输入序列的检测,如果第一个4连0之前有“1”码,则第一个“1”码的极性就由flag0的初值来确定,后边的“1”码也随之确定,第一个V的极性也由前面的“-1”码的极性确定,V码的极性是自行交替,则后面的V码极性也随之确定;如果输入的序列第一个4连0前面没有“1”码,则第一个V码的极性由它的标识信号firstv的初始值(程序中赋初值为0)确定。后边的“1”码和“V”码的极性均由第一个V的极性确定。最后,插“V”后的输出均为3位码。

2.1.3 插入“B”的设计与实现

在该部分将借助4位的移位寄存器来实现,使用元件例化语句D触发器组成4位移位寄存器。根据HDB3码的编码原理,首先将插“V”后的代码放入寄存器里,在同步时钟的作用下同时进行是否补“B”的判断,等码元从寄存器出来的时候,若需要补“B”,则把+B或-B的标识码直接赋值给移位寄存器的第4位;若不需要补“B”,则直接把移位寄存器的第3位送第4位照原码输出。

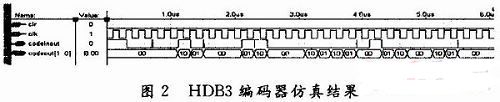

在设计中,用10标识+1,用01标识-1,用00标识0。其中codeinout是用来观察序列发生器产生的二进制码序列,codeout为HDB3码的编码输出。波形仿真结果如图2所示。

从图2中可见,输出的编码序列和编码规则一致,说明设计正确。

2.2 HDB3极性变换

在极性变换中,将使用四选一模拟开关实现+1,0,-1的波形输出。实现真正意义的HDB3码的输出,这里选用的是数字芯片CD4052来实现。

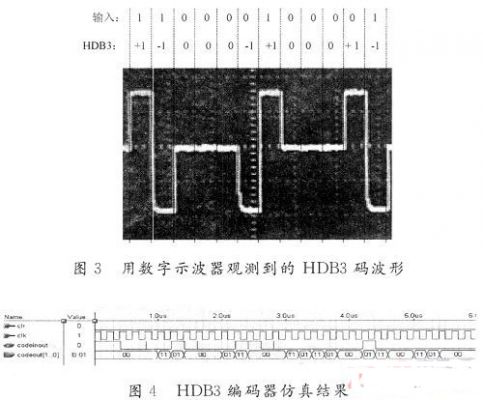

在单双极性变换设计与实现部分,要实现将3位的编码转换为2位的编码,也就是将前面的+1,-1,+V,-V,+B,-B,0转换成用两位来标识,这样才能通过CD4052的两个输入端进行不同的组合,从而选通不同的通道,实现HDB3码的+1,-1,0三种电平的输出。而转换的方法和编码时确定的极性是一致的,分别用10,01,00来标识+1,-1,0。在数字示波器下观测到的波形如图3所示。

2.3 结构化HDB3码编码器设计

在该设计中,将使用元件例化语句来实现HDB3码编码器。底层文件主要分为序列发生器、插“V”模块、插“B”模块、单双极性变换模块,加上顶层文件共5个模块。在该设计中,用11标识+1,01标识-1,用00标识0。其中codeinout是用来观察序列发生器产生的二进制代码序列,做为HDB3码编码器的输入序列,codeout为HDB3码的编码输出。该设计运用VHDL硬件描述语言的元件例化语句来实现HDB3码编码器的设计,共一个顶层文件和4个底层文件。在编码中,选用2位二进制对HDB3码编码的插“V”和插“B”以及输出进行编码,且用的均为非归零码来表示。对元件例化语句二位编码的设计进行波形仿真结果如图4所示。

从图4中可见,输出的编码序列和编码规则一致,说明设计正确。

3 HDB3码编码在FPGA中实现的特性分析

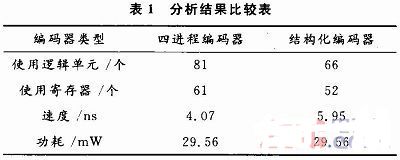

选用cycloneⅡ系列EP2C5T144C6器件,利用QuartusⅡ7.2对两种不同设计的HDB3编码器进行了分析。分析的主要内容包括:逻辑单元的占用、寄存器的占用、工作速度及功耗等的比较。仿真之后,主要选择了两组结果进行比较。分析结果如表1所示。从仿真结果可以看出,在结构化设计中,编码器总逻辑元件、专用寄存器使用与四进程设计相比各减少了18.5%,14.8%,表明结构化设计有利于减少器件资源的使用。

4 结语

根据实验和系统分析的结果,在FPGA中,利用VHDL语言设计HDB3编码器是可行的。尤其是结合VHDL语言程序设计的特点,利用不同的设计方式,可实现对HDB3编码器的优化设计。通过比较,在结构化设计中,编码器总逻辑元件、专用寄存器使用与四进程设计相比各减少了18.5%,14.8%。因此,结构化设计有利于减少器件资源的使用。

评论