双模超高频读写器的同步和解码模块设计和实现

引言

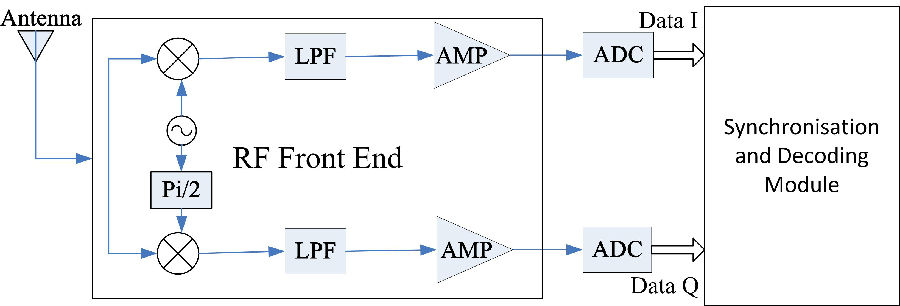

本文引用地址:https://www.eepw.com.cn/article/201703/345029.htmRFID(Radio Frequency Identification)技术是指以识别和数据交换为目的,利用电磁波进行非接触式双向通信的自动识别技术。利用这种技术可以实现所有物理对象的追踪和管理,在物品管理和物流跟踪等方面备受关注和应用。一个典型的读写器系统主要由三部分组成:读写器,标签和天线。本文所介绍的同步和解码模块属于读写器接收链路的关键模块,整个读写器接收链路如图1所示。

读写器上的天线接收到标签的返回信号,经过带通滤波后,与混频器(Mixer)混频,用低通滤波器滤掉高频分量,经过运放处理后的两路信号给ADC (Analog to Digtal Converter)转换为两路I、Q数字基带信号,数字基带处理器接收两路信号。带有同步和解码功能的处理器,用来进行两路信号的判决、同步和解码,从而恢复出原始的比特符号,使得读写器能够进行下一步的通信。

图1 UHF RFID读写器接收链路

可见数字同步和解码模块是整个接收链路的重点和难点。前人对这一部分也做了很大的研究。这里,我们设计了一个新颖的同步和解码模块。为了满足我国RFID读写器的发展,我们的同步和解码模块同时支持ISO18000-6C和GB标准,支持两种标准下的各种返回速率。同步模块以面积和低功耗为设计原则,在设计实现中,(1)采用过零点同步;(2)设计中两种模式共用一条接收链路,通过外部接口,配置寄存器,选择标准工作模式,同步模块能够快速判断出标签的理想返回速率并且进行返回速率的计算,各种速率共用一个判决机制,大大减小了同步模块的面积;(3)解码模块增加再生信号相位检测和同步时钟相位检测机制,提高了解码的抗干扰能力,降低了误码率,并且由同步判决模块产生同步时钟,经过相位检测机制后得到的解码时钟,使得该时钟和待解码信号恰好相差一个采样时钟的相位差,这进一步降低误码率,增加解码的正确性。

本次设计的验证和实现,采用FPGA (Field Progammable Gate Array)和读写器射频板共同搭建一套读写器系统测试平台,实测结果表明我们的设计能够容忍+/-22%的频偏,能够解调各种受射频接收机、天线、噪声、直流偏置和距离等因素影响的标签返回信号。

1 同步和解码模块分析与设计

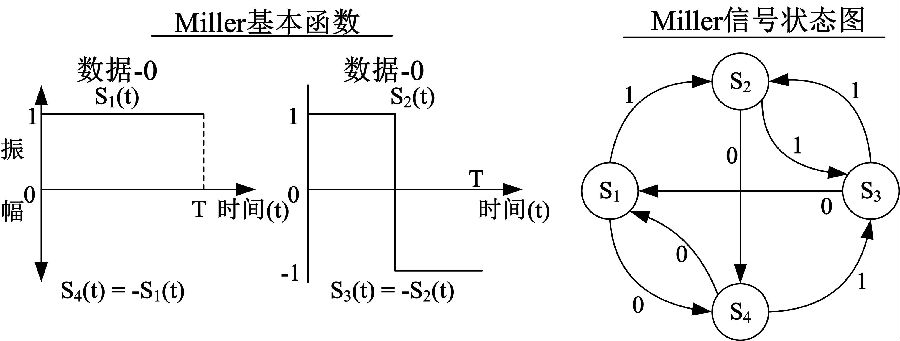

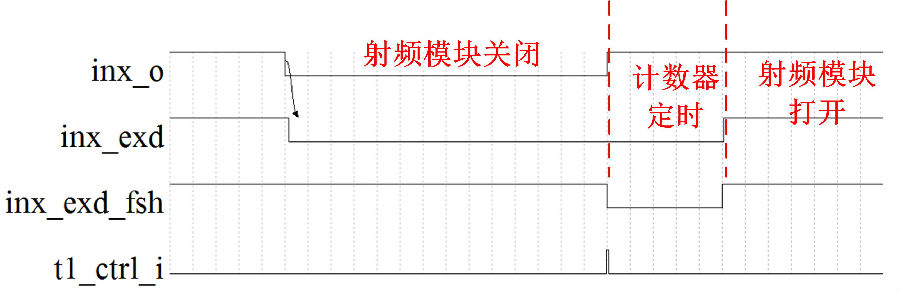

根据ISO18000-6C和GB两种标准,标签接收读写器发送的载波能量,通过后向散射给读写器信号,返回信号采用FM0或者Miller (2、4、8)编码,本文的研究以Miller2来说明,图2展示了Miller基本函数和信号状态图,图3展示了Miller导引头,可通过设置‘Trext’位的值来选择导引头类型。FM0与Miller基本类似,这里不再赘述。

图2 Miller基本函数和信号状态图

图3 Miller导引头

1.1 数字基带接收信号的特征

通过上述的论述,我们了解到了RFID系统返回信号的特殊性,首先由于无源标签没有一个参考时钟来校准返回的数据速率,使得基带接收到的信号速率偏差较大,最大可达+/-22%的频偏,增加了同步和频率估计的难度;接着从上述讨论的Miller函数的基本特征可知,返回信号的导引头过短,过于理想化,难以达到同步;最后数字接收信号相位和功率受射频接收机、天线、多路径衰减信道、距离和直流偏置等因素的影响,使得SNR (Signal To Noise Ratio)较低。ADC转化之前的接收信号可由公式(1)来进行描述:

其中 s(t),r(t) , ndc(t)和n(t)分别为读写器发射信号,接收信号,直流偏置噪声和高斯白噪声, 表示射频载波频率, 表示读写器与标签之间的距离, 是标签返回信号的初始相位。

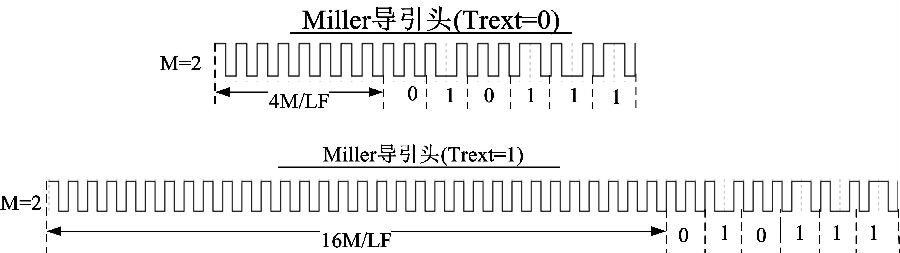

为了克服上述RFID接收信号的这些缺点,设计思路,采用在接收链路上加了窗函数控制功能,即用一位inx_o来控制射频接收模块的开启和关闭,在接收时开启射频接收,发送时关闭射频接收,来缓解直流偏置噪声的影响,提高SNR。其时序如图4所示,这里不属于本文研究重点,不做详细说明。根据接收信号的特征,综合资源和功耗的考虑,同步器采用过零检测型结构,增加累加器判决机制,多种返回速率计算模块复用,并且由于速率偏差严重,解码时钟由同步器判决提供,解码器带有再生信号相位检测和同步时钟相位检测机制,具体的分析设计和实现以下讨论。

图4 窗函数控制时序图

1.2 同步模块分析与设计

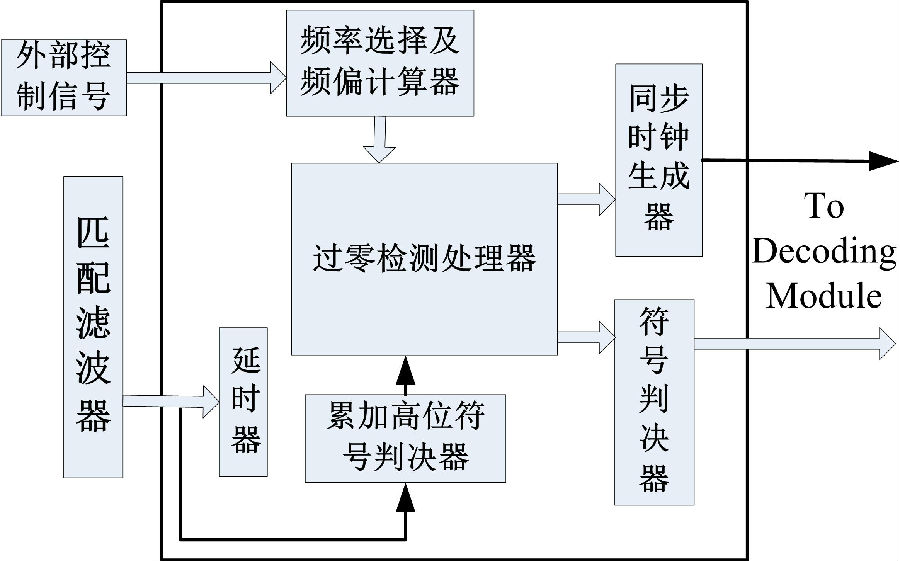

同步模块采用过零检测型结构,其整个算法实现如图5所示,该结构主要由过零检测处理器、频率选择及频偏计算器、累加高位符号判决器、同步时钟生成器和符号判决器组成。读写器天线接收的射频信号经过匹配滤波器后,经ADC量化成数字基带信号供同步模块提取接收频率、相位和符号信号。频率选择、协议标准及接收结束标志等由外部模块及外部接口提供。

图5 同步模块结构示意图

过零检测型结构相对于相关型和数字PLL(Phase Locked Loop)型结构,其结构简单,所占资源小,不过抗干扰性差,噪声及干扰会严重恶化过零点边沿的检测的性能,且其同步性能与过采样率密切相关。所以我们将量化后的数字信号进行累加运算,提取它的高位符号给过零检测处理器,考虑到返回信号最大速率40kHz及+/-22%的频偏,可得累加器位宽计算公式如下(2):

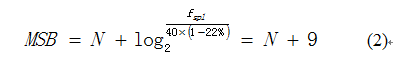

MSB为累加器的位宽,N为量化器位宽, fsp1为采样时钟。

综合考虑了同步性能和功耗的影响,采样时钟设计为10 MHz,采用6bit量化器,所以MSB为15,即累加器位宽为15。符号的判别由累加器的最高比特提供,每次过零标志置一时,重新累加,误差不累积,大大地提高了SNR及抗干扰能力。

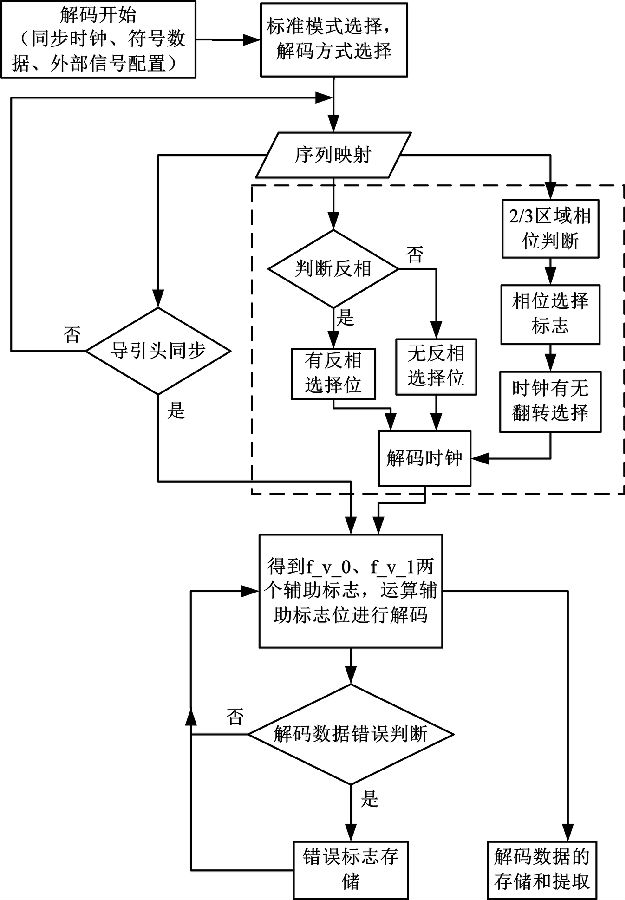

以Miller2解码,640 kHz、320 kHz和80 kHz为例来说明此同步模块对频偏的处理。该同步模块事先存储好在采样频率下的每种返回速率的理想计数值,并且由此计算出该频率偏移下的频率计数值,能够正确判决出接收信号的最大+/-22%的频偏。下表1给出了640 kHz、320 kHz和80 kHz下的计数值。Miller解码下,根据计数器cnt_ts与计数阈值1和计数阈值2的比较,来进行符号的判决。

2.3 解码模块分析与实现

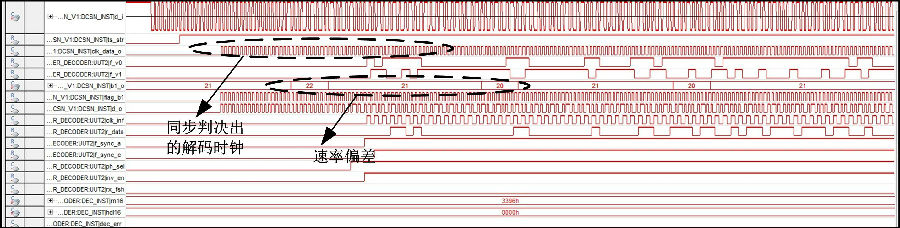

解码模块的解码时钟由同步模块生成的同步时钟处理得到,符号数据由同步模块提供,同步器生成的同步时钟及符号数据信号均采用边沿信号ts_bgn这同一个起始点,并且同步时钟的占空比和周期时时根据量化后的数字基带信号的采样个数进行调节,使得同步时钟和符号数据之间最多一个采样时钟周期的相位差,大大提高解码的正确性。下文会给出它的验证波形。

该解码模块也同时支持ISO18000-6C和GB两种标准模式,支持FM0和Miller解码,这里以和Miller2解码和ISO18000-6C模式来说明。设计中,保证解码模块和同步模块在同一个时钟域下工作,这里采用同一个采样时钟。

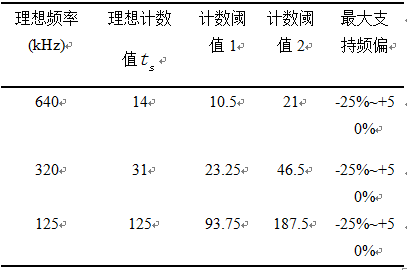

整个解码模块的工作流程图如图6所示。从同步模块产生的符号数据与存储的映射序列24'b1010_1001_0101_0110_1001_0110进行比特级的比对,若一一对应,则表示导引头同步,f_sync_a置位,反相标志位inv_en清零,若比对完全相反,表示导引头同步上,f_sync_a置位,inv_en置位,从而达到再生符号信号的相位检测,能够解码返回的正相和反相信号。与此同时,在序列存储区

的2/3区域进行判断,得到一个采样时钟周期的信号脉冲,在该信号脉冲的下降沿与同步时钟进行与运算,判断符号信号与同步时钟是否有(2k+1)p的相位偏移,若有则调节时钟,若无则保持原来的同步模块的同步时钟,从而达到同步时钟的相位检测,此机制能够大大地缓解数字接收信号相位和功率受射频接收机、天线、多路径衰减信道、距离等因素的影响造成的解码的错误,减小了解码的误码率。之后经过一组时钟分频和选择链路,从而得到Miller解码时钟。之后开始数据的解码,解码的错误判断以及解码数据的存储和提取。该模块,数据解码的实现主要是根据它的‘data_0’和‘data_1’数据的特点以及数据与Miller解码时钟的相位关系。解码模块接收同步模块的再生符号信号symbol_i和同步时钟clk_data_buff,在clk_data_buff时钟下,将symbol_i下降沿采样到buff_ofst,在解码时钟clk_inf上升沿对symbol_i和buff_ofst的异或信号进行处理,得到f_v_0信号,该信号用来判断Miller (M=2)每一位符号数据的开始相位是否出现跳变,若有则f_v_0信号为高电平,否则为低电平;在解码时钟clk_inf下降沿对symbol_i和buff_ofst的异或信号进行处理,得到f_v_1信号,该信号用来判断Miller (M=2)每一位符号数据的中间相位是否出现跳变,若有则f_v_1信号为低电平,否则为高电平。在clk_inf时钟的上升沿判断下,通过f_v_0 跟f_v_1两个标志信号,便可得出解码数据r_data。下文会给出它的仿真波形。

2仿真与验证

2.1 ModleSim仿真结果

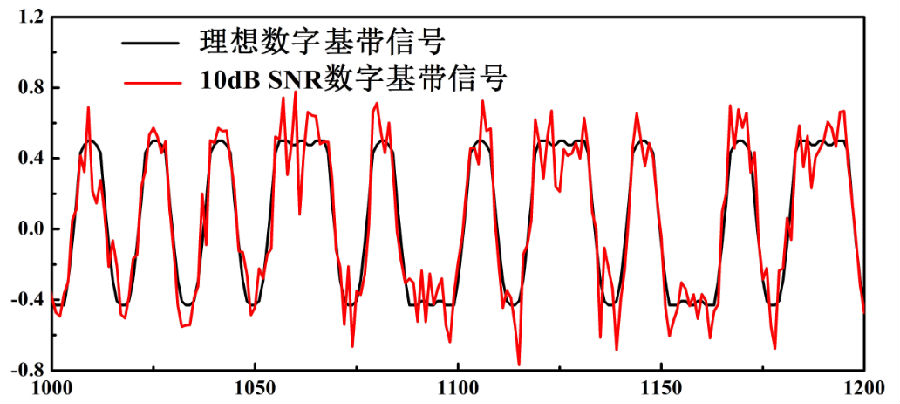

对于设计的同步和解码模块,采用ModleSim进行功能仿真。先用Matlab建模,模拟产生ADC量化之后的6比特数字基带信号,如图7所示,蓝色实线表示10dB SNR的数字基带信号,黑色虚线表示理想的数字基带信号。从而将Matlab产生的信号作为输入信号源,与ModleSim进行联合仿真。

图6 解码模块流程图

图7 Matlab建模产生的10 dB SNR的数字基带信号和理想数字基带信号

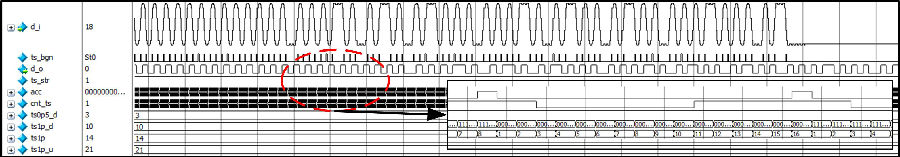

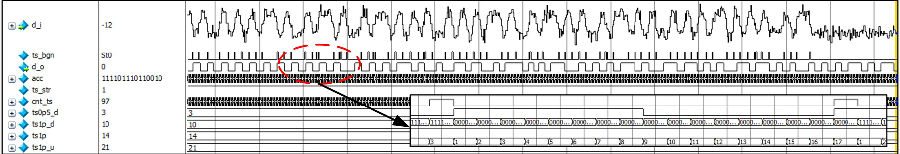

在仿真建立中,先用Matlab产生的理想数字基带信号作为提供给同步模块的6比特信号源,仿真波形如图8所示,当有6比特的信号进来时,首先进行标准的返回速率的选择,接着是频偏计数的计算,这里是640 kHz的返回速率,得到理想计数为14,计数阈值1 ts1p_d为10,计数阈值2 ts1p_u为21,与表1所示的设计值一致,对于理想的数字信号每个返回速率的周期过零点数最多不超过两个,即ts_bgn脉冲信号在一个返回速率周期中不超过两个脉冲信号,cnt_ts是两个ts_bgn脉冲之间的采样计数,acc是累加器的累加和,可通过cnt_ts和acc的最高比特来共同判断判决出来的符号,并提供给内部FIFO进行存储。10 dB SNR的数字基带信号同步模块仿真波形如图9所示。

图8 理想数字基带同步模块仿真波形

图9 10 dB SNR数字基带同步模块仿真波形

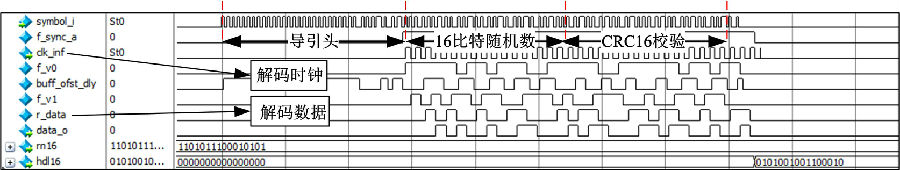

对于判决输出的符号信号d_o,供给解码模块进行解码,ModleSim仿真出来的解码波形如图10所示,与协议标准符合,判决出来的符号波形由导引头、16比特随机数和CRC16校验组成,当与序列映射一一对应时,f_sync_a置1,表示导引头同步上,开始数据的解码,clk_inf为最终经过时钟检测和信号检测之后的解码时钟。在该时钟下,对f_v0和f_v1异或之后的信号进行上升沿采样,则可得出解码后的数据,经过比对可得出符号信号的16比特随机数与data_o的数据一一对用,hdl16和rn16为提取出的解码数据。

图10 解码模块仿真波形

2.2 验证平台验证结果

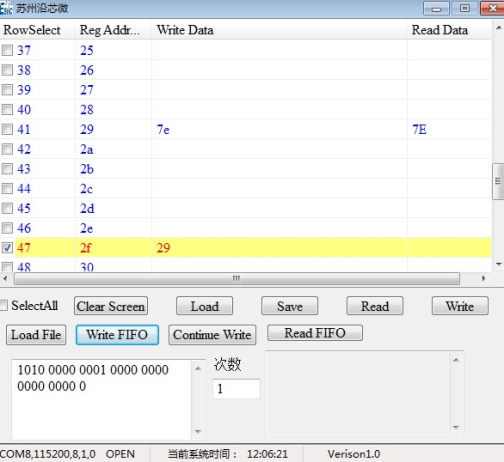

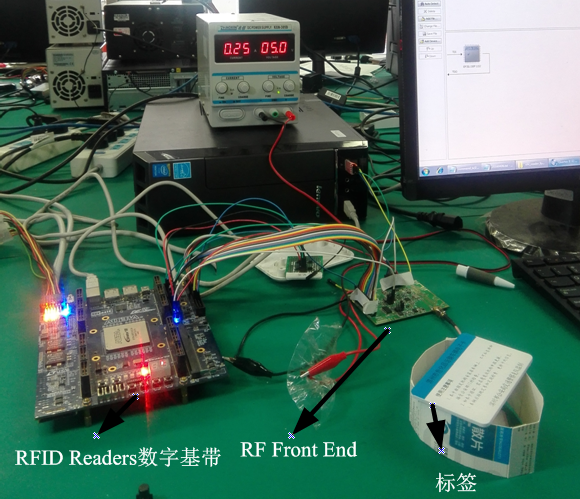

最终,基于Altera FPGA “Stratix III EP3SL150F1152C2”与读写器射频板和标签共同搭建测试平台,用于实测我们设计的同步和解码模块。验证平台如图11所示。图12是上位机软测试工具。

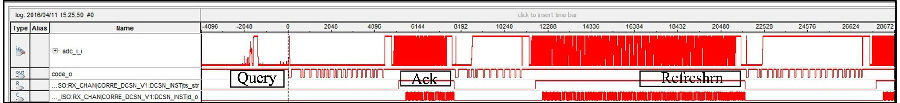

基于FPGA的实测,我们可以通过Quartus II的Signal tap工具来抓取实际电路的数字信号。通过上位机软件和接口电路,可以控制读写器的发送命令,来测试整个读写器系统的功能,这里主要用来验证我们的同步和解码模块。发送select和query命令后,Signal tap抓取的波形图如图13所示。图14是抓取的同步模块和解码模块的部分信号波形图,可以看出标签的返回速率的偏差以及解码时钟的生成的相关信号。

图11 上位机软件测试工具

图12 验证平台

图13 发送select和query命令后的波形

图14 同步和解码模块部分波形图

3结论

本文提出了一种新颖的,同时支持ISO18000-6C和GB两种标准的同步和解码模块的设计和实现。根据低功耗和面积资源的原则,同步模块采用过零检测型码元同步器,增加一级累加器结构用于过零检测,提高了判决的正确性。解码模块增加再生信号相位检测和同步时钟相位检测机制,大大提高了解码的抗干扰能力,降低了误码率。通过仿真和验证结果分析,该结构可正确解调+/-22%的频偏,能够在10 dB SNR下正确地同步和解码。最终生成的RTL级数字电路可作为IP核使用,用于FPGA的调用或者通过DC

综合,作为ASIC的数字电路,这对于UHF RFID读写器全数字集成具有一定的借鉴意义。

作者:

许玉淇1 肖永光2 唐明华2 成传品3

1湘潭大学 物理与光电工程学院(湖南 湘潭 411105)

2湘潭大学 材料科学与工程学院(湖南 湘潭 411105)

3湖南工程学院 理学院(湖南 湘潭 411104)

基金项目:国家自然科学基金项目(编号:51472210, 61274107, 61404113)

评论