使用逻辑分析仪快速发现数字系统的问题

逻辑分析仪中的同步和异步捕获比较

在讨论具体的测量实例之前,我们首先来探讨一下同步和异步捕获的差别,以及各自的优点和局限性。

同步(状态模式)捕获是指当出现一个相关的有效时钟信号时,例如在系统时钟线路上出现上升沿,逻辑分析仪中的测量系统会确定数字并行总线或控制线路的逻辑值。此类测量最主要的目的是确定系统的基本功能是否正常。

相比之下,异步(计时模式)捕获是指测量系统采用与被测系统“异步”的方式对总线或单独数字线路的值进行采样。测量时钟信号由逻辑分析仪而非目标系统生成。采样速度一般比目标系统的时钟速率快,理想情况下,采样速率是系统时钟速率的4倍~10倍,这使您可以查看相关信号的“计时”特征。

通过同步捕获进行功能验证

当数字设计的物理原型启动后,许多设计人员首先想要做的便是通过各种同步状态模式测量,确定系统内部的功能是否正常。如果发现异常,他们将会使用异步计时模式测量来查看是否可以找出问题所在。

假设有一个简单的8位计数器电路,在这个特殊的实例中,设计将会生成计数器数据,这些数据会在时钟上升沿之前变得有效和稳定。

通过同步捕获初步了解计数器电路

通过将逻辑分析仪的8条数据输入线路连接到电路的8条数据比特输出线路,可对计数器是否正常工作进行初步的测试。

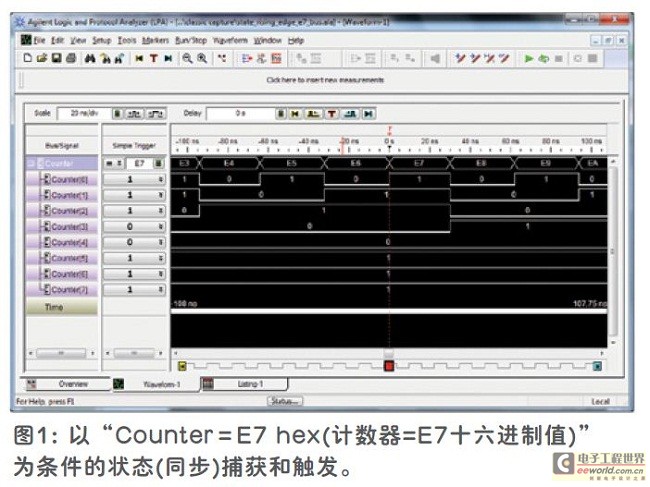

将逻辑分析仪置于“State(状态)”或同步捕获模式,并将计时设置为在时钟信号的上升沿捕获数据。通过“Waveform(波形)”窗口可以非常轻松地设置简单的触发。如图1所示,可以在总线名称“Counter(计数器)”旁边输入十六进制值E7,定义简单的触发事件。

当按下“Run(运行)”后,Waveform视图中会显示一个十六进制值序列。如图1所示,它们看上去进行了适当的计数,要想快速获得此数据的更完整视图,可以采用另一种方法“ChartMode(图表模式)”。图2为图表模式视图,但是看到的不是预期的纯净斜波。

评论