基于高吞吐率WLR测试的 ACS集成测试系统

引言

本文引用地址:https://www.eepw.com.cn/article/201702/338583.htm随着器件继续小型化,半导体器件可 靠性测试以及器件寿命预测面临极大挑战。由于新材料和新工艺的复杂性增大,器件 失效的随机性也在增加。1 这需要产生更 大的统计样本测试数据。虽然传统的应力 -开关-测量可靠性测试技术能实现庞大数 量的器件测试,但这种方法可能存在问题。使用TDDB,工程师需要监测软击穿和渐进 式击穿。采用NBTI,必须最小化器件弛豫并以极快的速度完成测量。在测试单个器 件的层面上,某些问题还是可控的,但在 实际时间段内顺序测试单个器件不能提供 大量的统计样本数据。

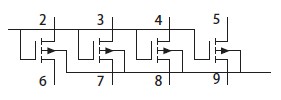

图1. 采用SMU-per-pin(每管脚SMU)架构的ACS集成 测试系统举例

此应用笔记讨论了如何克服ACS集成 测试系统和SMU(源-测量单元)-per-pin 配置条件下的可靠性测试挑战。使用吉时 利2600系列源表和自动特性分析套件(ACS) 软件,可以针对越来越复杂的测试(例如 TDDB、NBTI和HCI)实现中等规模系统(20 ~40引脚)。由于ACS中含有全自动探测器 控制和自动测试序列功能,因而可以实现 高吞吐量测试。去除开关后,SMU-per-pin 配置在提供系统灵活性和易用性方面还起到 了重要作用。此外,ACS提供了集成测试流 环境、方便的点-击操作,而且包含常规可 靠性测试,例如: • TDDB、Vramp、JRamp(JEDEC标准测试) • HCI(NBTI)、即时NBTI、NBTI快速SMU • EM、等温EM(JEDEC标准测试) 用户可以利用标准库的模块作为模板, 用ACS快速开发自用测试。图2示出了用ACS 进行TDDB测试的例子。

SMU-Per-Pin WLR测试 SMU-per-pin的理念非常简单——从系 统架构中去掉开关矩阵并用独立SMU代替漏 掉的引脚连接。用创新的TSP-LinkTM 将几 台2600系列仪器连起来像一台仪器那样工 作。为了更好地理解SMU-per-pin架构的优 点,请考虑下面两种情况。 • 测试共用引脚结构 • 同时测试几个器件的可靠性 共用衬垫/引脚测试结构 考虑图3的共用引脚器件。4个MOSFET 共用栅极和衬底引脚连接,而且每个MOSFET 的漏极和源极引脚单独连接。共用SMU配置 可以使用4台SMU和一个开关矩阵顺序测试器件。将结构划分为几个较小的设备后,测试 时间因开关而延长了。此外,劣化恢复出现 在大多数可靠性测试的开关过程中,从而使 测量的劣化和接下来的寿命预测出现变化。在此情况下的共用SMU架构存在另一个 缺点。在测量一个器件时,剩余器件受栅极 电压变化的影响。这会给栅极应力带来不应有的变化。SMU-per-pin架构具有消除开关 延时、实现并行测试的显著优点,这无需驱 动每个结构的栅极。

图4示出了多器件TDDB测试结构的共用 SMU和SMU-per-pin配置。在开关(共用SMU) 情况下,SMU1提供连续应力至测试序列的全 部结构,SMU2顺序测量每个器件。在顺序分 析结构的过程中,开关延时和有限的测量速 度合在一起会限制每个结构的测量速度。因 此,必须分析这些延时并折合至寿命分析以保证准确推测寿命。而且,如果一个结构遭 受灾难性的故障,本组的其它结构将遭受电 压瞬变、暂时失去应力条件并可能使测量结 果不准确。SMU-per-pin架构不受开关延时 和结构不良连接的影响,但更重要的是测量 速度非常快,这对于采集高速渐进击穿现象 而言至关重要。

评论