示波器梦想之方案选择

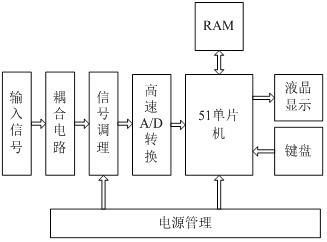

图1方案一系统框图

这种方案结构较为简洁,但很明显,A/D的最高采样速度达1MHz,由普通单片机直接处理这样速率的数据难以胜任,采用高档单片机甚至采用DSP芯片,将大大增加开发的难度。而且目前常用的外接RAM芯片时钟周期一般为40MHz~50MHz,难以达到高速数据存储的要求。

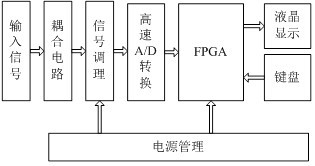

方案二:用FPGA可编程逻辑器件作为控制及数据处理的核心,利用FPGA的层次化存储器系统结构,使用FPGA内部集成的基本逻辑功能块配置成双端口同步RAM对采集信号进行存储,完成设计指标。其系统框图如图2。

图2方案二系统框图

由于FPGA可在线编程,因此大大加快了开发速度。电路中的大部分逻辑控制功能都由单片FPGA完成,多个功能模块如采样频率控制模块、数据存储模块都集中在单个芯片上,大大简化了外围硬件电路设计,增加了系统的稳定性和可靠性。FPGA的高速性能比其他控制芯片更适合于高速数据采集和处理,而且使用FPGA内部存储模块完成输入信号的量化存储,在存储速度上有着外接RAM无法比拟的优势。

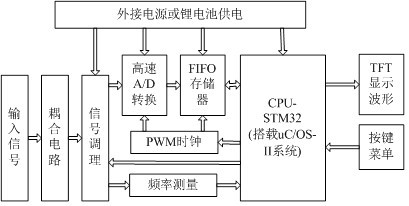

方案三:以Cortex-M3内核的STM32为主控制器的方案如下:

微处理器采用意法半导体的32位处理器STM32F103VET6,其内部是ARM公司Cortex-M3内核,工作主频最高可达72MHz,再在其上面移植开源的实时操作系统uC/OS-II系统,确保系统的实时性和稳定性。由于高速A/D转换器的速度太快,STM32处理数据的速度跟不上,所以在中间加入FIFO高速缓存器。利用STM32内部自带的FSMC(灵活的静态存储器控制器)来控制TFT液晶屏刷新波形,可实现更高频率的信号的波形刷新和显示。此为,利用STM32的高级定时器可输出高达12MHz的时钟,可以作为高速A/D转换器的采样时钟和FIFO存储器的控制时钟,从而避免了一大堆由有源晶振和数字芯片组成的时钟电路。

方案比较:

方案一虽然简单,但是51单片机处理能力有限,无法实现数字示波器的基本指标;

方案二采用FPGA虽然能深入开发数字示波器,然而,其成本偏高,即使加入SOPC软核,其软件压力也很大(后期为了提高性能可以用FPGA来做的)。

方案三是能够实现嵌入式数字示波器基本指标的良好方案,器件成本不高,实时操作系统uC/OS-II 简化编程,提供系统实时性和稳定性。

因此,本设计最终选择方案三开展设计。

评论