基于FPGA实现感性元件电阻测试

引言:

本文引用地址:https://www.eepw.com.cn/article/201701/337463.htm近期给汽车电子某厂商做了一套点火线圈测试系统,有一部分是关于感性线圈电阻测试,具体要求如下:初级电阻 620 mΩ +-50mΩ、次级电阻 9.5 kΩ +-0.9 kΩ、导线电阻 150 mΩ +-50 mΩ。

一、挑战:

初级线圈电阻较小(mΩ级),测量过程中还要考虑导线电阻影响;而次级电阻大(k Ω级),用DMM数字万用表进行测试是不错的方案,但是由于测试设备是放在生产线上,对体积、功耗和可靠性要求很高,NI CompactRIO平台是非常好的选择,但是NI CompactRIO电阻测试模块量程大,不适合小电阻测试。并且由于被测件是感性线圈,通过恒电流激励4线制测电阻方式,由于恒电流激励稳定性问题,会 使得感性线圈产生感应电动势,对小电阻测试带来考验。

二、方案:

选用NI 9265电流输出模块作为电阻测试激励,通过4线制来测量电压方式来进行电阻测试。为了减小电流激励不稳定性导致感应电动势产生,带来测量误差的影响,通过在FPGA用高频(10k)采样,然后降采样到低频(50-100Hz)模式,滤除感应线圈电动势的影响。

三、具体实施:

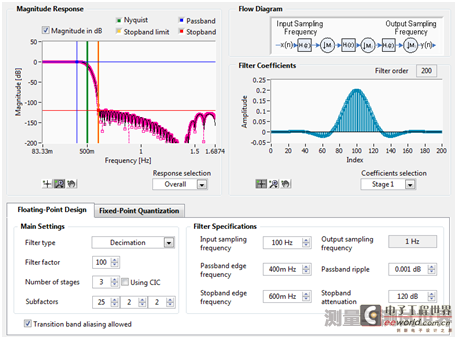

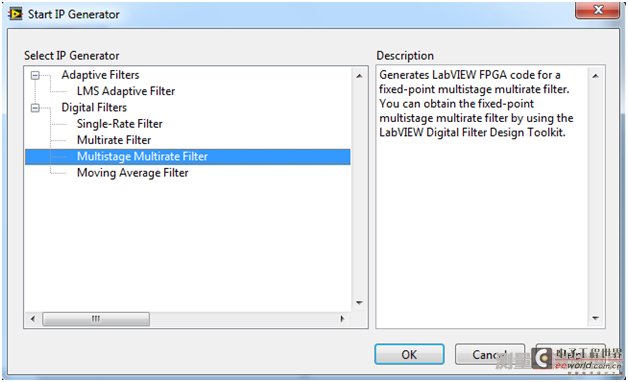

1、 构造浮点滤波器:在DFD设计工具包选择Multistage Decimation Filter

图1、DFD构造多级降采样浮点滤波器

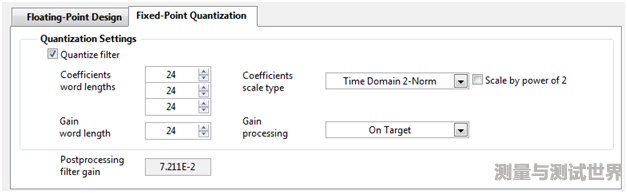

2、 多级降采样定点滤波器设计

图2、浮点滤波器量化构造定点滤波器

3、 多级降采样定点滤波器FPGA实现

关键词:

FPGA感性元件电阻测

评论