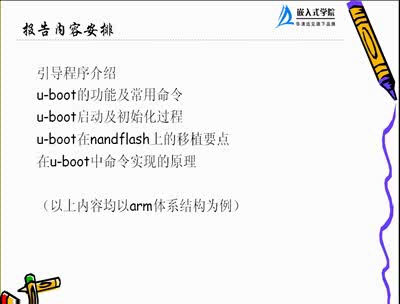

u-boot-在2440上的移植详解(一)

#gedit cpu/arm920t/start.S

本文引用地址:https://www.eepw.com.cn/article/201612/340975.htm#if defined(CONFIG_S3C2400) || defined(CONFIG_S3C2410) || defined(CONFIG_S3C2440)

/* turn off the watchdog */

# if defined(CONFIG_S3C2400)

# define pWTCON 0x15300000

# define INTMSK 0x14400008 /* Interupt-Controller base addresses */

# define CLKDIVN 0x14800014 /* clock divisor register */

#else //下面2410和2440的寄存器地址是一致的

# define pWTCON 0x53000000

# define INTMSK 0x4A000008 /* Interupt-Controller base addresses */

# define INTSUBMSK 0x4A00001C

# define CLKDIVN 0x4C000014 /* clock divisor register */

# endif

ldr r0, =pWTCON

mov r1, #0x0

str r1, [r0]

/*

* mask all IRQs by setting all bits in the INTMR - default

*/

mov r1, #0xffffffff

ldr r0, =INTMSK

str r1, [r0]

# if defined(CONFIG_S3C2410)

ldr r1, =0x3ff

ldr r0, =INTSUBMSK

str r1, [r0]

# endif

# if defined(CONFIG_S3C2440)//添加s3c2440的中断禁止部分

ldr r1, =0x7fff //根据2440芯片手册,INTSUBMSK寄存器有15位可用

ldr r0, =INTSUBMSK

str r1, [r0]

# endif

# if defined(CONFIG_S3C2440) //添加s3c2440的时钟部分

#define MPLLCON 0x4C000004 //系统主频配置寄存器基地址

#define UPLLCON 0x4C000008 //USB时钟频率配置寄存器基地址

ldr r0, =CLKDIVN //设置分频系数FCLK:HCLK:PCLK = 1:4:8

mov r1, #5

str r1, [r0]

ldr r0, =MPLLCON //设置系统主频为405MHz

ldr r1, =0x7F021 //这个值参考芯片手册“PLL VALUE SELECTION TABLE”部分

str r1, [r0]

ldr r0, =UPLLCON //设置USB时钟频率为48MHz

ldr r1, =0x38022 //这个值参考芯片手册“PLL VALUE SELECTION TABLE”部分

str r1, [r0]

# else //其他开发板的时钟部分,这里就不用管了,我们现在是做2440的

/* FCLK:HCLK:PCLK = 1:2:4 */

/* default FCLK is 120 MHz ! */

ldr r0, =CLKDIVN

mov r1, #3

str r1, [r0]

# endif

#endif /* CONFIG_S3C2400 || CONFIG_S3C2410 || CONFIG_S3C2440 */

S3C2440的时钟部分除了在start.S中添加外,还要分别在board/samsung/my2440/my2440.c和cpu/arm920t/s3c24x0/speed.c中修改或添加部分代码,如下:

#gedit board/samsung/my2440/my2440.c //设置主频和USB时钟频率参数与start.S中的一致

#define FCLK_SPEED 2 //设置默认等于2,即下面红色代码部分有效

#if FCLK_SPEED==0 /* Fout = 203MHz, Fin = 12MHz for Audio */

#define M_MDIV 0xC3

#define M_PDIV 0x4

#define M_SDIV 0x1

#elif FCLK_SPEED==1 /* Fout = 202.8MHz */

#define M_MDIV 0xA1

#define M_PDIV 0x3

#define M_SDIV 0x1

#elif FCLK_SPEED==2 /* Fout = 405MHz */

#define M_MDIV 0x7F //这三个值根据S3C2440芯片手册“PLL VALUE SELECTION TABLE”部分进行设置

#define M_PDIV 0x2

#define M_SDIV 0x1

#endif

#define USB_CLOCK 2 //设置默认等于2,即下面红色代码部分有效

#if USB_CLOCK==0

#define U_M_MDIV 0xA1

#define U_M_PDIV 0x3

#define U_M_SDIV 0x1

#elif USB_CLOCK==1

#define U_M_MDIV 0x48

#define U_M_PDIV 0x3

#define U_M_SDIV 0x2

#elif USB_CLOCK==2 /* Fout = 48MHz */

#define U_M_MDIV 0x38 //这三个值根据S3C2440芯片手册“PLL VALUE SELECTION TABLE”部分进行设置

#define U_M_PDIV 0x2

#define U_M_SDIV 0x2

#endif

#gedit cpu/arm920t/s3c24x0/speed.c //根据设置的分频系数FCLK:HCLK:PCLK = 1:4:8修改获取时钟频率的函数

static ulong get_PLLCLK(int pllreg)

{

S3C24X0_CLOCK_POWER * const clk_power = S3C24X0_GetBase_CLOCK_POWER();

ulong r, m, p, s;

if (pllreg == MPLL)

r = clk_power->MPLLCON;

else if (pllreg == UPLL)

r = clk_power->UPLLCON;

else

hang();

m = ((r & 0xFF000) >> 12) + 8;

p = ((r & 0x003F0) >> 4) + 2;

s = r & 0x3;

#if defined(CONFIG_S3C2440)

if(pllreg == MPLL)

{ //参考S3C2440芯片手册上的公式:PLL=(2 * m * Fin)/(p * 2s)

return((CONFIG_SYS_CLK_FREQ * m * 2) / (p << s));

}

#endif

return((CONFIG_SYS_CLK_FREQ * m) / (p << s));

}

/* return HCLK frequency */

ulong get_HCLK(void)

{

S3C24X0_CLOCK_POWER * const clk_power = S3C24X0_GetBase_CLOCK_POWER();

#if defined(CONFIG_S3C2440)

return(get_FCLK()/4);

#endif

return((clk_power->CLKDIVN & 0x2) ? get_FCLK()/2 : get_FCLK());

}

好了!修改完毕后我们再重新编译u-boot,然后再下载到RAM中运行测试。结果终端有输出信息并且出现类似Shell的命令行,这说明这一部分移植完成。示意图如下:

评论