基于FPGA的高速数字下变频系统设计

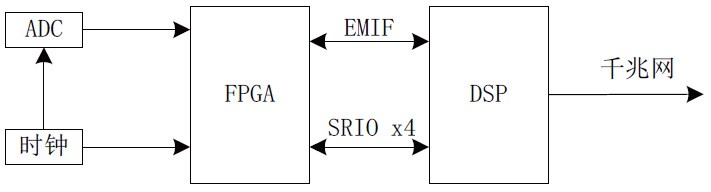

摘要:基于FPGA设计了一高速数字下变频系统,在设计中利用并行NCO和多相滤波相结合的方法有效的降低了数据的速率,以适合数字信号处理器件的工作频率。为了进一步提高系统的整体运行速度,在设计中大量的使用了FPGA中的硬核资源DSP48。Xilinx ISE14.4分析报告显示,电路工作速度可达360MHz。最后给出了在Matlab和ModelSim中仿真的结果,验证了各个模块以及整个系统的正确性。

本文引用地址:https://www.eepw.com.cn/article/201610/308189.htm数字下变频(Digital Down Conversion,DDC)是软件无线电系统的关键模块之一,其可将高频数据流信号变成易于后端数字信号处理器(Digital Signal Processor,DSP)设备实时处理的低频数据流信号。在数字下变频实现中,随着信号采样率的不断提高,数据率也会相应的提高,但是实际应用中随着数据速率的不断提高,数据处理器件(如FPGA)的处理速度会无法满足要求而不能正常工作,从而带来了数字信号处理的瓶颈问题。本设计就是以多路并行NCO技术为基础,研究了如何在FPGA中用多路并行采样数据的方式来解决数据处理器件无法提供高速率的匹配信号的问题,并给出了高速DDC实现的架构和仿真结果。

1 数字下变频基本原理

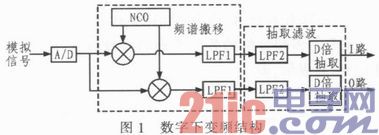

数字下变频主要由频谱搬移和抽取两部分组成,如图1所示,其中频谱搬移包含数控振荡器(Numerically Controlled Oscillators,NCO)、乘法器和低通滤波器(LPF,Low Pass Filter);抽取包含抽取滤波器(LPF2)和D倍的抽取,LPF2是为了限制信号的频谱,以免抽取后发生混叠。

模拟信号经过A/D转换后分成两路信号,一路信号和NCO输出的正弦信号相乘(同相分量),一路和NCO输出的余弦信号相乘(正交分量),之后经过低通滤波器(LPF1)将高频分量滤除,然后信号经过抽取滤波以降低速率,最终输出的两路信号就可以送往后续的数字信号处理器中做进一步的处理。

2 高速DDC系统设计

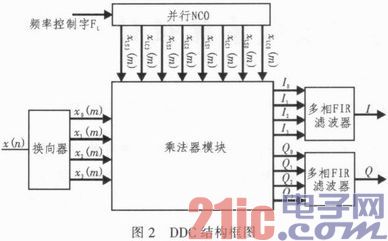

文中设计了一种基于并行NCO的高速DDC,可大大降低对FPGA处理速度的要求,其实现如图2所示,该系统主要由换向器、并行NCO、乘法器模块和两个多相FIR滤波器组成。换向器右侧的所有电路都是工作在Fs/4的时钟频率上,换向器将速率为Fs,16 bit的数据变成4路Fs/4,16 bit的数据。对于输入速率要求较高的场合(例如,速率超过500M),对于输入接口需要用到Xilinx的硬件原语IDDR。

换向器将一路高速率数据分成四路低速率数据输出,并行NCO的输出频率和起始相位受FL控制,分别输出8路正余弦数据,乘法器模块实现NCO输出数据和四路低速率数据的相乘,输出四路正交分量和四路同相分量,之后将这8路数据送入低通滤波器中进行滤波处理,最后将同相分量和正交分量分别输出。

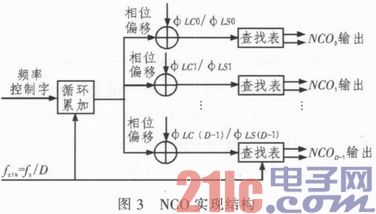

2.1 并行NCO设计

NCO是用来产生载波cosωct和sinωct的部件。

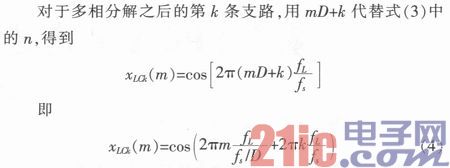

假设NCO的多相分解路数为D,我们可以将x(n)写为如下形式:

由式(1)和式(2)可以看出,经过多相分解之后,数据由原来一路x(n)变为了D个支路,假设x(n)的采样率为fs,那么多相分解后,每个支路的采样率为fs/D,即每一条支路上数据速率变为fs/D,相比原来一路x(n)的情况,数据到来的速率慢了D倍。

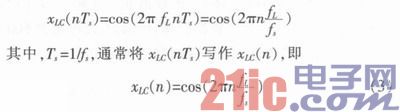

图1中,一路x(n)的采样率为,fs,那么NCO的输出载波相位的速率也必须是fs。假设NCO输出给上面支路的余弦信号为xLC(n),NCO输出给下面支路的正弦信号为xLS(n),假设xLC(n)和xLS(n)的初始相位都为0,其频率都为fL,我们以xLC(n)为例来说明。未采样之前的模拟信号为

xLC(t)=cos(2πfLt)

经过ADC采样,变成数字信号后,用nTs代替上式中的t,得到

由式(4)可以看出,多相分解之后,虽然每个支路的采样率,即数据到来的速率变慢了D倍,但是每个支路NCO输出的频率仍然是fL。我们还需要进一步降低NCO的输出本振信号频率,因为通常情况下,利用NCO产生本振信号需要使用一个主时钟fclk,这个主时钟fclk必须是FPGA可以稳定运行的时钟,其频率不可能太高,而且,实际应用中,NCO输出的本振信号的频率不能超过主时钟fclk。因此无法直接产生所需要的输出频率,但是,我们可以利用三角函数的转换关系,间接的产生。本文所设计的NCO采用如图3所示的结构。

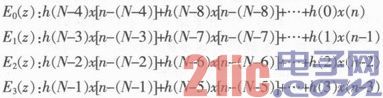

2.2 多相FIR滤波器的设计

低通滤波器主要是用来对信号进行整形滤波并除去信号中的噪声。本设计利用DSP48系列IP核来构成低通滤波器。Xilinx公司提供了两种利用DSP48构建FIR滤波器的方法,分别为Addr Tree和Addr Cascade,考虑到速度问题,本设计使用Addr Tree的设计方法,使用该方法,在Kintex7系列FPGA上其速率超过650 MHz。

假设H(z)对应的冲击响应h(n)的长度为N,且N能被D=4整除(以D=4为例),则四路滤波器输出分别为:

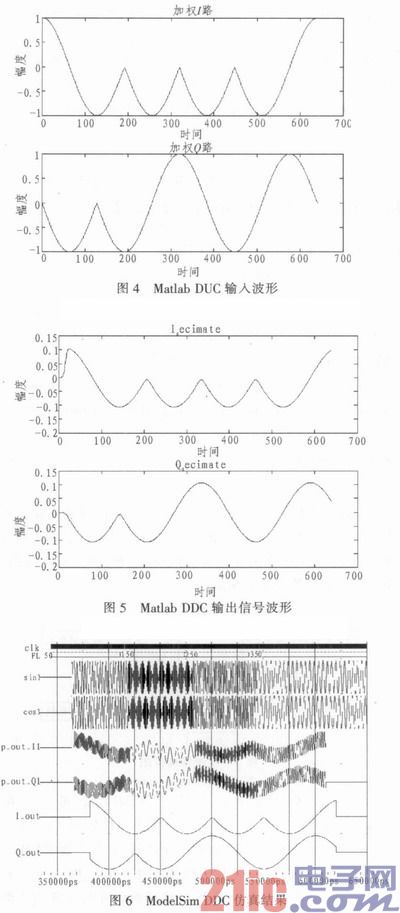

3 仿真及验证

根据系统设计的要求,我们利用Matlab软件对整个的数字下变频系统进行了建模仿真,并使用Verilog硬件描述语言在Xilinx的kintex7系列FPGA上实现了该数字下变频器。为了更好的验证该下变频器的设计,我们利用Matlab建模的上变频系统产生该下变频器的输入激励,如图4所示为上变频系统的输入波形。图5为Matlab建模仿真得到的数字下变频器I、Q两路的输出信号波形。图6为利用Modelsim仿真得到的输出结果,NCO本振频率(CLK)为320 MHz,输入信号跳变频率(FL)分别为50 MHz、150 MHz、250 MHz、350 MHz以及450 MHz,P_out_I1和P_out_Q1分别为混频后四相I、Q信号中的一路,I_out和Q_out为经过多相滤波后最终的输出波形。从Matlab和ModelSim的仿真波形可以很直观的看出我们设计的数字下变频器与理论相符,输出结果正确,达到了预期的设计目的。

4 结论

在设计数字下变频n系统中,提高处理速度是很关键的一部分,本设计首先利用多相结构,将数据分为D路,把每一路的数据速率降成原来的D分之一。在设计低通滤波器和乘法器模块时充分利用了Kintex7上的硬核资源DSP 48,大幅度的提高了电路的处理速度。利用Xilinx的ISEl4.4工具进行综合、布局、布线后的时序报告显示,该电路最高工作速度可达360 MHz,充分显现了此设计的速度优势。由于该数字下变频器是基于FPGA实现的,且具有很高的工作速度,可用它来代替大多数的专用数字下变频芯片,它能够满足大多数通信系统中接收机对数字下变频器处理速度、处理带宽以及滤波性能的要求,可广泛应用于数据采集、软件无线电等领域中,具有较高的实用价值。

评论