ARM的A/R/M设计目标:适合的处理器来执行对应的任务

摘要:ARM认为应该使用适合的处理器来执行对应的任务。本文介绍了每个不同的处理器如何体现这一设计理念。

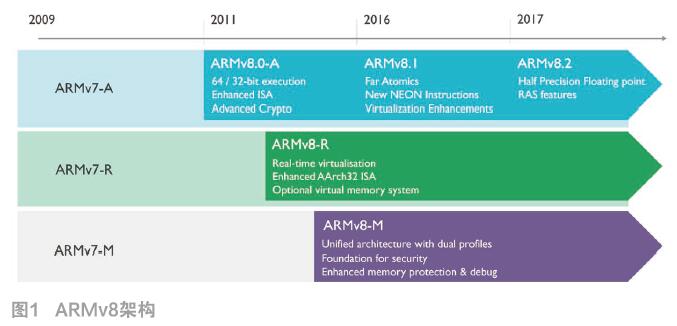

本文引用地址:https://www.eepw.com.cn/article/201607/294692.htmARM处理器现在分成了三个系列(如图1),从家族来讲是A系列、R系列和M系列。A系列主要是面向应用的处理器,R面向实时性处理器,M主要是面向微控制器。在ARM的架构里,每个系列都有独特的特征。针对这些独特的特征,每个系列里都推出了独特的处理器。

ARM现有的这些架构现在都有ARMv8架构了(图1)。针对ARMv8-A,公司在2013年已经推出了Cortex-A57和Cortex-A53。公司也在不断地扩展ARMv8-A指令架构,推出了ARMv8.1和ARMv8.2。ARMv8.1我们有Far Atomics,NEON指令,以及对于虚拟化的增强。而ARMv8.2支持半精度浮点(Half Precision Floating point)以及针对一些服务器的RAS 特征。

ARM在两年前(2014年)发布了ARMv8-R架构,增加了实时的虚拟化,还有增强的AArch32 ISA,以及可选的虚拟内存系统。同时,ARM也推出了ARMv8-M指令集,并有相应的处理器。

每个系列都有独特的功能以及特性(图2)。Cortex-A支持Linux/Rich OS, 32位/64位的ARM指令集,在软件上支持软件中断管理。在存储方面,支持多级缓存。在安全性方面,提供ASIL B级的支持。

对Cortex-R目前有支持MMU的,所以它也可以支持Rich OS。同样我们也可以选择支持MPU的操作系统,在Cortex-R上我们只有32位ARM指令集和Thumb指令集,这主要是专门针对嵌入式市场做的优化。在终端,ARM有专门的软件管理,还有一个Cache和TCM以及安全性方面支持ASIL D。

Cortex-M系列主要针对超低功耗以及最小面积进行设计的,所以目前我们是支持实时性的操作系统RTOS,目前支持32位Thumb的指令集。在终端这方面支持硬件中断管理,终端处理的速度可以是非常快的。在Cache和TCM这方面一般是用Cortex-M7来进行支持,在安全性方面,我们支持到 ASIL-D。

不同的处理器可处理不同的应用(图3)。例如,在可穿戴方面,主要用Cortex-A和Cortex-M。存储方面是Cortex-R和Cortex-M。在ADAS方面有Cortex-A和Cortex-R,由于ADAS对安全性要求特别高,所以针对Cortex-R,ARM做了特别的优化,提供了一些function package(功能包)。在ADAS这边,还有一些高性能的,可以用Cortex-A进行处理。在移动消费市场,Cortex-A、Cortex-R和Cortex-M都有应用,A来做应用处理器,R主要是做基带,Cortex-M可能会用于sensor hub(传感器中枢)的芯片领域。

接下来将分别介绍这几大系列的处理器及一些热门话题。

Cortex-A关注应用

Cortex-A架构里有非常丰富的指令集架构,包含整数的指令集架构以及浮点运算的指令集架构。可以支持到SIMD多数据的运算,在NEON单元里面提供支持。

Cortex-A里有AArch32的指令集,主要是向后兼容ARMv7-A架构。

在ARMv8-A里面,AArch64是2011年推出的,由ARM64位架构来实现的,当时是有Cortex-A57以及Cortex-A53。这样的指令集使访问地址大大增加了,超过了4GB的内存访问空间,也有更多的存储器可以让我们的编辑器进行使用。我们针对指令集也是专门进行了优化,主要是面向功耗效率这方面。

在微架构上,我们可以有多种实现。可以实现超高能效比的处理器,适用于可穿戴市场,也可以实现非常高性能的处理器,实现乱序,达到几GHz。这样的处理器可以应用在很高性能的市场,比如服务器市场。所有这些处理器都可以支持内存一致性的系统,这样我们可以从multi-Cluster的设计里面通过内存一致性让系统来进行支持。

以Cortex-A35为例(图4),Cortex-A35是Cortex-A系列里面向超低功耗、可穿戴市场,以及中低端手机移动市场的处理器。它的设计相对比较简单,指令集都做得相对面向能效优化方向,它主要是按需完成主要的流水线。在这样一个处理器里,也是做成多核处理器的。Cortex-A35在总线方面可以支持AMBA4 ACE总线,也可以支持最新的AMBA5 CHI总线。这样就可以在一个Cluster里面最多实现4个核,也可以实现多个Cluster。

ARM最近也发布了Cortex-A73处理器。它和以前的指令集完全兼容,也和Cortex-A53和Cortex-A35做了很好的配合。Cortex-A73在架构上是做了很大的提升,它可以进行乱序执行的,也是完全可以跟Cortex-A35完全兼容。

在总线上,Cortex-A73也是支持128-bit的AMBA4 AXI4的总线,在Cache配置方面,可以支持不同的配置。

Cortex-A73的热门话题

*Cortex-A73相比Cortex-A72,性能方面有很大提升。那么Cortex-A72设计成二路是基于什么样的考虑?

其实从Cortex-A72学习它的架构,去做了优化,从三路到两路,实现了上文提到的内存系统上的优化,在跳转预测上的优化,各种这方面的优化使得我们能够把Cortex-A72从三路瘦身到两路,同时提升它的功效性能。

设计成三路主要是为了性能,因为三路其实是很强大的,当时Cortex-A72也是性能最好的。ARM当初设计Cortex-A72的时候,就是为了大幅度提升它的性能,我们也可以看到相较以前有很大的性能提升。但是设计Cortex-A73的时候,提升性能不是主要目的,不过我们还是看到它相较Cortex-A72在性能上还是有提升的,但是更主要的是集中提升它的功耗的效率,所以我们能够对它进行瘦身。

* Cortex-A73是10nm,Cortex-A72是16nm,性能提升了30%,功耗降低了30%。这个30%的提升中是不是10%~15%是因为架构的提升,还有20%左右是来自于工艺的提升?

其实,在同样16nm工艺情况下的比较,在功耗效率方面,Cortex-A73相较Cortex-A72能够提升20%。10nm工艺的Cortex-A73相较16nm工艺的Cortex-A72有30%的提升,所以其中工艺的提升是10%,架构是20%。

在性能方面,从微架构上讲,我们提升了10%,但是我们为什么说提升了30%?因为在可持续的峰值性能上,在有限的功耗和散热的约束条件下,我们可以提升得更多,因为它的能耗效率会更高,所以额外提高了20%。

* 从16nm到10nm,更多的是面积上的节省,以及性能上的提升?

但是每家在设计的频率上也是不太一样的。举个例子,像海思Kirin做到2.3~2.5MHz,其他家在做Cortex-A73的时候也会有不同的设计,所以说整个性能的提升和客户做的性能、频率可能都不太一样。

本文来源于中国科技期刊《电子产品世界》2016年第7期第30页,欢迎您写论文时引用,并注明出处。

评论