智能手表拉抬移动市场成长

智慧手表市场即将快速攀升至成长高峰,而日益成熟的智慧型手机市场则将逐渐转冷,这是分析师Linley Gwennap在日前举行「Linley行动与穿戴式装置研讨会」(Linley Mobile & Wearables Conference)时所发表的看法。

本文引用地址:https://www.eepw.com.cn/article/201607/294627.htm另一方面,竞争的Ceva与Tensilica则利用这次会议的机会发表最新DSP核心。

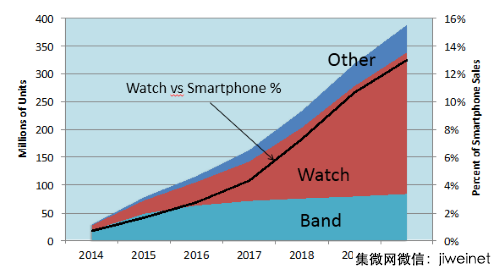

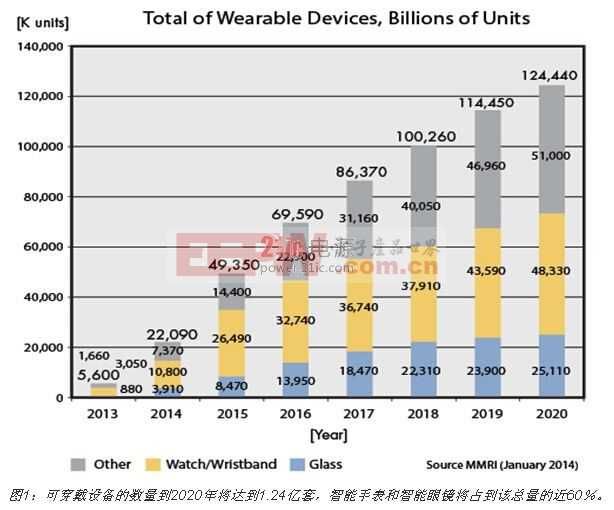

Gwennap预测,智慧手表目前正以38%的复合年成长率(CAGR)成长,预计将在2020年占据大约3.8亿单位的穿戴式装置市场。去年,主导这一市场的是健身手环,其销售量达到4,900万,较销售2,400万单位的智慧手表更高。预测发生变化的原因在于估计苹果(Apple)将在明年大幅升级其智慧手表,及其后在2018年将出现类似的Android智慧手表产品。

「此外,还有智慧型手机的创新。但我们将这场『行动技术』盛会改名为『行动与穿戴式装置』,主要是因为穿戴式装置正是最近最有趣的创新之处,」Gwennap在研讨会开始之前接受采访时表示。

智慧手表将带动穿戴式装置销售成长,并快速成长至大约智慧型手机销售量的13% (来源:Linley Group)

这一预测数字大致相当于Gartner在今年二月的预测,当时,Gartner表示,2016年全球穿戴式装置市场规模上看287亿美元,其中约有115亿美元来自智慧手表。

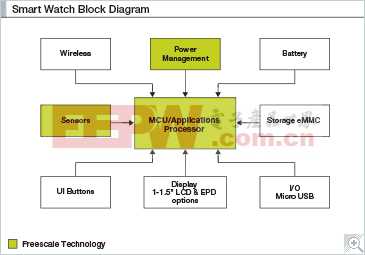

Gwennap呼吁工程师为穿戴式装置开发最佳化晶片,尤其是高阶智慧手表,毕竟,Apple Watch仅有18小时的电池寿命实在令人失望。

「Apple Watch基本上采用了来自iPhone 5智慧型手机等级的SoC,因而只能在狭小空间中挤进小型电池,这就是为什么电池寿命令人不敢恭维之故,」因此,他说:「我希望Apple以及其它公司能为智慧手表设计最佳化晶片。」

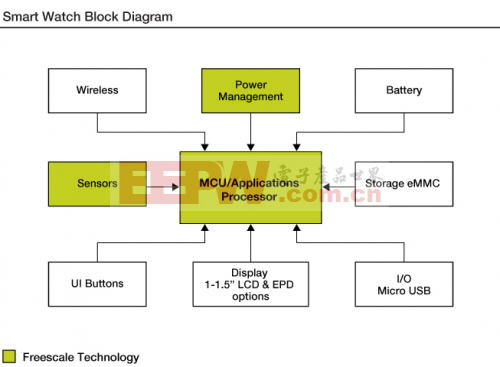

针对低阶的穿戴式装置,目前,50美元的智慧手表以及15-79美元的健身手环主要采用微控制器(MCU)。STM32 MCU用于大部份的Fitbit装置中,而小米手环(Xiaoni Mi Band)则采用Cypress Bluetooth控制器。相对地,价格约300美元或更高的高阶智慧手表则采用基于ARM Cortex-A的SoC、OpenGL 2.0 GPU核心以及大量记忆体。

为行动与穿戴式装置升级DSP

Gwennap估计,在5G风暴袭卷之前的这段宁静时期,智慧型手机的销售成长正逐渐放缓至6.6%的CAGR。然而,这一市场仍然巨大——在2020年以前的手机出货量达19.5亿支,而且广泛的各种手机元件中依然显现创新。

不过,由于成长力道放缓,手机应用处理器供应商开始减少。目前,包括高通(Qualcomm)、联发科(Mediatek)和展讯(Spreadtrum)的商用晶片,以及来自Apple、三星(Samsung)与华为(Huawei)的自家晶片,大约就占据了98%的市场。此外,三星与华为如今也开始设计自家的手机基频晶片。

在最新的高阶手机中,在快取一致性互连(cache-coherent interconnect)架构上使用CPU、GPU和DSP核心的异质丛集,就像使用数十颗GPU核心一样快速蔓延。工程师「能尽量进行卸载,因为CPU是最耗电的元件之一,而以其他元件取而代之可能更省电,」Gwennap说。

针对手机基频晶片,当今的高阶手机以3倍载波聚合(CA)实现LTE Category 9/10,带来高达450Mbits/s的幵载速率。他并补充说,LTE手机目前所有的新手机中约占39%,而营收约占58%,预计到了2018年可望占据智慧型手机营收的半壁江山。

包括华为、联想(Lenovo)、小米、宇龙(Yulong)和中兴(ZTE)等中国前几大的手机供应商,正不断扩展在全球智慧型手机市场的版图(来源:Linley Group)

在此研讨会中,Cadence宣布, Tensilica Fusion G3 DSP核心瞄准了诸多应用。该核心可支援固定、精度与双精度向量浮点运算。

而其竞争对手——Ceva,则推出了尺寸更小、更节能的Ceva-X2 DSP,以取代X4。它针对高阶手机数据机的实体层控制处理,并为低阶物联网(IoT)网路(如ZigBee)处理PHY与MAC作业。

相较于X4,X2采用了「半乘法器(4 vs 8)、较少的记忆体频宽(128位元vs 256位元)、64 vs 128位元的SIMD定点运算作业,以及至多2 vs 4的浮点运算作业,」另一家市调公司Forward Concepts首席市场分析师Will Strauss表示,「很显然地,Ceva了解到X4对于有些应用来说太高档了,而X2能提供较X4更小的晶片尺寸以及更低功耗。」

具体来说,相较于X4,X2提供更小约30%-65%的晶片尺寸,以及更高10%-25%的功率效率。

从历史上来看,尽管华为/海思(HiSilicon)与英特尔(Intel)在其4G数据机中采用了Tensilica,但Strauss指出,Cadence Tensilica DSP持续领先音讯晶片市场。整体来看,在广大的手机市场,Ceva持续于3G与4G数据机领域占主导位置。

然而,Linley Group资深分析师Mike Demler表示,Cadence和Ceca推出的新款核心并不至于直接竞争。

「Ceva的核心是一款PHY控制器,主要用于LTE-Advanced数据机与载波聚合…Ceva在此领域更有优势,而Cadence近来并未着眼于像LTE-Advanced、5G等高性能的数据机应用,」Demler表示。

相形之下,Cadence的Fusion G3「是几个不同DSP的组合,可用于包括音讯、成像与通讯等适于IoT装置的应用领域,」Demler并补说:「Ceva也为这些不同的功能供了IP,但并未整合其于单一封装中。」

评论